2006~2010数字逻辑试卷及答案要点

- 格式:doc

- 大小:4.08 MB

- 文档页数:36

一、填空题(20分,每空2分)1. (2010)D =()B = ()H = ()8421BCD答案:(111 1101 1010)B= (7DA)H = (0010 0000 0001 0000)8421BCD2. 仓库门上装了两把暗锁,A、B两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。

这种逻辑关系为。

答案:与逻辑3. 逻辑函数式F=AB+AC的对偶式为,最小项表达式为∑F( )。

=m答案:)F D++=∑A)((CABF(5,6,7)=m2.逻辑函数D''''+=的最简与或式++++'CF'CDACABAABCABDCD是。

答案:'DA+4. 从结构上看,时序逻辑电路的基本单元是。

答案:触发器5. JK触发器特征方程为。

答案:Q'+JQ'K6.A/D转换的一般步骤为:取样,保持,,编码。

答案:量化二、选择题(20分,每题2分)1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为()位。

A) 6 B) 7 C) 8 D) 51答案:B2. 在函数F=AB+CD的真值表中,F=1的状态有()个。

A) 2 B) 4 C) 6 D) 7答案:D3. 为实现“线与”逻辑功能,应选用()。

A) 与非门B) 与门C) 集电极开路(OC)门D) 三态门答案:C4. 图1所示逻辑电路为( )。

A) “与非”门B) “与”门C)“或”门D) “或非”门图1答案:A5. 在下列逻辑部件中,属于组合逻辑电路的是( )。

A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。

图2 A) 上升沿D 触发器 B) 下降沿D 触发器 C) 下降沿T 触发器 D) 上升沿T 触发器答案:D7. 寄存器要存放n 位二进制数码时,需要( )个触发器。

一、填空题 (20分,每空2分)1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。

这种逻辑关系为 。

答案:与逻辑3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。

答案:))((C A B A F D ++= ∑=m F (5,6,7)2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。

答案:'D A +4. 从结构上看,时序逻辑电路的基本单元是 。

答案:触发器5. JK 触发器特征方程为 。

答案:Q K JQ ''+6.A/D 转换的一般步骤为:取样,保持, ,编码。

答案:量化二、选择题 (20分,每题2分)1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。

A) 6 B) 7 C) 8 D) 51 答案:B2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。

A) 2 B) 4 C) 6 D) 7 答案:D3. 为实现“线与”逻辑功能,应选用( )。

A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C4. 图1所示逻辑电路为( )。

A) “与非”门B) “与”门C)“或”门 D) “或非”门图1答案:A5. 在下列逻辑部件中,属于组合逻辑电路的是( )。

A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。

武汉大学计算机学院2006~2007学年第二学期2006级《数字逻辑》期未考试试卷A卷学号班级姓名成绩一、填空(每空1分,共14分)1、(21.5)10=()2=()8=()162、若0.1101x=-,则[]x补=()3、十进制数809对应的8421BCD码是()4、若采用奇校验,当信息位为10011时,校验位应是()5、数字逻辑电路分为()和()两大类6、电平异步时序逻辑电路的描述工具有()、()、()7、函数()()=+⋅+的反函数是()F A B C D8、与非门扇出系数N O的含义是()9、若要消除函数(,,)=+对应的逻辑电路可能存在的险象,则应增加F A B C AB AC的冗余项是()二、选择题(每空2分,共16分)从下列各题的四个答案中,选出一个正确答案,并将其代号填入括号内1、数字系统采用()可以将减法运算转化为加法运算A.原码B.余3码C.Gray码D.补码2、欲使J-K触发器在CP脉冲作用下的次态与现态相反,JK的取值应为()A.00 B.01 C.10 D.113、对完全确定原始状态表中的6个状态,A、B、C、D、E、F进行比简,若有(A,B),(D、E)等效,则最简状态表中只有()个状态A.2 B.4 C.5 D.64、下列集成电路芯片中,()属于组合逻辑电路A.计数器74290 B.寄存器74194C.三一八译码器74138 D.集成定时器5G5555、设计一个20进制同步计数器,至少需要()个触发器A.4 B.5 C.6 D.206、用5G555构成的多谐振荡器有()A.两个稳态B.两个暂稳态C .一个稳态,一个暂稳态D .既没有稳态,也没有暂稳态 7、可编程逻辑阵列PLA 的与、或陈列是( )A .与阵列可编程、或阵列可编程B .与阵列不可编程、或阵列可编程C .与阵列可编程、或阵列不可编程D .与阵列不可编程、或阵列不可编程 8、最大项和最小项的关系是( )A .i i m M =B .i i m M =C .1i i m M ⋅=D .无关系 三、逻辑函数化简(6分)把(,,,)(0,1,5,14,15)(4,7,10,11,12)F A B C D m d =∑+∑化成最简与—或式 四、分析题(每小题12分,共24分)1、分析图1所示组合逻辑电路① 写出输出函数表达式 ② 列出真值表 ③ 说明电路功能2、分析图2所示脉冲异步时序逻辑电路① 写出输出函数和激励函数表达式 ② 列出次态真值表,作出状态表和状态图 ③ 说明电路功能④ 设初态2100y y =,作出x 输入4个异步脉冲后的状态y 2y 1和输出z 的波形图。

《数字逻辑》期末考试 A 卷参考答案

一、判断题:下面描述正确的打‘√’,错误的打‘×’ (每小题1 分,共 10 分)

1、为了表示 104 个信息,需 7位二进制编码 [√ ]

2、 BCD码能表示0 至 15 之间的任意整数[× ]

3、余 3码是有权码[× ]

4、 2421 码是无权码 [ × ]

5、二值数字逻辑中变量只能取值0 和 1,且表示数的大小 [ × ]

6、计算机主机与鼠标是并行通信[× ]

7、计算机主机与键盘是串行通信[√ ]

8、占空比等于脉冲宽度除于周期[√ ]

9、上升时间和下降时间越长,器件速度越慢

10、卡诺图可用来化简任意个变量的逻辑表达式[√]

[×]

二、写出图中电路的逻辑函数表达式。

(每小题 5 分,共10 分)

1、 F=A B

2、 F=AB CD

三、选择题:(多选题,多选或少选不得分,每小题 2 分,共 20 分)。

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

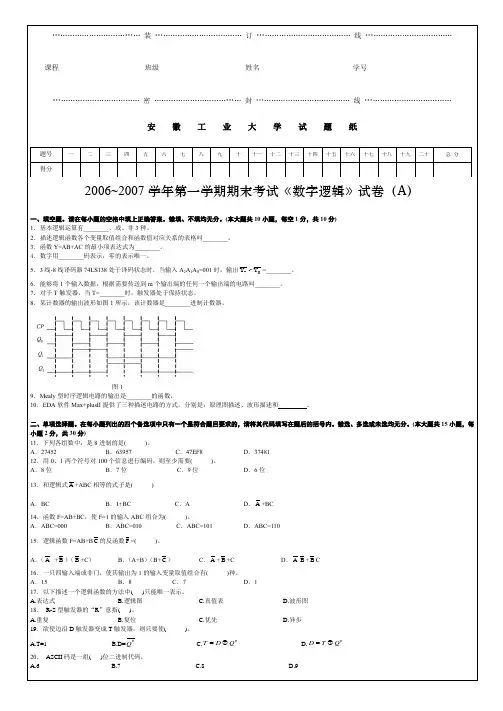

……………………………… 装 ……………………………… 订 ………………………………… 线 ………………………………课程________________________班级________________________姓名__________________________学号________________________……………………………… 密 ……………………………… 封 ………………………………… 线 ………………………………安 徽 工 业 大 学 试 题 纸2006~2007学年第一学期期末考试《数字逻辑》试卷(A )一、填空题。

请在每小题的空格中填上正确答案。

错填、不填均无分。

(本大题共10小题,每空1分,共10分) 1.基本逻辑运算有________、或、非3种。

2.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫________。

3.函数Y=AB+AC 的最小项表达式为________。

4.数字用________码表示,零的表示唯一。

5.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y =________。

6.能够将1个输入数据,根据需要传送到m 个输出端的任何一个输出端的电路叫________。

7.对于T 触发器,当T=________时,触发器处于保持状态。

8.某计数器的输出波形如图1所示,该计数器是________进制计数器。

图19.Mealy 型时序逻辑电路的输出是________的函数。

10.EDA 软件Max+plusII 提供了三种描述电路的方式,分别是:原理图描述、波形描述和 。

二、单项选择题。

在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

(本大题共15小题,每小题2分,共30分)11.下列各组数中,是8进制的是( )。

A .27452 B .63957 C .47EF8 D .37481 12.用0、1两个符号对100个信息进行编码,则至少需要( )。

数字逻辑总复习题答案一、选择题1. 以下哪个选项是数字逻辑中的基本逻辑运算?A. 与运算B. 或运算C. 非运算D. 所有以上选项答案:D2. 在数字逻辑中,一个变量的真值表可以有多少行?A. 1B. 2C. 4D. 8答案:C3. 逻辑门电路中的输出状态取决于输入状态,以下哪个描述是正确的?A. 输出状态与输入状态相同B. 输出状态与输入状态相反C. 输出状态由输入状态的组合决定D. 输出状态与输入状态无关答案:C二、填空题1. 在数字逻辑中,逻辑或运算的符号通常表示为______。

答案:∨2. 一个三变量的逻辑函数,其真值表最多可以有______种不同的输出组合。

答案:83. 逻辑门电路中的与非门(NAND)可以看作是______和______的组合。

答案:与门,非门三、简答题1. 请简述数字逻辑中的布尔代数基本定理。

答案:布尔代数的基本定理包括交换律、结合律、分配律、幂等律、补余律等,这些定理是构建和简化逻辑表达式的基础。

2. 描述逻辑门电路中的异或(XOR)门的功能。

答案:异或门的输出仅在输入状态中奇数个为真时为真,其余情况下输出为假。

四、计算题1. 给定逻辑函数F(A, B, C) = Σ(0, 1, 2, 7),请写出其对应的真值表。

答案:| A | B | C | F ||||||| 0 | 0 | 0 | 0 || 0 | 0 | 1 | 1 || 0 | 1 | 0 | 1 || 0 | 1 | 1 | 0 || 1 | 0 | 0 | 1 || 1 | 0 | 1 | 0 || 1 | 1 | 0 | 0 || 1 | 1 | 1 | 1 |2. 利用卡诺图化简逻辑函数F(A, B, C, D) = Σ(0, 1, 2, 3, 8, 9,10, 11, 12, 13, 14, 15)。

答案:F(A, B, C, D) = A'C + BD请注意,以上内容仅为示例,实际的试题和答案应根据具体的课程内容和教学要求来制定。

------------------------------------------------------------精品文档--------------------------------------------------------期末考试试题(答案)装考试时间:110 分钟考试科目:数字逻辑电路试卷类别:3卷级班______________系学院XXXX毛学号姓名订一二三题号四总分得分线一、选择题(每小题2分,共20分)评卷人得分内1.八进制(273)中,它的第三位数2 的位权为___B___。

8 A.(128) B.(64) C.(256) D.(8) 1010 1010与它功能相等的函数表达式2. 已知逻辑表达式F?AB?AC?BC,_____B____。

请F?AB?CAB?F.A.BF?AB?AC F?AB?BC..D C3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

勿A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。

答题A.与关系B.异或关系C.同或关系D.无法判断5.连续异或1985个1的结果是____B_____。

A.0B.1 C.不确定D.逻辑概念错误页8 共页1 第卷答案3 数字逻辑电路与逻辑函数功能相等的表达式为___C_____。

6. DF?A?B?C?DC?F?A?B?D?C?F?A?B.AB.D.C.D?F?AB?CDBCF?A为高阻态的逻辑时,FC=0时,F=;C=17.下列所给三态门中,能实现AB ____A______。

功能的是A A &BFFB?C CEN ENB AA A &&F F B B ??C C EN END C的频率为Q脉冲的频率为100KHZ,则输出8. 如图所示电路,若输入CP 。

_____D_____200KHz . 500KHz B A.50KHz . 100KHz D C.Q DCPC Q_____A_____。

数字逻辑技术试卷-第2章一、填空题1.逻辑电路中,电平接近0时称为低电平,电平接近V CC或V DD时称为高电平。

2.数字电路中最基本的逻辑门有与、或和非门。

常用的复合逻辑门有与非门、或非门、与或非门、异或门和同或门。

3.图腾结构的TTL集成电路中,多发射极三极管可完成与门逻辑功能。

4.CMOS反相器是两个增强型的MOS管组成,且其中一个是N沟道管,另外一个是P沟道管,由于两管特性对称,所以称为互补对称CMOS反相器。

5.TTL与非门输出高电平U OH的典型值是 3.6V,低电平U OL的典型值是0.3V。

6.普通的TTL与非门具有图腾结构,输出只有高电平和低电平两种状态;TTL三态与非门除了具有1态和0态,还有第三种状态高阻态,三态门可以实现总线结构。

7.集电极开路的TTL与非门又称为OC门,几个OC门的输出可以并接在一起,实现线与逻辑功能。

8.TTL集成电路和CMOS集成电路相比较,其中TTL集成电路的带负载能力较强,而CMOS集成电路的抗干扰能力较强。

9.用三态门构成总线连接时,依靠使能端的控制作用,可以实现总线的共享而不至于引起总线冲突。

10. TTL集成与门多余的输入端可与有用端并联或接高电平;TTL集成或门多余的输入端可与有用端并联或接低电平。

二、判断下列说法的正误1.所有的集成逻辑门,其输入端子均为两个或两个以上。

(错)2.根据逻辑功能可知,异或门的反是同或门。

(对)3.具有图腾结构的TTL与非门可以实现“线与”逻辑功能。

(错)4.基本逻辑门电路是数字逻辑电路中的基本单元。

(对)5.TTL和CMOS两种集成电路与非门,其闲置输入端都可以悬空处理。

(错)6.74LS系列产品是TTL集成电路的主流产品,应用最广泛。

(对)7.74LS系列集成电路属于TTL型,CC4000系列集成电路属于CMOS型。

(对)8.与门多余的输出端可与有用端并联或接低电平。

(错)9.OC门不仅能够实现“总线”结构,还可构成与或非逻辑。

数字逻辑技术试卷-第2章一、填空题1.逻辑电路中,电平接近0时称为低电平,电平接近V CC或V DD时称为高电平。

2.数字电路中最基本的逻辑门有与、或和非门。

常用的复合逻辑门有与非门、或非门、与或非门、异或门和同或门。

3.图腾结构的TTL集成电路中,多发射极三极管可完成与门逻辑功能。

4.CMOS反相器是两个增强型的MOS管组成,且其中一个是N沟道管,另外一个是P沟道管,由于两管特性对称,所以称为互补对称CMOS反相器。

5.TTL与非门输出高电平U OH的典型值是 3.6V,低电平U OL的典型值是0.3V。

6.普通的TTL与非门具有图腾结构,输出只有高电平和低电平两种状态;TTL三态与非门除了具有1态和0态,还有第三种状态高阻态,三态门可以实现总线结构。

7.集电极开路的TTL与非门又称为OC门,几个OC门的输出可以并接在一起,实现线与逻辑功能。

8.TTL集成电路和CMOS集成电路相比较,其中TTL集成电路的带负载能力较强,而CMOS集成电路的抗干扰能力较强。

9.用三态门构成总线连接时,依靠使能端的控制作用,可以实现总线的共享而不至于引起总线冲突。

10. TTL集成与门多余的输入端可与有用端并联或接高电平;TTL集成或门多余的输入端可与有用端并联或接低电平。

二、判断下列说法的正误1.所有的集成逻辑门,其输入端子均为两个或两个以上。

(错)2.根据逻辑功能可知,异或门的反是同或门。

(对)3.具有图腾结构的TTL与非门可以实现“线与”逻辑功能。

(错)4.基本逻辑门电路是数字逻辑电路中的基本单元。

(对)5.TTL和CMOS两种集成电路与非门,其闲置输入端都可以悬空处理。

(错)6.74LS系列产品是TTL集成电路的主流产品,应用最广泛。

(对)7.74LS系列集成电路属于TTL型,CC4000系列集成电路属于CMOS型。

(对)8.与门多余的输出端可与有用端并联或接低电平。

(错)9.OC门不仅能够实现“总线”结构,还可构成与或非逻辑。

t h数字逻辑电路 3卷答案 第 1 页 共 8 页期末考试试题(答案)考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟XXXX 学院 ______________系级班姓名学号 题号一二三四总分得分一、选择题(每小题2分,共20分)1. 八进制(273 2 的位权为___B___。

A .(128)10 C .(256)10 D .(8)102. C B +,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F += C .C A AB F +=D . B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误得分评卷人装 订 线 内 请 勿答 题数字逻辑电路 3卷答案 第 2 页 共 8 页6. 功能相等的表达式为___C_____。

B .D C B A F +++=D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=;C=1时,F 为高阻态的逻AB 辑功能的是____A______。

8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz 9.下列器件中,属于时序部件的是_____A_____。

A . 计数器B . 译码器C . 加法器D .多路选择器装a n t数字逻辑电路 3卷答案 第 3 页 共 8 页10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。

数字逻辑考试题答案及评分标准数字逻辑考试题数字逻辑考试题(一)一、填空(共17分,每空1分) 1. (1011.11)B =( ) D =( )H 2. (16)D =( )8421BCD 码。

3. 三态门的输出有 、 、 三种状态。

6. ABC C B A C AB C B A Y ++=),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(共10分,每题1分)1. DE BC A Y +=的反函数为Y =( )。

A. E D C B A Y +++⋅=B. E D C B A Y +++⋅=C. )(E D C B A Y +++⋅=D. )(E D C B A Y +++⋅= 3. 十进制数25用8421BCD 码表示为( )。

A. 10101 B. 0010 0101 C. 100101 D. 101014. 若用1表示高电平,0表示低电平,则是( )。

A. 正逻辑B. 负逻辑C. 正、负逻辑D. 任意逻辑 5. 下逻辑图的逻辑表达式为( )。

A. AC BC AB Y =B. BC AC AB Y ++=C. BC AC AB Y ++=D. BC AC AB Y = 6. 三态门的逻辑值正确是指它有( )。

A. 1个B. 2个C. 3个D. 4个9. 组合逻辑电路在电路结构上的特点下列不正确的是( )。

A. 在结构上只能由各种门电路组成B. 电路中不包含记忆(存储)元件C. 有输入到输出的通路D. 有输出到输入的反馈回路10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输出07~Y Y 为( )。

电子科技大学二零零六至二零零七学年第1学期期末考试数字逻辑设计 课程考试题 B 卷 ( 120 分钟) 考试形式: 闭卷 考试日期 2007年 月 日课程成绩构成:平时 20 分, 期中 10 分,期末 70 分一、单项选择题,下列每题的四个选项中有一个正确的,请把正确选项的编号填入括号内(每小题2分,共10分)1、已知某符号二进制数的补码为1.0110,则其原码为( B )。

A. 1.0110B. 1.1010C. 1.0101D. – 0.1010 2、将8421BCD 码为01000101的数转换成其十进制描述为( A )。

A. 45 B. 69 C. 37 D. 543、当描述同步时序逻辑电路时,有6个状态的最简状态图需要( C )个触发器。

A. 1 B. 2 C. 3 D. 44、TTL 集成电路的电源电压V CC =( 2 )。

(1)—5V (2) +5V (3) +10V (4) —10V5、设i M 和j M 是n 个变量构成的两个最小项,若j i ≠,则( A )。

A. 0=∙j i M MB. 0=+j i M MC. 1=∙j i M MD. 1=+j i M M二、填空题(每小题2分,共10分)1AC D C B A F )(++=的反函数为))((C A D C B A F +++=。

2、函数))((C A B A F ++=可能会产生险象,可以通过增加冗余项(C B +)的方法消除。

3、函数==∏)7,6,5,4,3,2,1,0(),,(M C B A F 0。

4、若121=⊕⋅⋅⋅⊕⊕n X X X ,则i X =1的个数必须为(奇)数。

5、(53.69)10的余3码表示为1000 0110.1001 1100。

三、判断题,请在下面正确描述的前面打√,在错误描述前面打×(每小题2分,10分)(×)1、CMOS电路的空闲输入端可以悬空,悬空时相当于逻辑“1”。

数字逻辑试卷(B)1.十六进制数的基数是( 18 )。

2.N进制数具有两个特点,一是(逢N进一),二是有( N )个计数符号。

3.(4321)8=( 100011010001 )2=( 8D1)164.(0001 0010 0011)8421BCD=( 0100 )余3BCD5.(1111.11)2=( 15.75 )106.N变量任意两个不同的最小项的乘积为( 0 )。

7.三态门的输出可能出现三种状态:高电平,低电平和(输出高阻态 )。

8.约束项和任意项统称为( 无关项 )。

9.同步RS触发器R和S不能同时为( 1 )。

10.时序电路是由组合电路和( 触发器 )两部分组成的。

二、判断(正确判断划√,否则划×。

每小题1分,本大题10分)1.BCD码只有一种即8421BCD码。

( × )2.正逻辑的与非门也是负逻辑的与非门。

( × )3.每一个最小项只有相对应的一组逻辑变量取值使该最小项的值为1。

√4二进制译码电路输出可以得到输入变量的全体最小项(或最小项相反)。

√5.边沿触发器有效地解决了空翻问题。

( √ )T触发器和D触发器都有两个逻辑功能,所以它们的逻辑功能是相同的。

×7.计数过程的基本特点是单向循环。

( √)8.移位寄存器可以实现数据的串行输入和串行输出。

(√ )9.串行加法运算速度比并行加法器快。

( × )10.单稳态触发器的暂稳态时间仅决定于电路本身的参数。

(√ )三、单项选择1.卡诺图上几个相邻的小方格合并消去2个变量。

( C.4个 )2.逻辑函数的哪种表示方式不是唯一的?( B.表达式)3.挂在同一总线上的三态门任何时候只允许几个门处在工作状态?B.一个4.下列电路哪个不是组合电路?( C.计数器)5.三输入的二进制译码器有几个输出?(C.8个 ) 6.哪种触发器只有一种逻辑功能?( C.T ′触发器) 7.组合电路的输出(A.仅与当时输入有关)8.异步时序电路中各触发器( C.无统一的时钟)9.并行加法器实现两个N 位二进制数的加法需要( A.N 个全加器) 10.下列哪种电路不需要触发信号( B.多谐振荡器 ) 四、逻辑运算(每小题3分,本大题15分)1.连续2000个1异或结果是( 0 )2.若AC AB =,B 是否一定等于C ?( 不一定 )3.用公式法证明C B A C AB B A ⋅⊕=++)(4.用公式法化简A C C B B A F ++=答:ABC C B A A C C B B A A C C B B A +=+++=++))()(( 5.用图形法化简)7,5,2,1,0()15,13,6,4(∑∑+=d m F五、组合电路分析设计(本大题18分) 1. 比较图示两电路的逻辑功能。