软件总体架构图资料

- 格式:doc

- 大小:1.05 MB

- 文档页数:14

作为软件开发者、产品经理、项目经理、售前经理等软件从事者,我们在工作中难免要画很多的架构图,但是很多人对于如何去画架构图其实是很模糊的,有那么多种类型的图,我们究竟该选哪个,用应该怎么画呢?今天让你一文学会画软件架构图。

一、什么是架构图?

架构图就像是一个房子,架构决定房子的布局、朝向、楼层,房子的框架就是我们所说的架构。

架构图就是运用抽象的方法用来描述系统中的实体以及实体之间的关系。

架构图将抽象的架构绘制到一张画布上,主要用于软件程序的设计和系统开发。

架构图灵活、可延展,可以解决许多复杂的工作及问题,将复杂的软件逻辑简单化。

二、架构的类型

架构大致可以分为2类,应用架构图、数据架构图。

2.1、应用架构图

应用架构图是最常用的架构图,也是对整个系统总体业务上的架构,遵循系统开发的原则,从上到下可分为展示层、用户层、应用层、数据层、数据库、运行环境。

如下图所示:

2.3、数据架构图

数据架构图是一套对存储数据的架构逻辑,根据系统数据应用场景,可分为数据应用层、数据存储层、数据处理层、数据来源层。

如下图所示:。

各种软件开发系统架构图案例介绍第一章【荐】共享平台架构图与详细说明1.1.【荐】共享平台逻辑架构设计(逻辑指的是业务逻辑)注:逻辑架构图--主要突出子系统/模块间的业务关系, 这里的逻辑指的是业务逻辑如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.【荐】技术架构设计注:技术架构图--主要突出子系统/模块自身使用的技术和模块接口关联方式如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.【荐】系统整体架构设计(也称为系统总体架构)上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:注:系统整体/总体架构图--主要突出从物理硬件(物理层/基础层)、数据库(数据层)、后台底层(支撑层)、业务逻辑(业务层/应用层)、UI描述(展示层)、系统用户分类(用户层),项目实施与运维管理,标准与规范体系和安全保障体系(贯穿各层的保障系统)一般我们只画大虚框内的部分就行了,外面的是说明与其他系统的对接描述,可以省略综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

各种软件开发系统架构图案例介绍v1.0 可编辑可修改第一章【荐】共享平台架构图与详细说明1.1.【荐】共享平台逻辑架构设计(逻辑指的是业务逻辑)注:逻辑架构图--主要突出子系统/模块间的业务关系, 这里的逻辑指的是业务逻辑如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.【荐】技术架构设计注:技术架构图 --主要突出子系统/模块自身使用的技术和模块接口关联方式如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.【荐】系统整体架构设计(也称为系统总体架构)上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:注:系统整体/总体架构图 --主要突出从物理硬件(物理层/基础层)、数据库(数据层)、后台底层(支撑层)、业务逻辑(业务层/应用层)、UI描述(展示层)、系统用户分类(用户层),项目实施与运维管理,标准与规范体系和安全保障体系(贯穿各层的保障系统)一般我们只画大虚框内的部分就行了,外面的是说明与其他系统的对接描述,可以省略综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

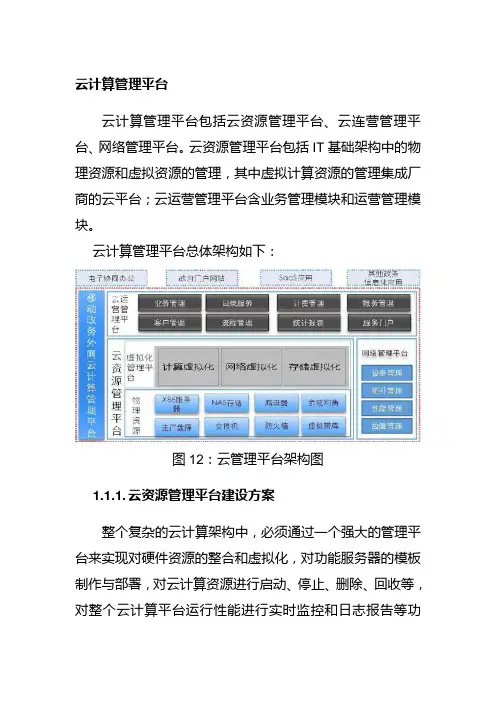

云计算管理平台云计算管理平台包括云资源管理平台、云连营管理平台、网络管理平台。

云资源管理平台包括IT基础架构中的物理资源和虚拟资源的管理,其中虚拟计算资源的管理集成厂商的云平台;云运营管理平台含业务管理模块和运营管理模块。

云计算管理平台总体架构如下:图12:云管理平台架构图1.1.1. 云资源管理平台建设方案整个复杂的云计算架构中,必须通过一个强大的管理平台来实现对硬件资源的整合和虚拟化,对功能服务器的模板制作与部署,对云计算资源进行启动、停止、删除、回收等,对整个云计算平台运行性能进行实时监控和日志报告等功能,同时还实现用户交换接口,用户可以方便地登录到云计算平台,申请各种硬件资源和中间件资源,启动、停止自己功能服务器功能。

这样打破了业务应用对资源的=独占的方式,实现硬件资源和软件资源的统一管理、统一分配、统一部署、统一监控和统一备份。

考虑到XX中的3个区(专用网络区、公共网络区、互联网接入区)之间是通过MPLS VPN相关隔离,为了实现云计算平台对3个区的统一管理,我们建议将宿主机的管理口(统一设置宿主机上某一个单独物理网卡用于云计算管理平台对虚拟机的管理通讯)进行统一VLAN规划,通过此方式可以实现不同分区的虚拟机在同一个资源组中迁移和统一管理。

云资源管理平台主要由以下两个模块组成:云资源管理系统云计算服务Portal。

图13:云资源管理功能模块图1.1.1.1. 云资源管理系统云资源管理系统其通过虚拟化技术和基于策略的自动化管理技术,构成虚拟化资源池,实现对物理资源、虚拟资源的统一管理和分配。

云资源管理系统架构需要实现功能:1、设备管理提供对物理设备的接入和管理功能,包括设备发现展示、配置部署、告警上报等。

2、虚拟适配层提供对不同虚拟层(VMM)的适配、集成能力,如VMware、Xen、KVM、Hyper-V等,对上层屏蔽不同虚拟层差异,提供统一的虚拟化管理接口。

3、云适配层提供对不同云资源的适应能力,实现公有云和私有云资源的统一管理能力。

各种系统架构图和说明1.1.共享平台逻辑架构设计如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.技术架构设计如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.整体架构设计上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

1.3.1.应用层级说明整体应用系统架构设计分为五个基础层级,通过有效的层级结构的划分可以全面展现整体应用系统的设计思路。

智慧政务云数据中心总体架构设计目录第一章、项目总体设计 (3)1.1、项目设计原则 (3)1.1.1、统一建设 (3)1.1.2、相对独立 (3)1.1.3、共建共享 (3)1.1.4、安全可靠 (3)1.2、建设思路 (4)1.2.1、需求驱动 (4)1.2.2、标准先行 (4)1.2.3、围绕数据 (4)1.2.4、逐步扩展 (4)1.3、数据中心总体结构设计 (5)1.3.1、总体逻辑体系结构 (8)1.3.1.1、信息资源体系 (8)1.3.1.2、支撑体系 (9)1.3.1.3、标准规范体系 (9)1.3.1.4、运行管理体系 (10)1.3.1.5、安全保障体系 (10)1.3.2、总体实施结构设计 (10)1.3.2.1、数据中心交换共享平台及信息资源 (11)1.3.2.2、数据接口系统区 (12)1.3.2.3、各部门系统 (12)1.3.2.4、综合应用 (12)1.3.3、总体物理体系结构 (12)第一章、项目总体设计1.1、项目设计原则1.1.1、统一建设数据中心必须统一规范建设。

通过制定统一的数据交换与共享标准,建设统一的数据共享与交换平台和统一的前置机接口系统,可以避免重复投资,降低接口的复杂性,有效实现数据中心与业务部门以及业务部门之间的数据共享与数据交换,消除社会保障系统范围内的“信息孤岛”,实现数据资源的互联互通。

1.1.2、相对独立根据数据中心的功能定位,数据中心的建设和运作必须保持业务系统的相对独立性。

为此采用松散耦合方式,通过在业务部门统一配置接口系统实现数据资源整合。

1.1.3、共建共享一方面建设数据中心的目的是为了实现业务部门之间的数据共享。

另一方面,数据中心的数据来源于各个业务部门,因此数据中心的建设必须依靠各业务部门的积极参与和配合。

1.1.4、安全可靠由于社会保障数据与广大社会保障对象的切身利益密切相关,所以数据中心的安全是非常重要的。

因此,必须要做好系统的安全设计,防范各种安全风险,确保数据中心能够安全可靠的运行。

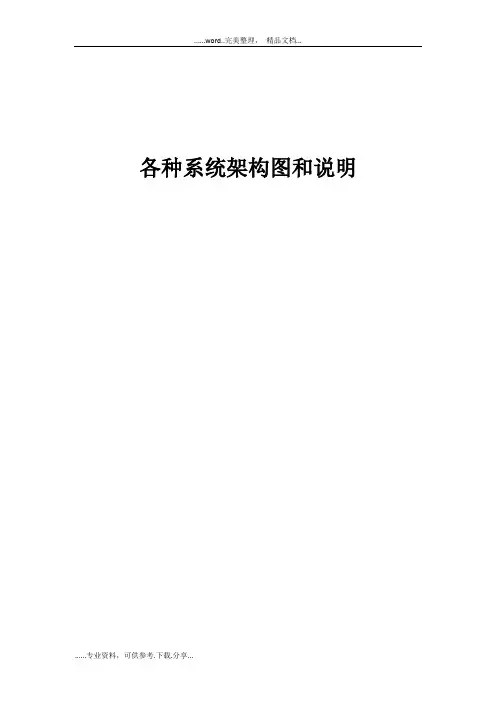

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

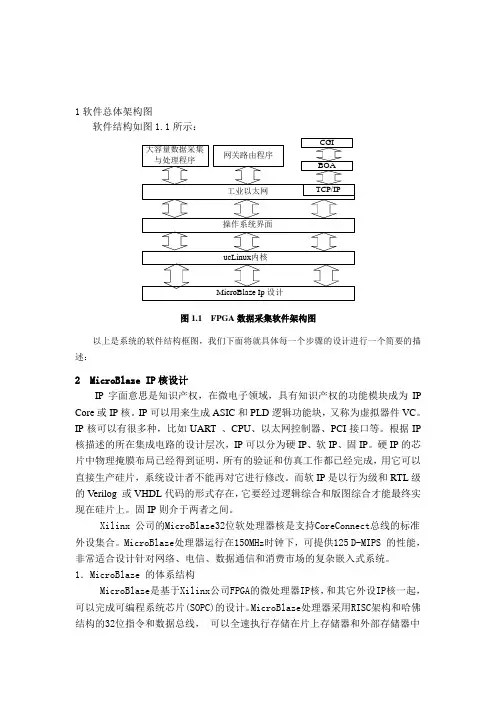

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

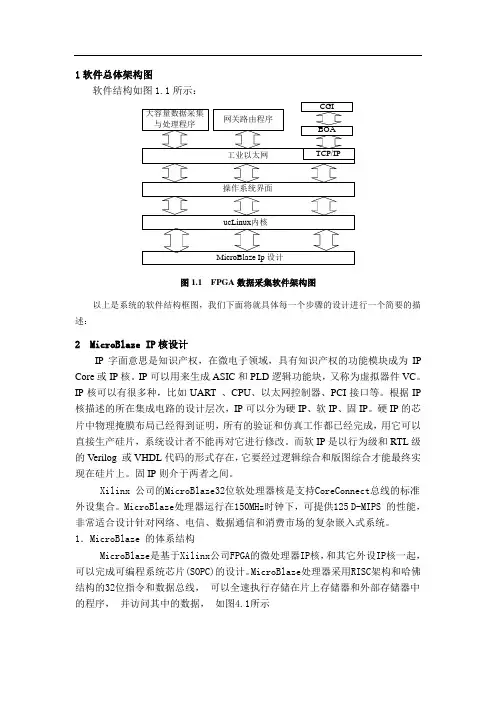

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

软件架构设计文档范本1. 引言软件架构设计文档是软件开发过程中的重要一环,它描述了整个软件系统的结构、组件之间的关系以及核心功能的实现方式。

本文档旨在提供一个范本,帮助开发团队快速准确地编写和组织软件架构设计文档。

2. 背景在本节中,将简要介绍开发的软件项目的背景信息。

包括项目的目标、需求和范围,以及所涉及的技术和平台。

3. 总体设计在这一节中,将描述软件系统的总体设计。

包括系统的层次结构、模块划分以及模块之间的协作关系。

此外,还应该包括系统的核心功能和设计原则。

4. 结构设计在本节中,将详细描述系统的结构设计。

包括每个模块的职责和接口,以及模块之间的依赖关系和通信方式。

还应该包括系统的数据流、事件流和控制流。

5. 组件设计在这一节中,将描述系统的组件设计。

包括每个组件的功能和接口,以及组件之间的通信方式和数据传输方式。

可以使用图表、序列图等工具来更直观地描述组件之间的交互过程。

6. 数据库设计在本节中,将介绍数据库的设计。

包括数据库的表结构、字段定义、索引和关系等。

可以使用ER图或数据库表格来辅助描述数据库的设计。

7. 部署设计在这一节中,将描述软件系统的部署方案。

包括系统的硬件需求、软件依赖以及部署的流程和策略。

可以使用流程图或架构图来展示系统的部署过程。

8. 安全设计在本节中,将介绍软件系统的安全设计。

包括身份认证、权限控制、数据加密和安全传输等方面。

可以使用流程图或思维导图来展示系统的安全设计方案。

9. 性能设计在这一节中,将详细描述软件系统的性能设计。

包括系统的响应时间、吞吐量、并发性和可扩展性等方面。

可以使用性能测试结果和图表来展示系统的性能指标。

10. 跨平台支持设计在本节中,将介绍软件系统的跨平台支持设计。

包括系统在不同操作系统、浏览器或设备上的兼容性和适应性。

可以使用表格或兼容性矩阵来展示系统的跨平台支持情况。

11. 总结在这一节中,对整个软件架构设计文档进行总结。

可以回顾设计过程中的重要决策和关键问题,并提出对未来工作的建议和展望。

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

H I S系统结构图-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN硬件设备:一、主干网:千兆光纤通信网络二、主机房:双电路,10A,防静电系统、恒温系统三、局域网:以太网(拓扑结构:星型)SISCO 路由器、智能型VLIN交换机、100兆集线器、Lucent 硬体防火墙、23英寸主机机柜、集线架、其他相关设备四、通信协议:ATM、TCP/IP、DICOM3。

0、TELNET、SMTP、POP3、SSL五、标准:HL7,802.3,ISO TC215,CEN TC251六、服务器:WEB,DNS,DB, Email, backup服务器系统是整个计算机信息系统的核心部位,采用先进有效合适的服务器系统能大大提高医院的日常工作效率,提高医院的服务水平,取得更好的经济效益与社会效益。

根据医院规模及业务量的大小,可以选择不同的服务器:1.二级以上医院或业务量较大的医院(如床位在400以上,日门诊量在500人次),一般可选择企业级服务器,如HP ProLiant ML570以上的服务器,一般建议采用由两台服务器加磁盘阵列组成一个集群。

部分较大的医院及业务量较大切医院经济效益较好的医院也可选择小型机或顶级PC-SERVER(如HP ProLiant DL760)等。

2.一般二级医院或业务量较小的(如床位在200左右,日门诊量在400人次左右),一般可选择如HP ProLiant ML530,可根据医院实际需要是否组成集群。

3.一般中心卫生院等一级医院,可选择,如HP ProLiant ML330G2/ ML350G2等服务器服务器通常配置:支持2个P4 CPU(2.4G)512M 内存, 10+ 存储托架,最大热插拔硬盘容量620GB,8MB SDRM显存七、操作系统系统(可选): Win2000八、存储方式: 短期:磁盘阵列长期:磁带库、刻录光盘数据备份是当前HIS数据容错措施的主要手段之一,在具体操作中,可将数据备份在刻录光盘、复制磁带的方式,这是医院确保数据安全性、一致性和灾难恢复的重要措施。

软件技术架构图:绘制步骤与示例软件技术架构图是一个描述软件系统体系结构、技术组件和它们之间关系的图表。

它展示了系统的不同技术层,以及层与层之间的通信方式。

一个有效的技术架构图可以帮助开发人员更好地理解、设计和实现软件系统。

在绘制软件技术架构图时,通常会遵循以下步骤:1.确定系统功能需求:首先,了解系统的功能需求是绘制技术架构图的关键步骤。

了解业务需求、用户需求以及非功能需求等,有助于确定需要哪些技术组件和它们之间的关系。

2.定义技术层:根据系统功能需求,将系统划分为不同的技术层。

通常,一个典型的软件系统可以划分为以下几个层次:a) 表示层(Presentation Layer):负责与用户进行交互,提供用户界面。

b) 业务逻辑层(Business Logic Layer):负责实现系统的业务逻辑。

c) 数据访问层(Data Access Layer):负责与数据存储进行交互,通常包括数据库、文件系统等。

d) 实体类(Entity Classes):代表数据模型中的实体对象,通常位于业务逻辑层和数据访问层之间。

e) 通信层(Communication Layer):负责不同技术层之间的通信,包括网络通信、消息传递等。

f) 基础设施层(Infrastructure Layer):包括操作系统、网络环境、硬件设备等底层设施。

3.确定组件关系:在确定了技术层之后,需要确定层与层之间的通信方式和关系。

例如,表示层和业务逻辑层之间的通信通常是通过API调用的方式进行的。

4.绘制架构图:根据上述步骤,使用图表工具绘制技术架构图。

在绘制架构图时,要确保各个技术层和组件之间的关系清晰明了。

下面是一个示例技术架构图的详细说明:1.表示层:该层包括用户界面和相关的UI组件,例如按钮、表单、列表等。

用户通过表示层与系统进行交互,实现信息的输入和输出。

2.业务逻辑层:该层包括实现系统业务逻辑的组件和功能模块。

例如,一个电商系统的业务逻辑层可能包括购物车管理、订单处理、支付管理等模块。

目录一、技术方案 (2)二、技术服务方案 (13)三、售后服务与技术支持 (14)一、技术方案3.软件开发技术(1)软件架构软件开发主要分为三层架构模式:表示层(User Interface Layer—UI),业务逻辑层(Bussiness Logic Layer—BLL),数据访问层(Data Access Layer —DAL),各层相互独立,高内聚、低耦合,结构如图 1所示。

UI表示层DLL业务逻辑层DAL数据访问层图 1 软件开发架构1)表示层位于系统的最上层,离用户最近。

用于显示数据和接收用户输入的数据,只提供软件系统与用户交互的界面。

2)业务逻辑层位于系统的表示层和数据访问层之间,专门负责处理用户输入的信息,或者是将这些信息发送给数据访问层进行保存,或者是通过数据访问层从数据库读出这些数据。

该层可以包括一些对“业务逻辑”描述的代码在里面。

业务逻辑层是表示层和数据访问层之间的桥梁,负责数据处理和传递。

开发人员可以在业务逻辑层写访问数据库的SQL语句,业务逻辑层可以验证用户输入的数据、缓存从数据库中读取的数据等。

3)数据访问层位于系统的最下层,仅实现对数据的保存和读取操作。

数据访问包括访问数据库系统、二进制文件、文本文档或是XML文档。

数据访问层只负责对数据的访问存取工作。

(2)可扩展标记语言XML(Extensible Markup Language)即可扩展的标记语言,一种常用软件开发技术语言。

XML 是一种应用非常广泛的标记语言,通过一系列文本格式定义规则对文本进行标记。

而作为标记语言,XML主要特点如下:跨平台性:XML 通过-组标记来对文挡进行划分处理,不依赖于任何一种开发语言,只要开发者在开发过程中遵守XML的基本规则,XML文档在任何一种平台下都可以进行有效的解析。

层次结构明确:XML 文档具有严格的格式,通常采用树状结构对文档中的元素进行组织。

可扩展性:在XML 中,开发者可以通过XML 提供的结构化构架定义属于自己的一套标注。

目录1.1软件系统概要设计及总体架构设计 (2)1.1.1系统设计概述 (2)1.1.2系统概要设计(结构设计) (3)1.1.3系统概要设计中的架构设计 (5)1.1.4层架构技术在系统设计中的典型应用 (11)1.1软件系统概要设计及总体架构设计1.1.1系统设计概述1、系统设计(1)什么是系统设计所谓系统设计就是通过某种特定的平台,而达到完成整体软件的功能。

主要涉及包括概要设计(静态结构)和详细设计(动态结构)。

(2)主要任务系统设计阶段的主要任务是在需求分析和建模的基础上,更加深入、综合地考虑辅助决策系统的目标、技术要求和约束,扩展和细化需求分析阶段的模型(3)设计的目标是精化方案并开发一个明确描述方案的可视化模型,保障设计模型最终能平滑地过渡到程序代码,即“怎么做”的问题。

2、系统设计的目的1)是指明一种易转化成代码的工作方案,是对分析工作的细化2)即进一步细化分析阶段所提取的类(包括其操作和属性),并且增加新类以处理诸如数据库、用户接口、通信、设备等技术领域的问题。

3)因为,设计是对问题域外部可见行为的规格说明、并增添实际的计算机系统实现所需的细节,包括人机交互、任务管理和数据管理的细节。

3、分析和设计的合作1)分析面向问题,是明确动力的过程,重在理解和翻译,灵活性高2)设计面向方案,是排除阻力的过程,重在精化和适应,受约束大从整体上看,分析和设计的对立是保障问题和方案趋于一致的基本动力。

就像两个相反方向的张力,使软件朝着正确的方向前进。

1.1.2系统概要设计(结构设计)1、在什么时期进行系统概要设计在需求明确、准备开始编码之前,要做概要设计,概要设计对后面的开发、测试、实施、维护工作起到关键性的影响。

2、系统概要设计工作的主要重点是适应特定的实施环境和部属环境。

工作的核心是规划方案的构造,在揭示实施细节的基础上得到方案的详细对象模型。

3、系统概要设计的重要性1)分析和设计模型是交错并且迭代的2)概要设计的重要性主要体现在它是把需求转化为软件系统的最重要的环节,并且系统设计的优劣在根本上决定了软件系统的质量。

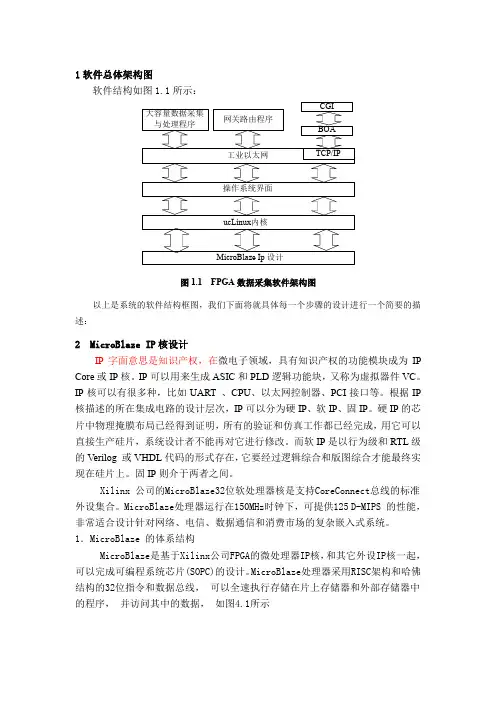

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

为了提高性能,MicroBlaze 还具有指令和数据缓存。

所有的指令字长都是32位,有3个操作数和2 种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线, 它分为3级流水:取指、译码和执行,如图4.2所示。

指令1指令2指令3指令周期4指令周期3指令周期2指令周期1指令周期5图2.2 MicroBlaze 的流水线(2)存储结构MicroBlaze 是一种大端存储系统处理器,使用如图4.3所式的格式来访问存储器。

3178151623240图2.3 大端数据格式(3)中断控制和调试接口MicroBlaze 可以响应软件和硬件中断,进行异常处理, 通过外加控制逻辑, 可以扩展外部中断。

利用微处理器调试模块(MDM)IP 核,可通过JTAG 接口来调试处理器系统。

多个MicroBlaze 处理器可以用1个MDM 来完成多处理器调试。

(4)快速单一链路接口MicroBlaze 处理器具有8个输入和8个输出快速单一链路接口(FSL)。

FSL 通道是专用于单一方向的点到点的数据流传输口。

FLS 和MicroBlaze 的接口宽度是32位。

每一个FSL 通道都可以发送和接收控制或数据字。

2. CoreConnect 技术CoreConnect是由IBM开发的片上总线通信链,它使多个芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中,处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

Xilinx将为所有嵌入式处理器用户提供IBM CoreConnect许可,因为它是所有Xilinx 嵌入式处理器设计的基础。

MicroBlaze处理器使用了与IBM PowerPC 相同的总线,用作外设。

虽然MicroBlaze软处理器完全独立于PowerPC,但它让设计者可以选择芯片上的运行方式,包括一个嵌入式PowerPC,并共享它的外设。

CoreConnect总线架构如图4.4所示。

它包括片上外围总线(OPB),处理器本机总线(PLB),设备控制寄存器(DCR)总线以及1个总线桥和2个判优器。

图2.4 CoreConnect 总线架构(1)片上外设总线(OPB)内核通过片上外设总线(OPB)来访问低速和低性能的系统资源。

OPB是一种完全同步总线,它的功能处于一个单独的总线层级。

它不是直接连接到处理器内核的。

OPB接口提供分离的32 位地址总线和32位数据总线。

处理器内核可以借助“PLB to OPB”桥,通过OPB访问从外设。

作为OPB总线控制器的外设可以借助“OPB to PLB”桥,通过PLB访问存储器。

(2)处理器本机总线(PLB)PLB接口为指令和数据一侧提供独立的32位地址和64位数据总线。

PLB支持具有PLB总线接口的主机和从机通过PLB信号连接来进行读写数据的传输。

总线架构支持多主从设备。

每一个PLB主机通过独立的地址总线、读数据总线和写数据总线与PLB连接。

PLB从机通过共享但分离的地址总线、读数据总线和写数据总线与PLB连接,对于每一个数据总线都有一个复杂的传输控制和状态信号。

为了允许主机通过竞争来获得总线的所有权,有一个中央判决机构来授权对PLB的访问。

(3)设备控制寄存器总线(DCR)设备控制寄存器总线(DCR)是为在CPU通用寄存器(GPRs)和DCR的从逻辑设备控制寄存器(DCRs)之间传输数据而设计的。

3.MicroBlaze 的开发应用EDK(嵌入式开发套件)可以进行MicroBlaze IP核的开发。

工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。

EDK中提供一个集成开发环境XPS(Xilinx Platform Studio),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程。

EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM 控制器、UART、中断控制器、定时器等。

利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。

在FPGA上设计的嵌入式系统层次结构为5级,可在最低层硬件资源上开发IP核,或利用已开发的IP核搭建嵌入式系统,这是硬件开发部分;开发IP核的设备驱动、应用接口(API)和应用层(算法),属软件开发内容。

利用MicroBlaze构建基本的嵌入式系统如图4.5所示。

通过标准总线接口——LMB总线和OPB总线的IP核,MicroBlaze就可以和各种外设IP核相连。

图2.5 MicroBlaze系统架构图EDK中提供的IP核均有相应的设备驱动和应用接口,使用者只需利用相应的函数库,就可以编写自己的应用软件和算法程序。

对于用户自己开发的IP 核,需要自己编写相应的驱动和接口函数。

软件设计流程如图4.6所示。

图2.6 软件开发流程3 移植uclinux首先不管什么平台,移植uclinux,整个流程都遵从于:Kernel preparation —> isntall BSP —> Build hardware platform —> Memory test —> Build kernel image —> Download 具体来说,如下图4.7所示:图3.1 uclinux移植流程1.搭建开发环境操作系统:Redhat Hat Linux 9,安装的时候添加开发和编译环境。

(编译内核)Windows(安装EDK)交叉编译工具:针对不同的CPU系列,有不同的编译环境,通常,程序是在一台计算机上编译,然后再分布到将要使用的其他计算机上。

当主机系统(运行编译器的系统)和目标系统(产生的程序将在其上运行的系统)不兼容时,该过程就叫做交叉编译。

建立一个交叉编译工具链是一个相当复杂的过程,网上有一些编译好的可用的交叉编译工具链可以下载。

下载并安装好,我们的编译环境就搭建好了。

(1)下载并创建BSP从petalogix站点下载BSP,并安装到电脑上。

把在EDK下生成的包含硬件系统信息的“auto-config.in”文件复制到linux的/home/devel/src\uClinux-2.4.x\arch\microblaze\platform\uclinux-auto路径下。

编译器需要从auto-config.in文件里知道“the address map and the processor system”以及其它相关信息。

(2)配置内核在网站上下载源代码包,并安装在系统的任意目录。

此时,就可以使用命令来进行内核的配置了:$cd~/uClinux-dist$make menuconfig这里,我们需要进行一系列内核配置的选择。

(3)编译内核生成image文件$cd ~/uClinux-dist$ make dep$ make clean$ make这个过程期间将完成下面的内容:编译内核(Build kernel)编译uclinux的C库(C libraries )编译用户程序(user applications)转换成二进制文件编译内核文件系统合并内核和文件系统为一个二进制文件编译成功,你就会在uClinux-dist的目录下发现一个新的目录images。

里面就包含了你编译成功的系统文件,image.elf和image.bin两个文件。

(4)下载内核文件到目标板将在上面编译生成的内核文件image.bin下载到目标板上去并运行.4.1 移植工业以太网协议由于Spartan-3E只提供了物理层(PHY)的网络控制器,所以对于处理本装置的物理层以上的网络设备,需要重新制定适合本系统的网络协议。

工业以太网EtherNet/IP,是一种适用于工业环境的通讯体系,能够在广阔的区域中支持大量现场设备的连接。

它采用通用工业协议(CIP)作为其应用层协议。

CIP协议支持各种控制、配置和信息处理服务,包括显式报文(用于信息传输,灵活的报文交换)以及隐式报文(用于控制和实时I/O数据的传输),支持轮询、周期和状态改变数据传输触发机制,点对点单播和广播数据传输方式[3]。

OE服务的设计简化了EtherNet/IP的移植,只需要修改操作环境文件来适合FPGA 操作体系。

4.2 移植BOA从下载一个主流版本的BOA源码包,本系统用的是boa-0.94.13.tar.gz。

第一步:修改Makefile文件,编译BOA源码,生成BOA可执行文件。