元件封装及基本脚位定义说明(精)

- 格式:doc

- 大小:17.50 KB

- 文档页数:4

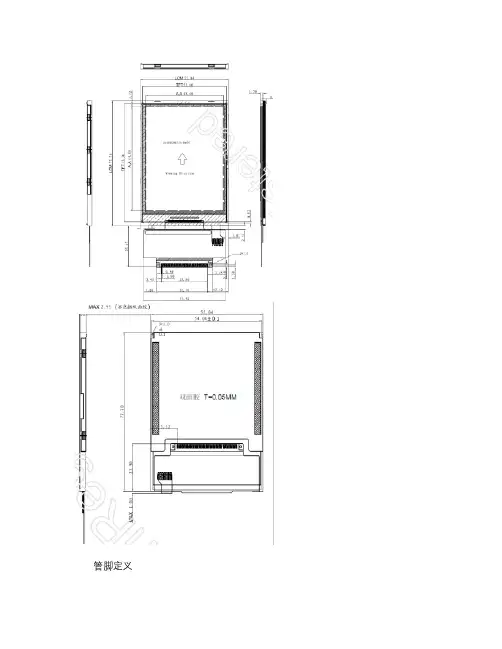

管脚定义1. LCM参数:1.1 屏幕大小:240*RGB*302 dots,262144色(2的(R(6位数+G(6位数+B(6位数)次方)1.2 控制器:HX8347-A1.2.1最低供电电压:1.65V ,内置升压器,1.2.2三种接口模式:①命令参数接口模式②寄存器内容接口模式③RGB 接口模式1.2.3工作温度:-40~85℃ 1.3显示:1.3.1正常显示模式①命令参数接口模式:262144(R(6,G(6,B(6色②寄存器内容接口模式:a262144(R(6,G(6,B(6,b 65536(R(5,G(6,B(5色 1.3.2空闲显示模式①8(R(1,G(1,B(1色1.4显示组件1.4.1 VCOM 控制组件:-2V~5.5V1.4.2 DC/DC转换①DDVDH :3.0V~6.0②VGH :+9.0V~16.5V ③VGL :-6.0V~-13.5V1.4.3 帧存储区域240(水平)*320(垂直)*18bit1.5显示/控制接口1.5.1显示接口模式①命令参数接口模式A .8/16bit并行总线接口B .串行总线接口C .16/18bit并行RGB 总线②寄存器内容接口模式A .8/16/18bit并行接口B .串行总线接口C .16/18bit并行RGB 总线1.5.2控制接口模式IFSEL0=0:命令参数接口模式 IFSEL0=1:寄存器内容接口模式1.5.3电压①逻辑电压(IOVCC ):1.65V~3.3V②驱动电压(VCI ):2.3V~3.3V1.5.4颜色模式A .16Bit :R(5,G(6,B(5A .18Bit :R(6,G(6,B(6接口模式选择:写寄存器:备注:NWR_RNW第一个低电平期间,把数据(index )写出去NWR_RNW第二个低电平期间,把数据(index )写出去读寄存器:备注: NWR_RNW低电平期间,把数据(index )写出去NRD_E低电平期间,把数据(command )读回来写图片RAM读图片RAM接口电路:并行接口特征:GAMMA 寄存器:WINDOW 寄存器:显示模式控制寄存器:Memory 访问控制寄存器:颜色定义:绿色:0x07e0 蓝色:0x001f 白色:0x0000 黑色:0xfffff 混色:0x1234 CYCLE 寄存器:显示控制寄存器:OSC 控制寄存器:Power 寄存器:位 GON DTE D1-0 SAP7-0 AP0-2 PON DK VCOMG 寄存器 R26 R26 R26 R90 R1C R1B R1B R43。

三极管的封装及引脚识别之巴公井开创作三极管的封装形式是指三极管的外形参数,也就是装置半导体三极管用的外壳。

资料方面,三极管的封装形式主要有金属、陶瓷和塑料形式;结构方面,三极管的封装为TO×××,×××暗示三极管的外形;装配方式有通孔插装(通孔式)、概况装置(贴片式)和直接装置;引脚形状有长引线直插、短引线或无引线贴装等。

经常使用三极管的封装形式有TO-92、TO-126、TO-3、TO-220TO 等。

国产晶体管按原部标规定有近30种外形和几十种规格,其外形结构和规格分别用字母和数字暗示,如TO-162、TO-92等。

晶体管的外形及尺寸如图1所示。

图1 晶体管的外形及尺寸1 封装(1)B型:B型分为B-1、B-2、…、B-6共6种规格,主要用于1W及1W以下的高频小功率晶体管,其中B-1、B-3型最为经常使用。

引脚排列:管底面对自己,由管键起,按顺时针方向依次为E、B、C、D(接地极)。

其封装外形如图2(a)所示。

(2)C型:引脚排列与B型相同,主要用于小功率。

其封装外形如图2(b)所示。

(3)D型:外形结构与B型相同。

引脚排列:管底面对自己,等腰三角形的底面朝下,按顺时针方向依次为E、B、C。

其封装外形如图2(c)所示。

(4)E型:引脚排列与D型相同,封装外形如图3(d)所示。

(5)F型:该型分为F-0、F-1~F-4共5种规格,各规格外形相同而尺寸分歧,主要用于低频大功率管封装,使用最多的是F-2型封装。

引脚排列:管底面对自己,小等腰三角形的庵面朝下,左为E,右为B,两固定孔为C。

其封装外形如图2(e)所示。

¨(6)G型:分为G-1~G-6共6种规格,主要用于低频大功率晶体管封装,使用最多的是G-3、G-4型。

其中G-1、G-2为圆形引出线,G-3~G-6为扁形引出线。

引脚排列:管底面对自己,等腰三角形的底面朝下,按顺时针方向依次为E、B、C。

零件封装知识零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

是纯粹的空间概念.因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装。

像电阻,有传统的针插式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电路板上了。

电阻AXIAL无极性电容RAD电解电容RB-电位器VR二极管DIODE三极管TO电源稳压块78和79系列TO-126H和TO-126V场效应管和三极管一样整流桥D-44 D-37 D-46单排多针插座CON SIP双列直插元件DIP晶振XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3。

其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。

一般<100uF用RB.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4发光二极管:RB.1/.2集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5关于零件封装我们在前面说过,除了DEVICE。

电子元器件封装简介及图解部分元件参考封装元件封装是指在PCB编辑器中,为了将元器件固定、安装于电路板,而绘制的与元器件管脚相对应的焊盘、元件外形等。

由于它的主要作用是将元件固定、焊接在电路板上,因此它对焊盘大小、焊盘间距、焊盘孔大小、焊盘序号等参数有非常严格的要求,元器件的封装、元器件实物、原理图元件管脚序号三者之间必须保持严格的对应关系,如图6.8所示,否则直接关系到制作电路板的成败和质量。

小技巧一般双列直插集成电路元件封装的第一脚焊盘为方形,以便于元件安装和检测,与此对应集成块表面的第一脚位置有小点标志。

由图6.8可知,元件封装一般由二部分组成:焊盘和外形轮廓,其中最关键的组成部分是和元件管脚一一对应的焊盘,它的形状和参数如图6.9所示。

焊盘的作用是将元件管脚固定焊接在电路板的铜箔导线上,因此它的各参数直接关系到焊点的质量和电路板的可靠性,一般包含如下参数:焊盘长度(X-Size)、焊盘宽度(Y-Size)、孔径(Hole Size)、序号(Designator)、形状(Shape)等。

在PCB编辑器中双击焊盘,即可打开焊盘属性对话框,可以修改或设置焊盘各属性。

在元件封装中,除了焊盘本身的参数至关重要外,焊盘之间的距离也必须严格和元件实物管脚之间距离保持一致,否则在进行元件装配、焊接时将可能存在元件无法安装等严重问题,元件封装的合理选择非常重要。

图6.8 元件封装与元件实物、原理图元件的对应关系图6.9 PCB板中的焊盘1元件封装的另一组成部分为外形轮廓,相对于焊盘而言,它的参数要求没有焊盘参数那么严格,一般就是从元件顶部向底部看下去所形成的外部轮廓俯视图,它一般在顶层丝印层(Top Overlayer)绘制,默认颜色为黄色。

外形轮廓主要用于标志元件在电路板上所占面积大小和安装极性,从而便于元件的整体布局,同时还便于元件的安装。

在Protel DXP 安装目录下的“*:\Program Files\Altium\Library\”目录中,存放着大量的PCB元件封装库,在不同的元件封装库中又含有许多不同种类、不同尺寸大小的PCB元件封装,熟练了解Protel DXP 元件封装库的各种封装是正确、快速地为元件选用合适封装的前提,而合适的选择元件封装是成功制作电路板的第一步。

单片机脚位定义

单片机的脚位定义,因不同品牌、型号而异,以下是常见单片机脚位的定义:

1. 电源脚:VCC 和GND 为电源正、负极脚,分别连接正、负电源。

2. 晶振脚:XTAL1、XTAL2 为晶振输入、输出脚,连接晶振及其补偿电容。

3. 复位脚:RESET 为复位脚,通常接外部复位电路,或通过内部电路实现复位功能。

4. I/O口脚:GPIO 为通用输入/输出脚,可以设置为输入、输出或特殊功能。

5. 中断脚:INT0、INT1 等为中断脚,可以触发外部中断服务程序。

6. 系统时钟脚:CLK、CLKIN、CLKOUT 等为系统时钟相关脚,用于时基、计时等应用。

7. 串口脚:RX、TX 等为串口通信相关脚,用于与其他设备进行数据通信。

8. 程序存储器脚:ROM、FLASH 等为程序存储器相关脚,用于存储程序代码。

9. 数据存储器脚:RAM、EEPROM 等为数据存储器相关脚,用于存储变量、常量等数据。

10. 特殊功能脚:比如PWM、ADC、DAC、I2C、SPI 等的相关脚,用于实现特定的功能。

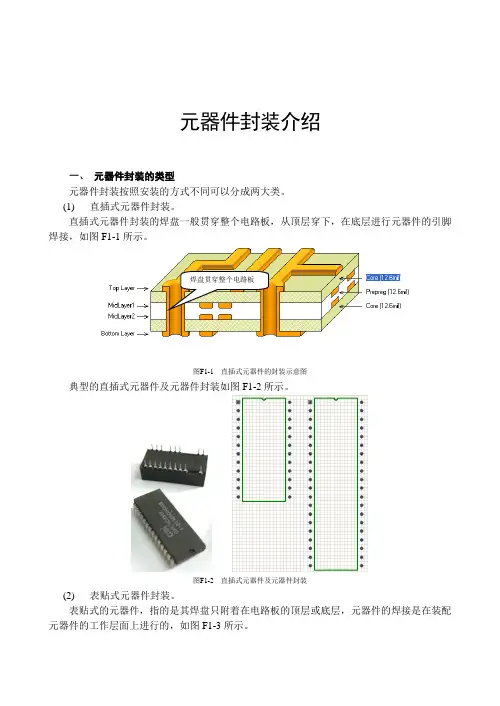

元器件封装介绍一、元器件封装的类型元器件封装按照安装的方式不同可以分成两大类。

(1)直插式元器件封装。

直插式元器件封装的焊盘一般贯穿整个电路板,从顶层穿下,在底层进行元器件的引脚焊接,如图F1-1所示。

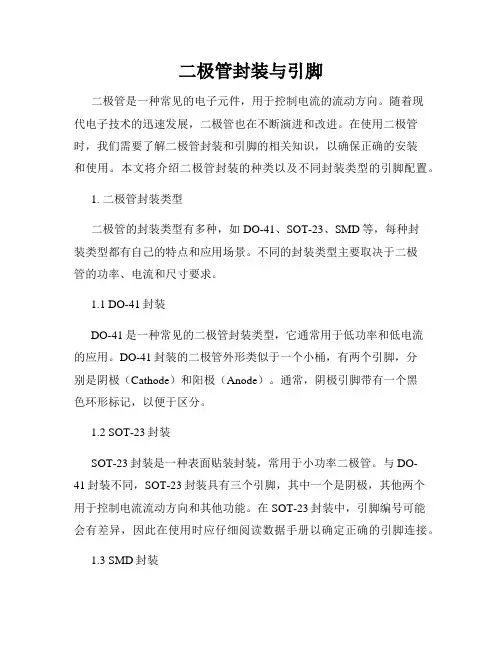

图F1-1 直插式元器件的封装示意图典型的直插式元器件及元器件封装如图F1-2所示。

图F1-2 直插式元器件及元器件封装(2)表贴式元器件封装。

表贴式的元器件,指的是其焊盘只附着在电路板的顶层或底层,元器件的焊接是在装配元器件的工作层面上进行的,如图F1-3所示。

焊盘贯穿整个电路板Protel 99 SE基础教程2图F1-3 表贴式元器件的封装示意图典型的表贴式元器件及元器件封装如图F1-4所示。

图F1-4 表贴式元器件及元器件封装在PCB元器件库中,表贴式的元器件封装的引脚一般为红色,表示处在电路板的顶层(Top Layer)。

二、常用元器件的原理图符号和元器件封装在设计PCB的过程中,有些元器件是设计者经常用到的,比如电阻、电容以及三端稳压源等。

在Protel 99 SE中,同一种元器件虽然相同电气特性,但是由于应用的场合不同而导致元器件的封装存在一些差异。

前面的章节中已经讲过,电阻由于其负载功率和运用场合不同而导致其元器件的封装也多种多样,这种情况对于电容来说也同样存在。

因此,本节主要向读者介绍常用元器件的原理图符号和与之相对应的元器件封装,同时尽量给出一些元器件的实物图,使读者能够更快地了解并掌握这些常用元器件的原理图符号和元器件封装。

(1)电阻。

电阻器通常简称为电阻,它是一种应用十分广泛的电子元器件,其英文名字为“Resistor”,缩写为“Res”。

电阻的种类繁多,通常分为固定电阻、可变电阻和特种电阻3大类。

固定电阻可按电阻的材料、结构形状及用途等进行多种分类。

电阻的种类虽多,但常用的电阻类型主要为RT型碳膜电阻、RJ型金属膜电阻、RX型线绕电阻和片状电阻等。

固定电阻的原理图符号的常用名称是“RES1”和“RES2”,如图F1-5(a)所示。

二极管封装与引脚二极管是一种常见的电子元件,用于控制电流的流动方向。

随着现代电子技术的迅速发展,二极管也在不断演进和改进。

在使用二极管时,我们需要了解二极管封装和引脚的相关知识,以确保正确的安装和使用。

本文将介绍二极管封装的种类以及不同封装类型的引脚配置。

1. 二极管封装类型二极管的封装类型有多种,如DO-41、SOT-23、SMD等,每种封装类型都有自己的特点和应用场景。

不同的封装类型主要取决于二极管的功率、电流和尺寸要求。

1.1 DO-41封装DO-41是一种常见的二极管封装类型,它通常用于低功率和低电流的应用。

DO-41封装的二极管外形类似于一个小桶,有两个引脚,分别是阴极(Cathode)和阳极(Anode)。

通常,阴极引脚带有一个黑色环形标记,以便于区分。

1.2 SOT-23封装SOT-23封装是一种表面贴装封装,常用于小功率二极管。

与DO-41封装不同,SOT-23封装具有三个引脚,其中一个是阴极,其他两个用于控制电流流动方向和其他功能。

在SOT-23封装中,引脚编号可能会有差异,因此在使用时应仔细阅读数据手册以确定正确的引脚连接。

1.3 SMD封装SMD(Surface Mount Device)封装是一种广泛应用的小型封装类型,也常用于二极管。

它具有多种不同的尺寸和形状,常见的有SOD-123、SOD-323等。

SMD封装的二极管通常有两个引脚,类似于DO-41封装,但其尺寸更小,适用于高密度的电路设计。

2. 引脚标识和功能在安装和使用二极管时,正确理解和连接引脚是至关重要的。

虽然不同封装类型的引脚安排可能有所不同,但以下标识和功能适用于大多数二极管封装。

2.1 阴极(Cathode)阴极是二极管的一个引脚,通常用黑色环形标记来表示。

它是负极,也被称为地极(Ground)。

在连接二极管时,阴极应该连接到电源中的负极。

2.2 阳极(Anode)阳极是二极管的另一个引脚,没有任何标记来表示。

电子元器件封装全解析按封装形式分:一般双列直插式,一般单列直插式,小型双列扁平,小型四列扁平,圆形金属,体积较大的厚膜电路等。

按封装体积大小排列分:最大为厚膜电路,其次分别为双列直插式,单列直插式,金属封装、双列扁平、四列扁平为最小。

两引脚之间的间距分:一般标准型塑料封装,双列、单列直插式一样多为2.54±0.25 mm,其次有2mm(多见于单列直插式)、1.778±0.25mm(多见于缩型双列直插式)、1.5±0.25mm,或1.27±0.25mm(多见于单列附散热片或单列V型)、1.27±0.25mm(多见于双列扁平封装)、1±0.15mm(多见于双列或四列扁平封装)、0.8±0.05~0.15mm(多见于四列扁平封装)、0.65±0.03mm(多见于四列扁平封装)。

双列直插式两列引脚之间的宽度分:一样有7.4~7.62mm、10.16mm、12.7mm、15.24mm等数种。

双列扁平封装两列之间的宽度分(包括引线长度:一样有6~6.5±mm、7.6mm、10.5~10.65mm等。

四列扁平封装40引脚以上的长×宽一样有:10×10mm(不计引线长度)、13.6×13.6±0.4mm(包括引线长度)、20.6×20.6±0.4mm(包括引线长度)、8.45×8.45±0.5mm(不计引线长度)、14×14±0.15mm(不计引线长度)等。

1、BGA(ball grid array)球形触点陈设,表面贴装型封装之一。

在印刷基板的背面按陈设方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈设载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装设计知识介绍1.封装的基本概念通常设计完电路板后,将它拿到专门的制板单位,制作成电路板,然后取回电路板,将元件焊接在电路板上。

那么,如何保证管脚与电路板的焊盘一致呢?这就必须依靠元件的封装。

元件封装是指元件焊接到电路板时的外观和焊盘的位置。

既然元件封装只是元件的外观和焊盘的位置,那么元件的封装仅仅是空间的概念,因此,不同的元件可以共用同一个元件封装,另一方面,同种元件可以有不同的封装,所以在取用焊接元件时,不仅要知道元件名称,还要知道元件的封装。

元件的封装形式主要可以分成两大类,即针脚式元件封装和SMT(贴片式)元件封装。

针脚式元件封装焊接时需要将元件针脚插入焊盘导通孔,然后再焊锡。

SMT元件封装的焊盘只限于表面层,在选择焊盘属性时必须为单一层面。

电路板上的元件大致可以分为3类,即连接器、分立元件和集成电路。

元件封装信息的获取通常有两种途径,即元件数据手册和自己测量。

元件的数据手册可以从厂商或互联网上获取。

元件封装中最主要的是焊盘的选择。

焊盘的作用是放置焊锡从而连接导线和元件的管脚。

焊盘是PCB设计中最常接触的也是最重要的概念之一。

在选用焊盘时要从多方面考虑,可选的焊盘类型很多,包括圆形、方形、六角形等。

在设计焊盘时,需要考虑到以下因素: 发热量的多少电流的大小当形状上长短不一致时,要考虑连线宽度与焊盘特定边长的大小差异不能过大需要在元件管脚之间布线时,选用长短不同的焊盘焊盘的大小要按元件管脚的粗细分别进行编辑确定对于DIP封装的元件,第一管脚一般为正方形,其他为圆形2.封装设计中使用的尺寸单位英制单位inch、mil,换算关系1 inch=1000 mil,公制单位mm,一般优先选择英制单位。

公英制单位换算关系为:1 inch =25.4 mm 1 mil =0.0254 mm 100 mil =2.54 mm封装设计中常用数值换算关系为:200 mil =5.08 mm 300 mil =7.62 mm 400 mil =10.16 mm一般估算时,可认为1 mm ≈40 mil,0.1 mm ≈ 4 mil3.DIP封装设计①焊盘数量。

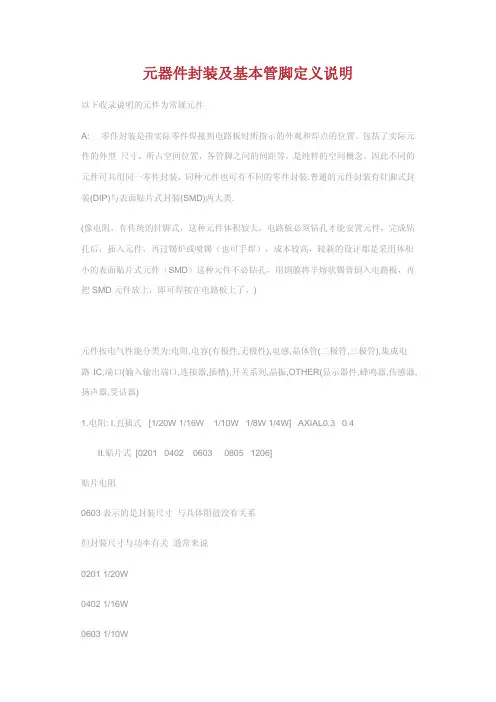

元器件封装及基本管脚定义说明以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装.普通的元件封装有针脚式封装(DIP)与表面贴片式封装(SMD)两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电路板上了。

)元件按电气性能分类为:电阻,电容(有极性,无极性),电感,晶体管(二极管,三极管),集成电路IC,端口(输入输出端口,连接器,插槽),开关系列,晶振,OTHER(显示器件,蜂鸣器,传感器,扬声器,受话器)1.电阻: I.直插式[1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4II.贴片式[0201 0402 0603 0805 1206]贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5III.整合式[0402 0603 4合一或8合一排阻]IIII.可调式[VR1~VR5]2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II.有极性电容分两种:电解电容[一般为铝电解电容,分为DIP与SMD两种]钽电容[为SMD型: A TYPE (3216 10V) B TYPE (3528 16V) C TYPE (6032 25V) D TYPE (7343 35V)]3.电感: I.DIP型电感II.SMD型电感4.晶体管: I.二极管[1N4148 (小功率) 1N4007(大功率) 发光二极管(都分为SMD DIP 两大类)]II.三极管[SOT23 SOT223 SOT252 SOT263]常见的to-18(普通三极管)to-22 (大功率三极管)to-3 (大功率达林顿管)5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立) LAN COM(DB-9)RGB(DB-15) LPT DVI USB(常规,微型) TUNER(高频头) GAME 1394 SATA POWER_JACK等]II.排针[单排双排(分不同间距,不同针脚类型,不同角度)过 IDE FDD,与其它各类连接排线.III.插槽 [DDR (DDR分为SMD与DIP两类) CPU座PCIE PCI CNR SD MD CF AGP PCMCIA]6.开关:I.按键式II.点按式III.拔动式IIII.其它类型7.晶振: I.有源晶振(分为DIP与SMD两种包装,一個電源PIN,一個GND PIN,一個訊號PIN)II.无源晶振(分为四种包装,只有接兩個訊號PIN,另有外売接GND)8.集成电路IC:I.DIP(Dual In-line Package):双列直插封装。

元器件封装定义及分类

元器件封装是将电子元器件包装起来,以保护元器件,方便安装和使用。

根据元器件的尺寸、功率、形状、引脚数量和布局等因素,元器件封装可分为多种类型。

常见的元器件封装类型有:

1. DIP封装:双列直插封装,适用于引脚数量较少的元器件,如二极管、三极管等。

2. SOP封装:小外形直插封装,适用于引脚数量较多的集成电路和场效应管等元器件。

3. QFP封装:正方形扁平封装,适用于高密度元器件,如微处理器、控制器、存储器等。

4. BGA封装:球格阵列封装,适用于高密度、高速度、高功率的微处理器、控制器、存储器等。

5. SMT封装:表面贴装封装,适用于引脚数量少、尺寸小的元器件,如电容、电感、电阻等。

以上是常见的元器件封装类型,不同的封装类型适用于不同的元器件,有助于提高电路的可靠性和性能。

- 1 -。

PCBFootprint命名规则及封装标准定义2.1 SMD类电阻命名规则:R+封装尺⼨,如:R0603 表⽰贴⽚电阻封装为0603⼤⼩注:⼀般零件封装,采⽤公制mm为单位,但0201、0402、0603等贴⽚⼩零件采⽤英制mil为单位。

◆可供选择的封装形式列表2.2R-11_5X5-10_52.3 DIP⽴式电阻的命名规则:R-D(mm)-Pitch,如R-D7_5-52.4 电阻排的命名规则:RP-排阻类型-封装尺⼨LXW(mm),如:RP-8P4R-04023 电容的命名⽅法3.1 SMD类电容命名规则:C+封装尺⼨LXW(mm),如:C0402◆可供选择的封装形式列表◆3.2 DIP卧式类和⽴式⽅形类电容命名规则:C-封装尺⼨LXW(mm)-Pitch,如:C-10_3X6-7_53.3 DIP⽴式圆形类电容命名规则:C-D(mm)-Pitch(mm) 或C-D(mm)XH(mm)-Pitch(mm),如:C-D6-2_5, C-D5XH12-23.4 排容命名规则:CP-排容类型-封装尺⼨LXW(mm),如:CP-8P4C-06033.5 钽电容命名规则:TAN-封装尺⼨LXW(mm),如:TAN-A4 电感磁珠的命名⽅法4.1 SMD类电感磁珠命名规则:L+封装尺⼨LXW(mm),如:L08054.2 DIP圆形类电感磁珠命名规则:L-D(mm)-Pitch(mm),如:L-D7_5-54.3 DIP⽅形类电感磁珠命名规则:L-封装尺⼨LXW(mm)-Pitch(mm),如:L-9X16_5-65 ⼆极管的命名⽅法5.1 SMD类⼆极管命名规则:D+封装尺⼨LXW(mm),如:D+06035.2 DIP圆形类⼆极管命名规则: D-D(mm)-Pitch(mm):如:D-D5-2_55.3 DIP⽅形类⼆极管命名规则: D-封装尺⼨LXW(mm)-Pitch(mm):如:D-7_5X9-2_56 发光⼆极管的命名⽅法6.1 SMD类发光⼆极管命名规则:LED+封装尺⼨LXW(mm),如:LED06036.2 DIP圆形类发光⼆极管命名规则: LED-D(mm)-Pitch(mm):如:LED-D5-2_56.3 DIP⽅形类发光⼆极管命名规则: LED-封装尺⼨LXW(mm)-Pitch(mm):如:LED-7_5X9-2_57 变压器的命名⽅法7.1 规则变压器命名规则:T-封装尺⼨LXW(mm)-Pin数-Pitch, 如:T-12_15X11_35-10P-27.2 不规则变压器命名规则:T-封装尺⼨LXW(mm)-Pin数, 如:T-32_6X10-8P8 继电器的命名⽅法8.1 规则继电器命名规则:RE-封装尺⼨LXW(mm)-Pin数-Pitch, 如:RE-7_5X15-8P-2_548.2 不规则继电器命名规则:RE-封装尺⼨LXW(mm)-Pin数, 如:RE-10_5X16-8P9 保险丝的命名⽅法9.1 SMD保险丝命名规则:F-封装尺⼨LXW(mm),如:F-6_1X2_699.2 DIP保险丝命名规则:F-封装尺⼨LXW(mm)-Pitch,如:F-9X3_8-510 滤波器的命名⽅法10.1 滤波器的命名规则: FIL-封装尺⼨LXW(mm)-Pin数,如:FIL-3_1X3_45-6P11 散热⽚的命名⽅法11.1 散热⽚的命名规则:HS-封装尺⼨LXW(mm),如:HS-44X4412 放电管的命名⽅法12.1 SMD放电管的命名规则: DT-封装尺⼨LXW(mm),如:DT-3_76X1_712.2 DIP放电管的命名规则: DT-封装尺⼨LXW(mm)-Pin数,如:DT-12_2X3-2P13 SOT系列晶体管的命名⽅法13.1 NPN型三极管命名规则:SOT-封装-NPN,如:SOT-23-NPN13.2 PNP型三极管命名规则:SOT-封装-PNP,如:SOT-23-PNP13.3 其它:SOT-封装-Pin数,如:SOT-232-5P14 TO系列封装命名⽅法14.1 规则: TO-封装-Pin数,如:TO-263-5P15 晶振的命名⽅法15.1 晶振的命名规则:OSC-封装尺⼨LXW(mm)-Pin数,如:OSC-5X3_2-4P16 场效应管的命名⽅法16.1 场效应管的命名规则:MOS-封装-DGS17 雷击保护器的命名⽅法17.1 雷击保护器的命名规则:THY-封装尺⼨LXW(mm)-Pin数,如:THY-12_5X13-6P18 电池的命名⽅法18.1 电池的命名规则:BA-封装型号,如:BA-170577119 桥式整流器的命名⽅法19.1 桥式整流器的命名规则:BE-封装型号,如:BE-B6S20 其它器件的命名⽅法20.1 其它器件的命名规则:O-封装,如:O-201121 插座的命名⽅法21.1 规则:JACK-插座型号-LXW(mm)或JACK-LXW(mm)- Pin数(mm),如:JACK-DC-14_5X9,JACK-11_7X10_7-4P21.2 规则:RJ45-Port数- Pin数(mm)或RJ45-LXW(mm)- Pin数(mm)如,RJ45-1X4-32P, RJ45-21X15_3-12P21.3 规则:RJ11-插座型号-LXW(mm),如,RJ11-SIG-13_1X12,RJ11-13x12-4P21.4 规则:DB9-插座型号,如,DB9F21.5 规则:USB-插座型号-LXW(mm),如,USB-14X13_7-4P22 连接器的命名⽅法22.1 单排:CN-Pin数-Pitch,如,CN-40P-1_2722.2 多排:CN-⾏X列-Pin数-Pitch,如,CN-2X2-4P-2_5422.3 其它连接器:CN-Pin数-型号,如,CN-38P-76700423 开关的命名⽅法23.1 开关的名规则:SW-封装尺⼨LXW(mm)-Pin数,如, SW-6_8X6_4-5P24 跳线的命名⽅法24.1 跳线的命名规则:JP-封装型号,如,JP-USB25 ⾦⼿指的命名⽅法25.1 ⾦⼿指的命名规则:GF-封装型号-Pin数,如,GF-MINPCI-124P26 BGA系列26.1 规则: BGA-LXW(mm)-PIN数-Pitch如:BGA-12X12-196P-0_8表⽰:⼤⼩为12X12(mm),PIN数196,pin间距 0.8 mm 27 PGA系列27.1 规则: PGA-LXW(mm)-PIN数-Pitch28CSP系列28.1 规则: CSP-LXW(mm)-PIN数-Pitch,如,CSP-13X11-64P-129PLCC系列29.1 规则: PLCC-PIN数,如,PLCC8430QFP系列30.1 规则:QFP-LXW(mm)-PIN数-Pitch,如,QFP-12X12-52P-0_6531QFN系列31.1 规则:QFN-LXW(mm)-PIN数-Pitch,如,QFN-7X7-48P-0_532DFN系列32.1 规则:DFN-LXW(mm)-PIN数-Pitch,如,DFN-3X3-8P-0_533SO系列33.1 规则:SO-LXW(mm)-PIN数-Pitch,如,SO-4_9X3-8P-0_6534DIP系列34.1 规则:DIP-PIN数,如,DIP-1435SIP系列35.1 规则:SIP-LXW(mm)-PIN数-Pitch36其它IC的命名⽅法36.1 规则:OIC-LXW(mm)-其它,如:OIC-14X10-49P-0_8537 保护盖的命名⽅法37.1 规则:SF-LXW(mm)-其它,如:SF-40_2x2938 螺丝孔命名规则38.1 NPTH螺丝孔命名规则:GMTH+孔直径,如:GMTH103 表⽰:孔径103mil不镀铜螺丝孔38.2 PTH螺丝孔命名规则:GMPTH+孔直径+外环直径,如:GMPTH80R160 表⽰:孔径80mil,外环160mil的镀铜螺丝孔38.3 NPTH椭圆捞孔命名规则: GMTH+捞孔尺⼨(⼩X⼤),如:GMTH80X160 表⽰:孔径80milX160mil的不镀铜捞孔38.4 PTH椭圆捞孔命名规则: GMPTH+外环尺⼨(⼩X⼤)+D+捞孔尺⼨(⼩X⼤),如:GMPTH64X252D40X228 表⽰:外环64X252mil,捞孔40X228mil的镀铜捞孔39 光学点命名⽅法39.1 圆形光学点命名规则:FIDMC39.2 矩形光学点命名规则:FIDMR40 LABEL命名⽅法40.1 LABEL命名规则: LABEL+封装尺⼨LXW(mm),如:LABEL20X1041 测试点命名⽅法41.1 规则: TP+封装尺⼨(mil),如:TP3041 圆形焊盘41.1 SMD: C+直径 ,如: C1441.2 DIP: C+外环直径+D+内径 ,如: C80D6042 长⽅形焊盘42.1 SMD: R+尺⼨⼤⼩(⼩X⼤),如:R20X4042.2 DIP: R+尺⼨⼤⼩(⼩X⼤)+D+孔径,如:R40X60D2043 正⽅形焊盘43.1 SMD: S+尺⼨⼤⼩,如:S2043.2 DIP: S+尺⼨⼤⼩+D+孔径,如: S40D2044 椭圆焊盘44.1 SMD: O+尺⼨⼤⼩(⼩X⼤),如:O20X4044.2 DIP: O+外环尺⼨(⼩X⼤)+D+孔径,如:O44X55D3244.3 DIP捞孔: O+外环尺⼨(⼩X⼤)+D+内环尺⼨(⼩X⼤),如:O31X47D21X3745 过孔焊盘45.1 规则:V+外径+D+内径,如:V24D1246 定位孔46.1 NPTH定位孔命名规则:MTH+孔径,如:MTH13046.2 PTH定位孔命名规则:MPTH+孔径+R+外环直径,如:MPTH32R5647 FLASH焊盘47.1 规则: 外径X内径X⾓度X开⼝数X开⼝宽度如: 80x60x45x4x2048 SHAPE焊盘48.1 规则: A-器件封装名如: A-sot89Footprint标准封装定义1、实体层: class PACKAGE GEOMETRYsubclass ASSEMBLY_TOP线宽定义:2mil 表⽰零件实际的尺⼨,如长、宽等。

电子元器件封装简介及图解部分元件参考封装元件封装是指在PCB编辑器中,为了将元器件固定、安装于电路板,而绘制的与元器件管脚相对应的焊盘、元件外形等。

由于它的主要作用是将元件固定、焊接在电路板上,因此它对焊盘大小、焊盘间距、焊盘孔大小、焊盘序号等参数有非常严格的要求,元器件的封装、元器件实物、原理图元件管脚序号三者之间必须保持严格的对应关系,如图6.8所示,否则直接关系到制作电路板的成败和质量。

小技巧一般双列直插集成电路元件封装的第一脚焊盘为方形,以便于元件安装和检测,与此对应集成块表面的第一脚位置有小点标志。

由图6.8可知,元件封装一般由二部分组成:焊盘和外形轮廓,其中最关键的组成部分是和元件管脚一一对应的焊盘,它的形状和参数如图6.9所示。

焊盘的作用是将元件管脚固定焊接在电路板的铜箔导线上,因此它的各参数直接关系到焊点的质量和电路板的可靠性,一般包含如下参数:焊盘长度(X-Size)、焊盘宽度(Y-Size)、孔径(Hole Size)、序号(Designator)、形状(Shape)等。

在PCB编辑器中双击焊盘,即可打开焊盘属性对话框,可以修改或设置焊盘各属性。

在元件封装中,除了焊盘本身的参数至关重要外,焊盘之间的距离也必须严格和元件实物管脚之间距离保持一致,否则在进行元件装配、焊接时将可能存在元件无法安装等严重问题,元件封装的合理选择非常重要。

图6.8 元件封装与元件实物、原理图元件的对应关系图6.9 PCB板中的焊盘1元件封装的另一组成部分为外形轮廓,相对于焊盘而言,它的参数要求没有焊盘参数那么严格,一般就是从元件顶部向底部看下去所形成的外部轮廓俯视图,它一般在顶层丝印层(Top Overlayer)绘制,默认颜色为黄色。

外形轮廓主要用于标志元件在电路板上所占面积大小和安装极性,从而便于元件的整体布局,同时还便于元件的安装。

在Protel DXP 安装目录下的“*:\Program Files\Altium\Library\”目录中,存放着大量的PCB元件封装库,在不同的元件封装库中又含有许多不同种类、不同尺寸大小的PCB元件封装,熟练了解Protel DXP 元件封装库的各种封装是正确、快速地为元件选用合适封装的前提,而合适的选择元件封装是成功制作电路板的第一步。

贴片式元件表面组装技术(surface Mount Technology 简称SMT) 表面贴装器件 (Surface Mounted Devices 简称SMD)一、表面贴片组件(形状和封装的规格)表面贴片技术由1960年代开始发展,在1980年代逐渐广泛采用,至现在已发展多种类SMD 组件,优点是体积较小,适合自动化生产而使用在线路更密集的底板上。

SMD 组件封装的形装和尺寸的规格都已标准化,由JEDEC 标准机构统一,以下是SMD 组件封装的命名:1. 二个焊接端的封装形式:矩形封装:通常有片式电阻(Chip-R)/ 片式电容(Chip-C)/ 片式磁珠 (Chip Bead),常以它们的外形尺寸(英制)的长和宽命名,来标志它们的大小,以英制(inch) 或 公制(mm)为单位, 1inch=25.4mm ,如外形尺寸为0.12in×0,06in,记为1206,公制记为3.2mm×1.6mm。

常用的尺寸规格见下表:(一般长度误差值为±10%)NO 英制名称 长(L) "X 宽(W) "公制(M)名称 长(L)X 宽(W) mm 1 01005 0.016" × 0.008" 0402M 0.4 × 0.2 mm 2 0201 0.024” × 0.012" 0603M 0.6 × 0.3 mm 3 0402 0.04” × 0.02" 1005M 1.0 × 0.5mm 4 0603 0.063" × 0.031" 1608M 1.6 × 0.8 mm 5 0805 0.08" × 0.05" 2012M 2.0 × 1.25 mm 6 1206 0.126" × 0.063" 3216M 3.2 × 1.6 mm 7 1210 0.126" × 0.10" 3225M 3.2 × 2.5 mm 8 1808 0.18" × 0.08" 4520M 4.5 × 2.0 mm 9 1812 0.18" × 0.12" 4532M 4.5 × 3.2 mm 10 2010 0.20" × 0.10" 5025M 5..0 × 2.5 mm 11 2512 0.25" × 0.12" 6330M 6.3 × 3.0 mm 较特别尺寸如下:NO 英制名称 长(L) "X 宽(W) " 公制(M)名称 长(L)X 宽(W) mm 1 0306 0.031" × 0.063" 0816M 0.8 ×1.6 mm 2 0508 0.05" × 0.08" 0508M 1.25 × 2.0mm 3 06120.063" ×0.12"0612M1.6 × 3.0 mm注:1、L (Length ):长度; W (Width ):宽度; inch :英寸2、1inch=25.4mm片式电阻(Chip-R ) 片式磁珠 (Chip Bead )片式电容(Chip Cap )MELF 封装:MELF(是Metal Electrical Face 的简称) 圆柱体的封装形式,通常有晶圆电阻(Melf-R ) /贴式电感(Melf Inductors ) /贴式二极管(Melp Diodes ):NO 工业命名 公制(M)名称 长(L)X 直径(D) mm 1 0102 2211M 2.2 × 1.1 mm 2 0204 3715M 3.6 × 1.4 mm 3 0207 6123M 5.8 × 2.2 mm 403098734M8.5 × 3.2 mmSOD 封装:专为小型二极管设计的一种封装。

PCB换算:100mil=2.54mm 圆形焊盘默认孔径30mil (0.762mm,总直径60mil (1.524mm 。

自恢复电阻管脚直径0.6mm封装定义孔径为0.7mm总直径1.5mm压敏电阻管教直径1mm圭寸装定义孔径1.27m(50mil ),总直径2.54m(100mil )。

焊接220V导线的焊盘:3mm x 1.8mm电源线不低于18mil,信号线不低于12mil , cpu入出线不低于10mil (或8mil ), 线间距不低于10mil。

正常过孔不低于30mil (内孔一般不能小于10mil )。

一般封装只与功率有关。

1 •贴封装-两脚表贴现在常用的的电阻、电容、电感、二极管都有贴片封装。

贴片封装用四位数字标识,表明了器件的长度和宽度。

贴片电阻有百分五和百分一两种精度,购买时不特别说明的话就是指百分五。

一般说的贴片电容是片式多层陶瓷电容电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.5 0603=1.6x0.8 0805=2.0x1.21206=3.2x1.6 1210=3.2x2.5 1812=4.5x3.2 2225=5.6x6.5国内贴片电阻的命名方法:1、5%精度的命名:RS-05K102JT2、1%精度的命名:RS-05K1002FTR 一表示电阻S —表示功率0402是1/16W 0603是1/10W 0805是1/8W 1206是1/4W、1210 是1/3W A 1812是1/2W A 2010是3/4W 2512是1W05 —表示尺寸(英寸):02表示0402、03表示0603、05表示0805、06表示1206、1210表示1210、1812表示1812、10表示1210、12 表示2512。

K —表示温度系数为100PPM,102—5%精度阻值表示法:前两位表示有效数字,第三位表示有多少个零,基本单位是Q, 102= 10000 Q = 1K Q。

电子元器件封装技术详细介绍电子元器件封装技术详细介绍1、BGA(ballgridarray):球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304引脚QFP为40mm见方。

而且BGA不用担心QFP那样的引脚变形问题。

该封装是美国Motorola公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500引脚的BGA。

BGA的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC和GPAC)。

2、BQFP(quadflatpackagewithbumper):带缓冲垫的四侧引脚扁平封装。

QFP封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC等电路中采用此封装。

引脚中心距0.635mm,引脚数从84到196左右(见QFP)。

3、碰焊PGA(buttjointpingridarray):表面贴装型PGA的别称(见表面贴装型PGA)。

4、C-(ceramic):表示陶瓷封装的记号。

例如,CDIP表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip:用玻璃密封的陶瓷双列直插式封装,用于ECLRAM,DSP(数字信号处理器)等电路。

元件封裝及基本腳位定義說明 PS:以下收录说明的元件为常规元件 A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装.普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类. (像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电路板上了。

元件按电气性能分类为:电阻,电容(有极性,无极性,电感,晶体管(二极管,三极管,集成电路IC,端口(输入输出端口,连接器,插槽,开关系列,晶振,OTHER(显示器件,蜂鸣器,传感器,扬声器,受话器 1.电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] II.贴片式 [0201 0402 0603 0805 1206] III.整合式 [0402 0603 4合一或8合一排阻] IIII.可调式[VR1~VR5] 2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225] II.有极性电容分两种: 电解电容 [一般为铝电解电容,分为DIP与SMD两种] 钽电容 [为SMD型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25V D TYPE (7343 35V] 3.电感: I.DIP型电感 II.SMD型电感 4.晶体管: I.二极管[1N4148 (小功率 1N4007(大功率发光二极管 (都分为SMD DIP两大类] II.三极管[SOT23 SOT223 SOT252 SOT263] 5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立 LAN COM(DB-9 RGB(DB-15 LPT DVI USB(常规,微型 TUNER(高频头 GAME 1394 SATA POWER_JACK等] II.排针[单排双排 (分不同间距,不同针脚类型,不同角度过 IDE FDD,与其它各类连接排线. III.插槽 [DDR (DDR分为SMD与DIP两类CPU座 PCIE PCI CNR SD MD CF AGP PCMCIA] 6.开关:I.按键式 II.点按式 III.拔动式 IIII.其它类型 7.晶振: I.有源晶振 (分为DIP与SMD两种包装,一個電源PIN,一個GND PIN,一個訊號PIN II.无源晶振(分为四种包装,只有接兩個訊號PIN,另有外売接GND) 8.集成电路IC: I.DIP(Dual In-line Package):双列直插封装。

& SIP(Single inline Package):单列直插封装 II.SOJ (Small Out-Line J-Leaded Package):J形引线小外形封装。

& SOP (Small Out-Line Package):小外形封装。

III.QFP (Quad Flat Package):方形扁平封装。

IIII.PLCC(Plastic LeadedChip Carrier):有引线塑料芯片栽体。

IV.PGA(Ceramic Pin Grid Arrau Package)插针网格阵列封装技术 IV.BGA (Ball Grid Array):球栅阵列,面阵列封装的一种。

OTHERS: COB(Chip on Board):板上芯片封装。

Flip-Chip:倒装焊芯片。

9.Others B: PIN的分辨与定义 1.二极管 & 有极性电容: (正负极 AC PN 2.三极管(BCE GDS ACA AIO 3.排阻 & 排容 [13572468 12345678] 4.排针 [主要分两种:1357.... 2468... 12345678...] 5.集成电路:集成电路的封装大都是对称式的,如果不在集成电路封装上设立PIN识别标示,则非常容易错接,反接等差错,使産品设计失败. 6.OTHERS 一般常見端口PIN定義此項技能考核參考說明:技能要求:B級B項基本熟悉各種元件封裝以及基本腳位定義等考題要求:說明十個各不相同元件的名稱與特點,由考核者在公司電腦中抓取新建一個線路圖,抓取十個有特殊腳位定義封裝,更改PIN定義與PIN連接訊號後,請考核者CHECK並改爲正確定義。

考核標准:按考核題目要求抓取十個各不相同元件,要求全部正確,如對所抓元件有疑問可另行說明,如所抓取元件錯誤,此項不通過(元件抓取錯誤但有說明合理原因除外)按考核題目要求對十個PIN定義錯誤元件進行更改,如對元件PIN定義有疑問可另行說膽,如更改後PIN定義還是錯誤,此項不通過(更改後PIN定義錯誤, 但有說明合理原因除外)說明:抓取正確的元件封裝與新建元件同樣重要,故不允許出錯。

如說明原因不容易界定者可安排重考。

附1: 集成电路封装说明: DIP封装DIP封装(Dual In-line Package),也叫双列直插式封装技术,指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100。

DIP封装的IC芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。

DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏管脚。

DIP封装结构形式有:多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP(含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等。

DIP封装具有以下特点: 1.适合在PCB(印刷电路板上穿孔焊接,操作方便。

2.芯片面积与封装面积之间的比值较大,故体积也较大 QFP封装中文含义叫方型扁平式封装技术(Plastic Quad Flat Pockage),该技术实现的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

该技术封装IC时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT表面安装技术在PCB上安装布线 PGA封装中文含义叫插针网格阵列封装技术(Ceramic Pin Grid Arrau Package),由这种技术封装的芯片内外有多个方阵形的插针,每个方阵形插针沿芯片的四周间隔一定距离排列,根据管脚数目的多少,可以围成2~5圈。

安装时,将芯片插入专门的PGA插座。

该技术一般用于插拔操作比较频繁的场合之下 BGA封装BGA技术(Ball Grid Array Package)即球栅阵列封装技术。

该技术的出现便成为CPU、主板南、北桥芯片等高密度、高性能、多引脚封装的最佳选择。

但BGA封装占用基板的面积比较大。

虽然该技术的I/O引脚数增多,但引脚之间的距离远大于QFP,从而提高了组装成品率。

而且该技术采用了可控塌陷芯片法焊接,从而可以改善它的电热性能。

另外该技术的组装可用共面焊接,从而能大大提高封装的可靠性;并且由该技术实现的封装IC信号传输延迟小,适应频率可以提高很大。

BGA封装具有以下特点: 1.I/O引脚数虽然增多,但引脚之间的距离远大于QFP封装方式,提高了成品率 2.虽然BGA的功耗增加,但由于采用的是可控塌陷芯片法焊接,从而可以改善电热性能 3.信号传输延迟小,适应频率大大提高 4.组装可用共面焊接,可靠性大大提高附2:元件實物圖图表 SEQ 图表 \* ARABIC 1 TSSOP 图表 SEQ 图表 \* ARABIC 2 TSOP 图表SEQ 图表 \* ARABIC 3 to-220 图表 SEQ 图表 \* ARABIC 4 TO263 图表 SEQ 图表\* ARABIC 5 TO92 图表 SEQ 图表 \* ARABIC 6 TO18 图表 SEQ 图表 \* ARABIC 7 SSOP 图表 SEQ 图表 \* ARABIC 8 SOT523 图表 SEQ 图表 \* ARABIC 9 SOT343 图表 SEQ 图表 \* ARABIC 10 SOT252 图表 SEQ 图表 \* ARABIC 11 SOT223 图表SEQ 图表 \* ARABIC 12 SOT143 图表 SEQ 图表 \* ARABIC 13 sot89 图表 SEQ 图表 \* ARABIC 14 sot26 图表 SEQ 图表 \* ARABIC 15 sot23 图表 SEQ 图表 \* ARABIC 16 SOT23-5 图表 SEQ 图表 \* ARABIC 17 SOP 图表 SEQ 图表 \* ARABIC 18 SOJ 图表 SEQ 图表 \* ARABIC 19 SOCKET603 图表 SEQ 图表 \* ARABIC 20 SO 图表 SEQ 图表 \* ARABIC 21 SIP 图表 SEQ 图表 \* ARABIC 22 SDIP 图表 SEQ 图表 \* ARABIC 23 QFP 图表 SEQ 图表 \* ARABIC 24 PQFP 图表 SEQ 图表 \*ARABIC 25 PLCC 图表 SEQ 图表 \* ARABIC 26 PGA 图表 SEQ 图表 \* ARABIC 27 PGA 图表 SEQ 图表 \* ARABIC 28 HSOP 图表 SEQ 图表 \* ARABIC 29 DIP-DIP_TAB 图表 SEQ 图表 \* ARABIC 30 CNR 图表 SEQ 图表 \* ARABIC 31 CLCC 图表 SEQ 图表 \* ARABIC 32 BGA 图表 SEQ 图表 \* ARABIC 33 BEAD 图表 SEQ 图表 \* ARABIC34 168-DIMM ***[JimiSoft: Unregistered Software ONLY Convert Part Of File! Read Help To Know How To Register.]***。