半导体工艺及器件模拟一

- 格式:ppt

- 大小:1.57 MB

- 文档页数:138

主要内容2.12.22.32.1 器件模拟的基本方程组2.1.3 载流子输运的基本方程2.1.3.2小尺寸半导体器件的载流子输运方程(a) (b)图2.1 半导体中的载流子过冲. (a) GaAs材料, (b) Si材料2.1 器件模拟的基本方程组2.1.6光波导方程由Maxwell 方程组同样可以导出在半导体材料中传输的光波的电场分量E 所满足的方程:式中n 为材料的折射率,k 0 =2π/λ,λ是波长。

对于沿z 方向传播的波,式中β是波沿z 方向的传播常数,可得到Helmholtz 方程为,2022=+∇E E k n )(exp ),,(),,,(z t j E E E t z y x z y x βω−=E 222/,/ββ−=∂∂−=∂∂z j z 所以,)(22022=−+∇E E βk n T 式中,22222//y x T ∂∂+∂∂=∇2.3 半导体器件的分级模拟2.3.1 问题目的提出判断一个半导体器件模拟软件优劣的指标是功能全、精度高、速度快和便于用户使用。

功能全主要指能处理问题面广,便于用户使用则主要指程序输入参数形式简单,并以交互或对话方式工作。

实际开发半导体器件模拟软件时要考虑这两点,但这不是衡量半导体器件模拟方法本身优劣的指标。

衡量半导体器件模拟方法优劣的指标是速度快、精度高。

在半导体器件的计算机模拟中,除了从指标要求出发选取好的方法外,在给定精度的条件下,还经常使用分级模拟技术以减少计算时间和提高计算速度。

2.3 半导体器件的分级模拟2.3.3 分级模拟的意义随着工件条件的变化,模型方程的复杂性越来越高,相应地,模拟的复杂性也越来越高。

对于复杂的模拟问题,往往需要采用分级模拟的方法,该方法包括两点:(1)根据具体的工作条件,选用级别较低的模型方程,以在保证精度的条件下大大减少计算时间。

(2)利用低一级的解作为初值。

由于低一级的解是本级的很好近似,这样做将有效减少计算时间。

请简述半导体器件工艺的十大流程半导体器件工艺是制造半导体器件的工艺流程,是半导体工程领域的重要组成部分。

半导体器件工艺流程包括十大流程,分别是晶圆生长、晶圆切割、清洁和清洗、化学氧化、物理氧化、光刻、蚀刻、沉积、离子注入和退火。

下面将详细介绍这十大流程。

首先是晶圆生长。

晶圆生长是制备半导体材料的第一步,也是半导体器件制造的基础。

它是利用化学气相沉积技术在单晶衬底上生长出高质量的半导体材料晶体。

晶圆生长的材料通常是硅、砷化镓等半导体材料。

其次是晶圆切割。

晶圆切割是将生长好的半导体晶体切割成一定大小的薄片,这些薄片被称为晶片。

晶圆切割的精度和质量直接影响到后续工艺的成功与否。

接着是清洁和清洗。

这一步是为了去除晶片表面的杂质和污染物,保证后续工艺的顺利进行。

清洁和清洗通常采用多种化学试剂和超声波清洗等方法。

然后是化学氧化和物理氧化。

化学氧化和物理氧化是为了在晶片表面形成一层氧化物膜,以保护晶片表面并提供绝缘层,以便后续形成电路结构。

接下来是光刻。

光刻是一种非常重要的半导体器件制造工艺,它通过选择性照射光源和光刻胶的方式,在晶片表面形成所需的图案。

这是制造半导体器件电路结构的关键步骤。

然后是蚀刻。

蚀刻是利用化学或物理方法去除光刻胶未被照射的部分,从而形成所需的图案。

蚀刻的精度和准确度对电路的性能和稳定性有着很大的影响。

接着是沉积。

沉积是将金属、氧化物等材料以化学气相沉积或物理气相沉积的方式沉积在晶片表面,形成电路结构所需的电极、导线和绝缘层等材料。

然后是离子注入。

离子注入是将掺杂剂以离子束的方式注入晶片内部,改变晶片的电学性能,以形成所需的电子器件。

最后是退火。

退火是通过加热晶片,以改变晶体结构和去除注入后的损伤,提高器件的性能和稳定性。

以上就是半导体器件工艺的十大流程。

这些流程相互关联,缺一不可,任何一步出现问题都会影响整个器件的性能和稳定性。

因此,在实际生产中,需要严格控制每一个环节,不断优化工艺流程,不断提高制造技术水平,以满足市场需求和技术发展的要求。

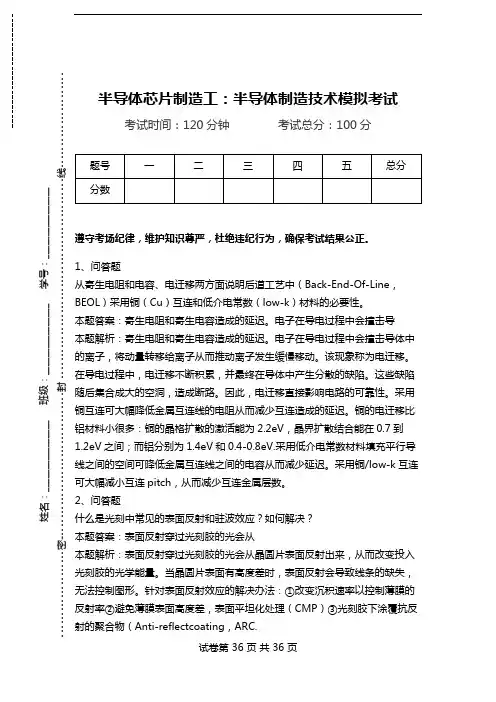

半导体芯片制造工:半导体制造技术模拟考试 考试时间:120分钟 考试总分:100分遵守考场纪律,维护知识尊严,杜绝违纪行为,确保考试结果公正。

1、问答题 从寄生电阻和电容、电迁移两方面说明后道工艺中(Back-End-Of-Line ,BEOL )采用铜(Cu )互连和低介电常数(low-k )材料的必要性。

本题答案:寄生电阻和寄生电容造成的延迟。

电子在导电过程中会撞击导 本题解析:寄生电阻和寄生电容造成的延迟。

电子在导电过程中会撞击导体中的离子,将动量转移给离子从而推动离子发生缓慢移动。

该现象称为电迁移。

在导电过程中,电迁移不断积累,并最终在导体中产生分散的缺陷。

这些缺陷随后集合成大的空洞,造成断路。

因此,电迁移直接影响电路的可靠性。

采用铜互连可大幅降低金属互连线的电阻从而减少互连造成的延迟。

铜的电迁移比铝材料小很多:铜的晶格扩散的激活能为2.2eV ,晶界扩散结合能在0.7到1.2eV 之间;而铝分别为1.4eV 和0.4-0.8eV.采用低介电常数材料填充平行导线之间的空间可降低金属互连线之间的电容从而减少延迟。

采用铜/low-k 互连可大幅减小互连pitch ,从而减少互连金属层数。

2、问答题 什么是光刻中常见的表面反射和驻波效应?如何解决? 本题答案:表面反射穿过光刻胶的光会从 本题解析:表面反射穿过光刻胶的光会从晶圆片表面反射出来,从而改变投入光刻胶的光学能量。

当晶圆片表面有高度差时,表面反射会导致线条的缺失,无法控制图形。

针对表面反射效应的解决办法:①改变沉积速率以控制薄膜的反射率②避免薄膜表面高度差,表面平坦化处理(CMP )③光刻胶下涂覆抗反射的聚合物(Anti-reflectcoating ,ARC.姓名:________________ 班级:________________ 学号:________________--------------------密----------------------------------封 ----------------------------------------------线----------------------驻波效应在微细图形光刻时,一般曝光光源为单色或窄带光源,在由基片、氧化物层和抗蚀剂等组成的多层膜系情况下,由于膜系各层折射率不同,曝光时在基底表面产生的反射光和入射光相互干涉而形成驻波。

电子学中的半导体器件设计与模拟在当今科技快速发展的时代,半导体器件作为电子学的重要组成部分,扮演着至关重要的角色。

半导体器件的设计与模拟技术的研究与应用,不仅直接影响着电子产品的性能和稳定性,也对整个电子行业的发展起到了关键推动作用。

本文将深入探讨电子学中的半导体器件设计与模拟技术,带领读者进入这一神秘而又具有巨大潜力的领域。

一、半导体器件的基本原理与分类半导体器件是利用半导体材料的特性,通过在其内部添加杂质或者构造特殊结构来实现特定功能的电子器件。

根据不同的原理和功能,半导体器件可以分为多种类型,比如二极管、晶体管、场效应管、可控硅等等。

这些器件在电子设备中发挥着不同的作用,相互之间有着协同配合的关系。

二、半导体器件设计的基本流程半导体器件的设计是一个复杂而严密的流程,需要经过多个步骤才能最终得到满足要求的器件。

常见的半导体器件设计流程如下:1. 规格和需求确定:根据具体的应用场景和功能要求,确定半导体器件的性能规格和工作参数。

2. 材料选择:根据应用要求和器件特性,选择适合的半导体材料,如硅(Si)、砷化镓(GaAs)等。

3. 结构设计:根据器件类型和功能要求,设计合适的器件结构,包括材料层次、接触结构和电极等。

4. 工艺流程制定:根据器件结构,确定相应的工艺流程,包括材料生长、掺杂、光刻、蚀刻等工序。

5. 设计验证与模拟:利用电子设计自动化(EDA)软件进行电路仿真和参数验证,确保设计的正确性和可行性。

6. 器件制作与测试:根据设计和验证结果,利用微纳制造技术制作半导体器件,然后进行电学和物理性能测试。

7. 优化与改进:根据测试结果,对器件进行分析,并通过优化和改进,使其性能和稳定性达到预期要求。

三、半导体器件模拟的重要性在半导体器件设计的过程中,模拟技术扮演着重要的角色。

半导体器件模拟能够通过数值计算和仿真,预测器件在特定工作条件下的电学和物理特性,为设计优化提供有力支持。

通过模拟,可以提前发现问题和缺陷,减少实际制造和测试的错误成本,提高设计效率和品质。

第一章工艺和器件发展概述1947年第一只具有放大作用的点接触晶体管问世,与电子管相比具有很多优点,引起人们广泛注意,在随后的十几年时间相继发明了各式各样晶体管(合金管、合金扩散管、台面管等)。

1960年硅平面工艺和外延技术的出现,使半导器件的制造工艺获得重大突破。

它为集成电路的制造开拓了广阔的途径,促进了半导体器件进一步向微型化、低功耗和高可靠性方向发展。

集成度由SSI、MSI、LSI、VLSI步入了ULSI时代。

1957年第一只SCR问世以来功率器件也取得了长足的进步,相继推出了GTO(可关断晶闸管)TRIAC(双向晶闸管)和GTR(达林顿功率晶体管)这些都是双极型器件,它们共同优点是功率容量大,导通电阻小,缺点是存在少子贮存效应,开关速度低,电流驱动,驱动功率大,不易控制,七十年末由IR和GE公司发明了单极型功率器件功率MOSFET,立即受到制造厂和用户的重视。

三年后西方15家大公司均掌握了功率MOSFET生产技术(VDMOS),1983年诞生了IGBT双极型器件。

半导体器件种类繁多,工艺有别,本次培训主要以外延平面工艺为主,介绍以下内容:单晶硅拉制及衬底制备、外延工艺、氧化工艺、扩散与离子注入工艺、光刻工艺、蒸发工艺、芯片组装工艺。

一、锗合金扩散晶体管制造工艺流程简介合金扩散晶体管是五十年代中期发展起来的一种高频管。

工艺流程:切片→研磨、抛光、腐蚀→扩散(Sb扩)→装发射极(In合金)→真空烧结(500~550℃)→装基极及支架→烧结(H2)→点焊管座→拉丝→涂保护油→台面腐蚀→去油清洗→管芯腐蚀→烘干→涂胶→封管二、硅外延平面晶体管制造工艺流程(NPN型)三、集成电路制造工艺流程原始硅片 P型(衬底) ρ:8-13Ω·cm 晶面(111)比平面晶体管多出工艺隐埋(埋层)扩散,隔离扩散。

四、肖特基二极管芯工艺工艺势垒金属结温 VF IRVR标准工艺 Mo-Si化合物 150℃低适中≤60V830工艺 Pd-Si化合物+Mo 175℃高低≤200VCr Cr-Si化合物+Mo 125℃很低高≤45VV V-Si化合物 100℃极低很高≤45V 管芯工艺流程见附图五、IGBT工艺流程 IGBT、MOSFET芯片结构详见附图第二章单晶拉制与衬底制备半导体单晶是制造半导体器件的基础材料,它的质量好坏直接影响到半导体器件的性能。