基于原理图的模100BCD码计数器设计

- 格式:pdf

- 大小:1.50 MB

- 文档页数:14

用74160集成计数器构成任意进制计数器的电路设计单嵛琼;单长吉【摘要】74160 is die for 10 synchronous counter addition,take advantage of its reset and the number of pre-set function can make mould for any number of counters.So as to solve the problem that we can't buy any kind of counter.%74160是模为10的同步加法计数器,利用它的清零和预置数功能可以构成模为任意数的计数器,从而解决了我们需要计数器但市场上又买不到这种计数器的困难。

【期刊名称】《大学物理实验》【年(卷),期】2016(029)003【总页数】3页(P15-17)【关键词】计数器;清零;置数;有效状态【作者】单嵛琼;单长吉【作者单位】昭通学院,云南昭通 657000;昭通学院,云南昭通 657000【正文语种】中文【中图分类】O453市场上能买到的集成计数器芯片一般为4位二进制计数器和十进制计数器,如果需要其它进制计数器,可用现有的4位二进制计数器和十进制计数器芯片进行设计。

74160是8421BCD码同步加法十进制计数器,可以用它来构成任意进制计数器。

74160是8421BCD码同步加法计数器[1-2],图1是它的逻辑符号:是清零端,端是预置数端,EP、ET是两个使能端,CP端是时钟脉冲端,RCO是进位输出端,D3、D2、D1、D0是四个预置数据输入端,Q3、Q2、Q1、Q0是四个数据输出端。

其中进位输出端的逻辑表达式为[3]:RCO=ET·Q3·Q1。

由表1可知,74160具有异步清零、同步置数、计数和保持的功能。

用74160构成模小于10的计数器的计数器时通常有两种方法:异步清零法和同步置数法[4].文章中选取用74160构成五进制计数器来说明这两种方法的应用。

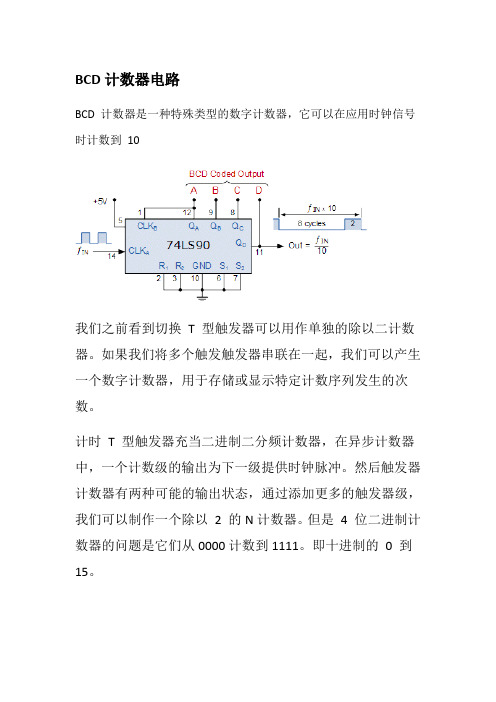

BCD计数器电路BCD 计数器是一种特殊类型的数字计数器,它可以在应用时钟信号时计数到10我们之前看到切换T 型触发器可以用作单独的除以二计数器。

如果我们将多个触发触发器串联在一起,我们可以产生一个数字计数器,用于存储或显示特定计数序列发生的次数。

计时T 型触发器充当二进制二分频计数器,在异步计数器中,一个计数级的输出为下一级提供时钟脉冲。

然后触发器计数器有两种可能的输出状态,通过添加更多的触发器级,我们可以制作一个除以 2 的N计数器。

但是 4 位二进制计数器的问题是它们从0000计数到1111。

即十进制的0 到15。

要制作一个从 1 到10 计数的数字计数器,我们需要让计数器只计算二进制数0000到1001。

那是十进制的0 到9,对我们来说幸运的是,计数电路很容易作为集成电路使用,其中一个这样的电路是异步74LS90 十进制计数器。

数字计数器在应用时钟信号时从零向上计数到某个预定计数值。

一旦达到计数值,重置它们会将计数器返回到零以重新开始。

十进制计数器按10 的顺序计数,然后在计数到9 后返回零。

显然,要计数到二进制值9,计数器必须在其链中至少有四个触发器来表示每个十进制数字,如图所示。

BCD 计数器状态图然后十进制计数器有四个触发器和16 个潜在状态,其中只使用了10 个,如果我们将一系列计数器连接在一起,我们可以计数到100 或1,000 或我们选择的任何最终计数数字。

计数器也可以计数的总数称为它的MODULUS。

在n 次计数后返回零的计数器称为模n 计数器,例如模8 (MOD-8) 或模16 (MOD-16) 计数器等,对于“n 位计数器” ”,计数的全范围是从0到2n-1。

但正如我们在异步计数器教程中看到的那样,一个计数器在十次计数后重置,从二进制0000(十进制“0”)到1001(十进制“9”)的除以10 计数序列被称为“二进制-coded-decimal counter”或简称BCD Counter和一个MOD-10 计数器可以使用最少四个触发触发器来构建。

附录一:基于原理图的模100BCD码计数器的设计1目的:1)练习用原理图输入设计;2)如何用数码管和二极管显示设计;3)如何仿真;4)如何绑定管脚。

2过程2.1新建原理图文件。

点击file->new->block diagram file->OK,如图2-1,图2-2,出现图2-3。

图2-1 新建文件。

点击file->new。

图2-2 新建原理图文件。

点击block diagram file->OK。

图2-3. 原理图设计输入区域。

双击工作区域。

图2-4 宏单元输入界面。

点击Library下的+。

图2-5 选用宏单元。

键入74160。

2.2 输入设计。

双击图2-3的工作区,出现图2-4。

在+megafunctions,+others,+primitives中寻找需要的宏单元。

也可在Name下输入知道名字的宏单元,如“74160”,“GND”,“VCC”等,如图2-5。

输入设计,如图2-6。

存盘为m100_jishuqi,如图2-7。

图2-6 模100BCD码计数器。

图2-7 保存文件。

2.2为本设计建立工程,并放在文件夹..\m100_jishuqi\中。

在图2-7中点击是(或点击file->newproject)出现图2-8;点击next,出现图2-9;输入工程名字和顶层设计名字;点击next,出现图2-10,加入设计文件;点击next,出现图2-11,选择器件(cycloneII系列EP2C70F896C6);点击next->next->finish。

图2-8 新建工程。

点击Next。

图2-9 输入工程名字和顶层设计名字:mo100_jishuqi。

图2-10 把设计文件加入工程。

图2-11 选择器件:cycloneII系列EP2C70F896C6。

2.3把FPGA没有用到的引脚设定为 as input tri-stated。

点击assignment->device,如图2-12;点击Device and Pin Options,如图2-13所示,把Unused Pins设定为as input tri-stated。

《电气工程及其自动化EDA课程设计》课程设计报告\题目:数字频率计的设计院(系):机电与自动化学院专业班级:电气工程及其自动化学生姓名: XXX学号: 2011XXXXXXX指导教师: XXX 】2014年1月6日至2014年1月10日#华中科技大学武昌分校《电气工程及其自动化EDA课程设计》设计任务书(目录摘要 (1)一.课程设计要求及内容 (1)主要技术指标 (1)工作内容及要求 (1)二数字频率计的基本原理 (1)数字频率计的组成 (1):数字频率器的原理 (2)三具体电路模块设计 (2)100MHz分频器 CLK_GEN的设计 (2)带时钟使能的十进制计数器CNT10的设计 (3)32位锁存器REG32B的设计 (5)测频控制信号发生器TESTCTL的设计 (6)动态输入编译译码器HC4511的设计 (7)四数字频率计系统模块的设计 (9)>系统模块程序设计及仿真波形 (9)数字频率计系统顶层设计 (10)五心得体会 (13)课程设计成绩评定表 (14)(摘要数字频率计是一种用十进制数字显示被测信号频率的一种数字测量仪器,其功能是测量正弦信号,方波信号,尖脉冲信号以及其他各种单位时间内变化的物理量,因此已经成为电路设计的常用元器件之一,有它不可替代的地位。

在电子技术中,频率与许多电参量的设计测量方案,测量结果都有着十分紧密的关系,因此频率的测量就显得更为重要。

测量频率的方法有很多种,其中数字计数器测量频率具有精度高,使用方便,测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

其原理为通过测量一定闸门时间内信号的脉冲个数。

本文阐述了利用VHDL语言在CPLD器件的基础上设计一个简单的数字频率计的过程。

采用VHDL编程技术设计实现的数字频率计,除被测信号的整形部分,键输入部分和数码显示部分以外,其余全部在一片集成电子芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

实验二 文本输入方式设计数字逻辑电路一、实验目的:1、 掌握VHDL 语言的基本语法和设计文件的基本结构。

2、 掌握组合逻辑电路的特性及设计和调试方法。

3、 掌握时序逻辑电路的特性及设计和调试方法。

4、 掌握常用的组合逻辑电路和时序逻辑电路的设计方法。

二、实验的硬件要求:1、 EDA/SOPC 实验箱。

2、 计算机。

三、实验原理数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。

组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。

时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。

1、组合逻辑电路①组合逻辑电路的定义通常组合逻辑电路可以用图1.1所示结构来描述。

其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm 为输出信号。

输入和输出之间的逻辑函数关系可用式1.1表示: ②组合逻辑电路的设计方法组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。

理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。

在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。

设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。

组合电路的基本设计步骤可用图1.2来表示。

③组合逻辑电路的特点及设计时的注意事项a)组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。

(实际电路中图 2.1 组合逻辑电路框图L0=F0(X0,X1,···Xn) · · ·Lm=F0(X0,X1,···Xn)(1.1)图 2.2 组合电路设计步骤示意图图还要考虑器件和导线产生的延时)。

BCD码与计数器二-十进制BCD码:1、概念:BCD码是用一组四位二进制数码来表求一位十进制数的编码2、四位二进制数码有16种组合其中合法的就以下十组:0:00001:00012:00103:00114:01005:01016:01107:01118:10009:1001以下是不合法:1010,1011、1100、1101、1110、1111计数器我们高考的时候数电里面的最后大题会是15分,基本上是考计数器重点:如何判断几进制?如何去判断考试的题目是四位二进制计数器还是十进制计数器?还是九进制计器?还是八进制计数器?还是5进制计数器?还是N进制计数器?1、已以解决十进制计数器的判断2、在触发器构成的电路中,一个触发器表示一位数字。

所以四位二进制计数器需要四个触发器。

那么十进制计数器需要几个触发器?好的!大家都说四个,对的那么如果考试的时候电路当中只出现三个触发器,就不可能去判断是十进制计数器3、如何判断电路是不是二进制计数器2位:00-01-10-11-00(二位二进制加法)(四种组合中途没有归0过)3位:000-001-010-011-100-101-110-111-000(三位二进制加法)(八种组合中途没有归0过)4位:0000-0001-。

-1001-1010-。

1111-0000(四位二进制加法计数器)(十六种组合中途没有归0过)判断以下情况是几进制:1、0000-0001、、、、-1010-0000?2、0000-0001、、、、-1110-0000?3、000-110-、、、-101-000?8421-BCD码:8421是什么意思?代表每一位上的权OK所以我们把这一类编码称为有权码。

有权码是不是8421-BCD码一样呢?有权码:1、8421-BCD码2、2421-BCD码3、5421-BCD码以上3种编码都可以来表示一位十进制数0-9对于我们中职学生来说,我们只要掌握8421-BCD码就行了OK了8:10008421,11102421-BCD,10115421-BCD 7: 01118421 11012421-BCD,01112421-BCD逻辑函数的化简:(高考填空题)我们学习的数电应用主要在于两方面的应用1、组合逻辑电路的应用2、时序逻辑电路应用那么我们高考会是什么形式出现?1、给你一个任务单,叫你设计一个能够实现任务功能的电路2、给你一个电路图,叫你分析这个电路它能实现什么功能。

60秒计数器摘要60秒计数器作为一种工具,可以用来计时、定时,如用在定时炸弹。

本设计是以60秒计数器为基本理念。

利用AT89C52单片机及外围接口实现的计时系统,利用单片机的定时器/计数器定时和记数的原理,将软、硬件有机地结合起来,使得系统能够正确地进行计时,同时使数码管能够正确地显示时间,扬声器发生提示。

关键词:AT89C52 数码管计时报警1.任务与要求设计并制作一个BCD码显示60秒计数器,并实现00-01-…60-00-…计数。

当计数到60秒时,报警1秒,并停留显示在60秒状态。

复位后才恢复到00状态。

2.计时原理定时计数器工作方式2(M1M0=10)M1M0=10时,定时器T0和T1设置为能自动重装计数器初值的8位定时/计数器工作方式2,计数器的计数值由下式确定:N=28-x=256-x计数范围为1—256。

定时器的定时值由下式确定:t=N×T=(256-x)T如果晶体振荡器频率fosc=12MHz,则T=1us,定时范围为1—256us;若晶体振荡器频率fosc=6MHz,则T=2us,定时范围为1—512us。

3 硬件电路分析硬件如上路,与P0。

0,接的是开始开关,与P0。

1接的是蜂鸣器,与P3。

0连接的LED用于模拟秒闪信号,与P2口连接的BCD数码管显示个位,与P1口连接的BCD数码管显示十位,BCD数码管为共阴极。

4 秒信号发生器设计首先设置方式字:TMOD=00000010B计算计数初值:方式2的最大定时为512us,要产生1秒的定时用多次溢出才能实现;(256-X)*T*N=t 其中,T=2us,t=1s取X=250,则N=2000,溢出次数2000超过了255,因此要用至少两个计数器作为溢出次数计数器。

即:N=n1*n2其中,n1和n2必须为小于255的整数,可以取n1=50,n2=40n1=100,n2=20n1=200,n2=10n1=250,n2=8由于任务中要求有一个秒闪信号,因此我们采用三个计数器作为溢出次数计数器,即N=n1*n2*n3=2*20*505 复位电路的设计单片机的第9脚RST为硬件复位端,只要将该端持续4个机器周期的高电平即可实现复位,复位后单片机的各状态都恢复到初始化状态,其电路图如图6所示:图6 复位电路图6中由按键RESET1以及电解电容C3、电阻R2构成按键及上电复位电路。

二位bcd码计数器电路工作原理二位BCD码计数器电路工作原理引言:二进制编码十进制(Binary-Coded Decimal,简称BCD)是一种常用的数据表示方法,将十进制数的每一位都用4位二进制数表示,称为BCD 码。

BCD码计数器电路是一种常见的计数器电路,用于计数和显示十进制数字。

本文将详细介绍二位BCD码计数器电路的工作原理,并逐步回答有关该主题的问题。

第一步:什么是BCD码?BCD码是一种使用4位二进制数表示一个十进制数的编码方式。

在BCD 码中,每一位二进制数的取值范围为0000到1001,分别对应十进制的0到9。

由于使用了4位二进制数,BCD码的每一位可以使用一位数码管进行显示。

第二步:二位BCD码计数器电路的结构二位BCD码计数器电路包含两个独立的计数器模块,每个模块负责计数和显示一个十进制位数。

两个计数器模块之间通过电路连接,共享一个时钟信号。

第三步:每个计数器模块的结构和工作原理每个计数器模块通常由三个主要组件构成:计数器、锁存器和数码管显示。

- 计数器:计数器用于存储当前的BCD码值,并根据时钟信号的输入进行计数。

计数器模块中的每个计数器可以存储4位BCD码值,所以可以表示0到9的十进制数。

- 锁存器:锁存器用于在计数完成时保存最后一个计数器的值,以便在下一个计数周期开始时将其作为时钟信号的输入传递给下一个计数器。

- 数码管显示:每个计数器模块都包含一个数码管用于显示当前计数器的值。

数码管显示可以通过将BCD码转换为对应的数码管段亮灭来实现。

第四步:工作原理1. 初始化:当启动计数器电路时,需要将计数器模块中的计数器值初始化为0。

2. 计数:计数器模块根据时钟信号的输入进行计数。

一般情况下,计数器通过下降沿触发进行计数。

每个计数器从0开始计数,当计数器的值达到9时,它会自动归零并将进位信号传递给下一个计数器。

3. 锁存:当一个计数周期结束时,锁存器会将最后一个计数器的值保存下来,并在下一个计数周期的开始时将其作为时钟信号的输入传递给下一个计数器。

附录一:基于原理图的模100BCD码计数器的设计

1目的:1)练习用原理图输入设计;2)如何用数码管和二极管显示设计;3)如何仿真;4)如何绑定管脚。

2过程

2.1新建原理图文件。

点击file->new->block diagram file->OK,如图2-1,图2-2,出现图2-3。

图2-1 新建文件。

点击file->new。

图2-2 新建原理图文件。

点击block diagram file->OK。

图2-3. 原理图设计输入区域。

双击工作区域。

图2-4 宏单元输入界面。

点击Library下的+。

图2-5 选用宏单元。

键入74160。

2.2 输入设计。

双击图2-3的工作区,出现图2-4。

在+megafunctions,+others,+primitives中寻找需要的宏单元。

也可在Name下输入知道名字的宏单元,如“74160”,“GND”,“VCC”等,如图2-5。

输入设计,如图2-6。

存盘为m100_jishuqi,如图2-7。

图2-6 模100BCD码计数器。

图2-7 保存文件。

2.2为本设计建立工程,并放在文件夹..\m100_jishuqi\中。

在图2-7中点击是(或点击file->newproject)

出现图2-8;点击next,出现图2-9;输入工程名字和顶层设计名字;点击next,出现图2-10,加入设计文件;点击next,出现图2-11,选择器件(cycloneII系列EP2C70F896C6);点击

next->next->finish。

图2-8 新建工程。

点击Next。

图2-9 输入工程名字和顶层设计名字:mo100_jishuqi。

图2-10 把设计文件加入工程。

图2-11 选择器件:cycloneII系列EP2C70F896C6。

2.3把FPGA没有用到的引脚设定为 as input tri-stated。

点击assignment->device,如图2-12;点击

Device and Pin Options,如图2-13所示,把Unused Pins设定为as input tri-stated。

图2-12 assigments->device设置

图2-13 assigments->device->Device and Pin Options->Unused Pins设置

2.5 编译本设计。

点击processing->start compilation,进行全编译。

2.6 波形仿真—输入波形文件。

点击file->new->vector waveform file,如图2-14;点击ok,双击工作界面,出现图2-15;点击Node Finder,出现图2-16;过滤器Filter选择Pins Input,点击List,并点击“>>”,选择全部输入信号,如图2-16(也可以点击某个输入信号,如clk,用>选择该输入信号);过滤器Filter选择Pins Output,点击List,显示所有输出信号,如图2-17;分别点击shiwei,>,gewei,>,就选出了输出信号shiwei[3:0]和gewei[3:0],如图2-18;点击ok->ok,出现图2-19;利用放大镜(zoom tool)把波形缩放到合适的大小(点击放大镜,点击鼠标左键是放大波形;点击鼠标右键是缩小波形);至此完成波形文件的输入输出信号选择。

点击输入信号clk,再点击时钟图标,如图2-20,把时钟周期改为20ns;点击ok,出现了输入信号clk的波形,如图2-21;点击信号clr,再点击“1”小图标,clr变高电平,如图2-22,再按下鼠标左键,框选clr信号的前40ns,然后点击“0”小图标,使得clr的前40ns为低电平,如图2-22;至此完成输入波形的输入。

点击file->save,如图2-23,波形文件名和文件夹用缺省的,点击“保存(S)”。

2.7波形仿真—查看仿真波形。

功能仿真。

点击菜单processing->simulator tool,出现图2-24;选择simulation mode为functional,点击“generate functional simulation netlist”,如图2-24;点击start,ok,再点击open观查仿真结果,如图2-25。

从波形图看出,仿真波形正确,但只能计数到49。

要看到完整的仿真,应把仿真时间总长从1us改为10us,方法是:点击菜单Edit->End Time,把1us改为10us,如图2-26,点击ok;从新做仿真,可以看到图2-27的结果。

时序仿真。

点击菜单processing->simulator tool,选择simulation mode为timing,点击start,ok,

再点击open观查仿真结果。

图2-14 新建波形文件。

点击ok。

图2-15 波形文件输入窗口。

图2-16 选择波形文件的输入信号

图2-17显示波形文件的输出信号

图2-18选择波形文件的输出信号

图2-19 波形文件(已经有了输入输出信号)

图2-20 设置输入时钟clk的周期

图2-21 完成了的clk输入波形

图2-22 完成了的clr输入波形

图2-23 保存波形文件

图2-24 功能仿真设置

图2-25 功能仿真波形

图2-26 修改仿真时间的长度

图2-27 延长仿真时间后的结果

2.8管脚绑定。

管脚绑定的任务就是要把设计中需要的输入信号绑定到指定的FPGA引脚,使得可以从外部器件得到输入信号;把设计中的输出信号绑定到指定的FPGA引脚,以达到控制外部器件的目的。

打开文件DE2_70_pin_assignments.csv,如图2-28。

图中的B列表示器件的类型及其具体的信号名号,如iCLK_28表示28M的外部时钟的输入端;iAUD_ADCDAT表示音频接口的ADCDAT信号输入端;oHEX0_D[0]表示输出到数码管0的a端;iKEY[0]表示第一个轻触键的输入端;oLEDR[0]表示输出到第1个红色发光二极管的端子。

图中列D表示列B中的信号已经连接到了FPGA的对应的引脚。

管脚绑定的任务就是把设计中的输入输出信号绑定到DE2_70_pin_assignments.csv文件列D对应的引脚,具体如图2-29所示。

具体操作是打开assigments->pins来进行。

输入信号clk的绑定。

把iKey[0]作为clk的输入,即把clk绑定到iKey[0]上:查

DE2_70_pin_assignments.csv,iKey[0]对应FPGA的PIN_T29,所以在assigments->pins中找到clk,并把其location设为PIN_T29;

输入信号clr_n的绑定。

把iSW[0]作为清零健,即把clr_n绑定到iSW[0]上:查

DE2_70_pin_assignments.csv,iSW[0]对应FPGA的PIN_AA23,所以在assigments->pins中找到clk,

并把其location设为PIN_AA23;

其它信号的绑定方法相似。

2.9 重新编译整个设计。

2.10 下载设计。

点击Tools->Programmer,如图2-30。

点击Start即可下载设计。

2.11 观测结果。

按下开发板中的KEY0键,观测数码管有和变化。

不断按下KEY0,再看结果。

3 注意事项

1)以上的设计是模100计数器。

2)上文红色字的设置一定要做好,否则不要下载设计。

图2-28 DE2_70_pin_assignments.csv文件

图2-29 输入输出信号引脚的绑定

图2-30 Programmer界面。