计数器接线图

- 格式:pdf

- 大小:72.21 KB

- 文档页数:1

计数器一实验目的1、掌握中规模集成计数器的逻辑功能及使用方法。

2、学习运用集成电路芯片计数器构成N位十进制计数器的方法。

二实验原理计数器是一个用以实现计数功能的时序器件,它不仅可以用来记忆脉冲的个数,还常用于数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多,按构成计数器中的各个触发器输出状态更新是否受同一个CP脉冲控制来分,有同步和异步计数器,根据计数制的不同,分为二进制、十进制和任意进制计数器。

根据计数的增减趋势分,又分为加法、减法和可逆计数器。

另外,还有可预置数和可编程功能的计数器等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器芯片。

如:异步十进制计数器74LS90,4位二进制同步计数器74LS93,CD4520,4位十进制计数器74LS160、74LS162;4位二进制可预置同步计数器CD40161、74LS161、74LS163;4位二进制可预置同步加/减计数器CD4510、CD4516、74LS191、74LS193;BCD码十进制同步加/减计数器74LS190、74LS192、CD40192等。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列就能正确使用这些器件。

例如74LS192同步十进制可逆计数器,具有双时钟输入十进制可逆计数功能;异步并行置数功能;保持功能和异步清零功能。

74192功能见表表19.1*表中符号和引脚符号的对应关系:CR = CLR—清零端;LD= LOAD—置数端(装载端)CP U = UP—加计数脉冲输入端CP D = DOWN—减计数脉冲输入端CO——非同步进位输出端(低电平有效)BO——非同步借位输出端(低电平有效)D3 D2 D1 D0 = D C B A—计数器数据输入端Q D Q C Q B Q A—计数器数据输出端根据功能表我们可以设计一个特殊的12进制的计数器,且无0数。

如图19.1所示:当计数器计到13时,通过与非门产生一个复位信号,使第二片74LS192(时十位)直接置成0000,而第一片74LS192计时的个位直接置成0001;从而实现了1——12的计数。

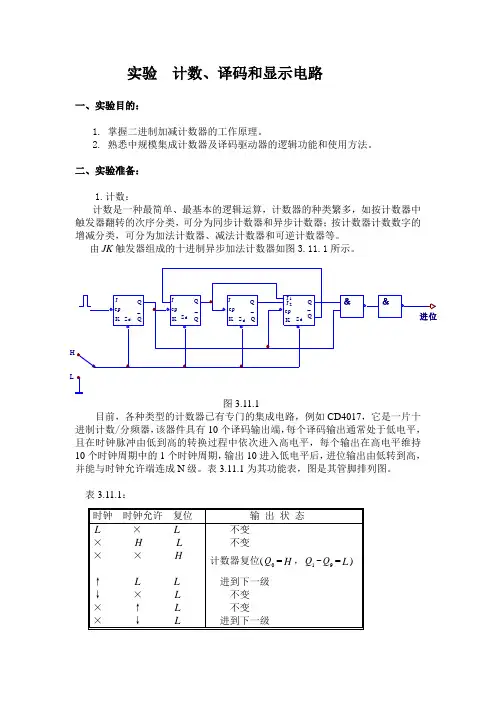

实验计数、译码和显示电路一、实验目的:1. 掌握二进制加减计数器的工作原理。

2. 熟悉中规模集成计数器及译码驱动器的逻辑功能和使用方法。

二、实验准备:1.计数:计数是一种最简单、最基本的逻辑运算,计数器的种类繁多,如按计数器中图3.11.2另外一种可预计的十进制加减可逆计数器CD4510,用途也非常广,其引脚排列如图3.11.3所示,其中,E P 为预计计数使能端,in C 为进位输入端,1P ~4P 为预计的输入端,out C 为进位输出端,U /D 为加减控制端,R 为复位端,CD4510输入、输出间的逻辑功能如表所示。

表3.11.2:。

2. 译码与显示:十进制计数器的输出经译码后驱动数码管,可以显示0~9十个数字,CD4511是BCD~7段译码驱动集成电路,其引脚排列如图3.11.4所示。

LT 为试灯输入,BI 为消隐输入,LE 为锁定允许输入,A 、B 、C 、D 为BCD 码输入,a~g 为七段译码。

CD4511的逻辑功能如表所示。

LED 数码管是常用的数字显示器,分共阴和共阳两种,BS112201是共阴的磷化镓数码管,其外形和内部结构如图3.11.5所示。

图3.11.5三、计算机仿真实验内容:1. 计数10的电路:(1).单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“CMOS”按钮,从弹出的对话框“Family”栏中选“CMOS_10V”,再在“Component”栏中选取4093BD和4017BD各一只,如图3.11.6所示,将它们放置在电子平台上。

图3.11.6(2).单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“Source”按钮,从弹出的对话框“Family”栏中选“POWER_SOURCES”,再在“Component”栏中选取“VDD”和地线,将它们调出放置在电子平台上。

(3). 双击“VDD”图标,将弹出如图3.11.7所示对话框,将“V oltage”栏改成“10”V,再点击下方“确定”按钮退出。

微型计算机原理与接口技术实验报告班级:学号:姓名:指导老师:朱亚萍实验名称:定时器/ 计数器8259单级中断控制器实验实验六定时器/计数器一、实验目的1. 学会8253芯片和微机接口的原理和方法;2. 掌握8253定时器/计数器的工作方式和编程原理。

二、实验内容用8253的0通道工作在方式3,产生方波。

三、实验接线图图6-1四、编程指南1. 8253芯片介绍:8253是一种可编程定时/计数器,有三个十六位计数器,其计数频率范围为0-2MHz,用+5V单电源供电。

8253的功能用途:⑴延时中断⑵可编程频率发生器⑶事件计数器⑷二进制倍频器⑸实时时钟⑹数字单稳态输出⑺复杂的电机控制器2. 8253的六种工作方式:⑴方式0:计数结束中断⑵方式l:可编程频率发生⑶方式2:频率发生器⑷方式3:方波频率发生器⑸方式4:软件触发的选通信号⑹方式5:硬件触发的选通信号五、实验程序框图图6-2六、实验步骤1. 断电连接导线, 按图6-1连好实验线路:⑴8253的GATE0接+5V;⑵8253的CLK0插孔接分频器74LS393(左下方)的T2插孔,分频器的频率源为8.0MHZ,T→8.0MHZ。

2. 在PC机和实验系统联机状态下,新建实验程序,编辑完成后进行保存(保存后缀为.asm文件);3. 编译下载;4. 全速运行,运行程序。

七、实验程序CODE SEGMENTASSUME CS:CODETIME PROC FARSTART:MOV DX,43HMOV AL,37HOUT DX,ALMOV DX,40H;控制口地址;设置通道0,先读写低字节后读写高;字节,方式3,BCD计数;通道0口地址MOV AL,00HOUT DX,ALMOV AL,90HOUT DX,ALJMP $TIME ENDPCODE ENDSEND START;先读写低字节;后读写高字节;结束程序八、实验结果将OUT0接二极管,相应的发光二极管会以一定周期闪烁。

实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图1.8.1(a)是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图1.8.1(b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FFO(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的C P端接FF0的Q0端,因而当FFO(Q O)由1→ 0时,FF1翻转。

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。

目录一、原理 (5)二、动作的检查方法及计数器检测仪原理 (6)三、操作方法 (7)四、注意事项 (9)五、装箱清单 (9)六、售后服务 (9)HTFZ-II 避雷器放电计数器检验仪一、原理图1 所示为ZK 型计数器的原理接线图。

图1(a)为ZK 型动作计数器的基本结构,即所谓的双阀片式结构。

当避雷器动作时,放电电流流过阀片R1,在R1上的压降经阀片R2给电容器C 充电,然后C 再对电磁式计数器的电感线圈L 放电,使其转动1 格,记1次数。

改变R1及R2的阻值,可使记数器具有不同的灵敏度。

一般最小动作电流为100A(8/20μs)的冲击电流。

因R1上有一定的压降,将使避雷器的残压有所增加,故它主要用于40kV 以上的高压避雷器。

图1(b)表示ZK-8 型动作计数器的结构,系整流式结构。

避雷器动作时,高温阀片R1上的压降经全波整流给电容器C 充电,然后C 再对电磁式计数器的L 放电,使其记数。

该计数器的阀片R1的阻值较小(在10kA 时的压降为1.1kV),通流容量较大(1200A 方波),最小动作电流也为100A(8/20 s)的冲击电流。

ZK-8 型计数器可用于6.0~330kV 系统的避雷器,ZK-8A 型计数器可用于500kV 系统的避雷器。

二、动作的检查方法及计数器检测仪原理由于密封不良,动作计数器在运行中可能进入潮气或水分,使内部元件锈蚀,导致计数器不能正常动作,所以《规程》规定,每年应检查1 次。

现场检查计数器动作的方法有电容器放电流支、交流法和标准冲击电流法。

研究表明,以标准冲击电流法最为可靠,其原理接线如图2 所示。

将冲击电流发生器发生的8/20μs、100A 的冲击电流波作用于动作计数器,若计数器动作正常,则说明仪器良好,否则应解体检修。

例如某电业局曾用此法对27 只计数器进行检测,其中有3 只不动作,解体发现内部元件受潮、损坏。

《规程》规定,连续测试3~5 次,每次应正常动作,每次时间间隔不少于30s。

“雷正电气”11年专注生产:电缆桥架、金属线槽、JDG/KBG镀锌线管厂家

老电工分享25张电能表接线图,你了解多少?

电能表是用来测量电能的仪表,又称电度表,火表,千瓦小时表,指测量各种电学量的仪表。

使用电能表时要注意,在低电压(不超过500伏)和小电流(几十安)的情况下,电能表可直接接入电路进行测量。

在高电压或大电流的情况下,电能表不能直接接入线路,需配合电压互感器或电流互感器使用。

单相有功电度表(简称:单相电度表)由接线端子、电流线圈、电压线圈、计量转盘、计数器构成,只要电流线圈通过电流,同时电压线圈加有电压,转盘就受到电磁力而转动。

单相电度表共有5个接线端子,其中有两个端子在表的内部用连片短接,所以,单相电度表的外接端子只有4个,即1、2、3、4号端子。

由于电度表的型号不同,各类型的表在铅封盖内都有4各端子的接线图。

实验七计数器一、实验目的1. 熟悉中规模集成计数器的逻辑功能及使用方法。

2. 掌握用中规模集成计数器构成任意进制计数器的方法。

3. 学习用集成触发器构成计数器的方法。

二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可以用来对脉冲计数,还常用作数字系统的定时、分频和执行数字运算以及其他特定的逻辑功能。

计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数进制的不同,分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器;如按预置和清除方式来分,则有并行预置、直接预置、异步清除和同步清除等;按权码来分,则有“8421”码,“5421”码、余“3”码等计数器及可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数电路。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1.十进制计数器74LS90(二、五分频)74LS90是模二-五-十异步计数器。

具有计数、清除、置9功能。

74LS90包含M=2和M=5两个独立的下降沿触发计数器,清除端和置9端两计数器公用,没有预置端。

模2计数器的时钟输入端为A(CP1),输出端为Q A;模5计数器的时钟输入端为B(CP2)。

输出端由高位到低位为Q D、Q C、Q B;异步置9端为S91和S92,高电平有效。

即只要S91·S92=1,则输出Q D Q C Q B Q A为1001;异步清除端为R01和R02,当R01·R02=1,且S91·S92=0时,输出Q D Q C Q B Q A=0000;只有R01·R02=0,S91·S92=0,即两者全无效时,74LS90才能执行计数操作。

深圳大学实验报告课程名称:数字电子技术实验项目名称:计数器学院:光电工程学院专业:光源与照明指导教师:**报告人:黄学号:2016 班级:实验时间:2018年12月19日实验报告提交时间:教务处制三、实验原理:计数器器件是应用较广的器件之一,它有很多型号,各自完成不同的功能,可根据不同的需要选用。

本实验选用74LS162做实验器件。

74LS162引脚图见图1。

74LS162是十进制BCD同步计数器。

Clock是时钟输入端,上升沿触发计数触发器翻转。

允许端P和T都为高电平时允许计数,允许端T为低时禁止Carry产生。

同步预置端Load加低电平时,在下一个时钟的上升沿将计数器置为预置数据端的值。

清除端Clear为同步清除,低电平有效,在下一个时钟的上升沿将计数器复位为0。

74LS162的进位位Carry在计数值等于9时,进位位Carry为高,脉宽是1个时钟周期,可用于级联。

四、实验内容与步骤:(一)实验内容:1、用1片74LS162和1片74LS00采用复位法构一个模7计数器。

用单脉冲做计数时钟,观测计数状态,并记录。

用连续脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

2、用1片74LS162和1片74LS00采用置位法构一个模7计数器。

用单脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

3、用2片74LS162和1片74LS00构成一个模60计数器。

2片74LS162的Q D,Q C,Q B,Q A分别接两个译码显示的D,B,C,A端。

用单脉冲做计数时钟,观测数码管数字的变化,检验设计和接线是否正确。

(二)实验接线及测试结果:1、复位法构成的模7计数器接线图及测试结果(1)复位法构成的模7计数器接线图图9.1 复位法7进制计数器接线图1 图9.2 复位法7进制计数器接线图2 图中,AK1是按单脉冲按钮,LED0,LED1,LED2和LED3是逻辑状态指示灯,100kHz 是连续脉冲源。

plc计数器怎么用?plc计数器用法

计数器

计数器实物图

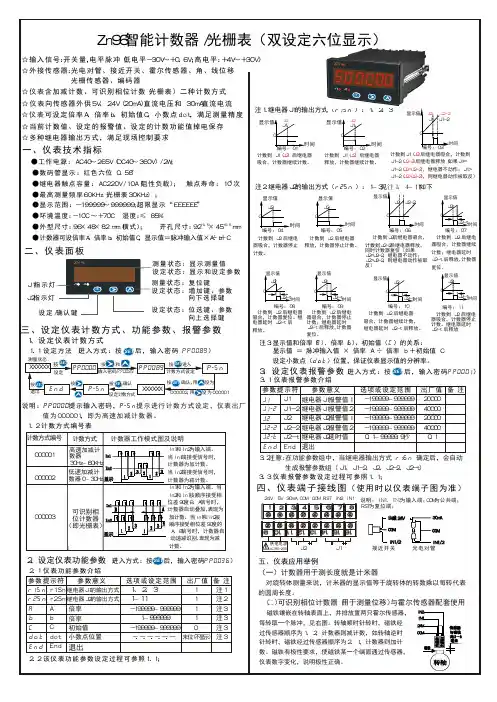

计数器接线图

功能介绍

通过传动机构驱动计数元件,指示被测量累计(加法计数)或逆计(减法计数)值的器件,当数量达到预设值输出接通或断开信号。

下面介绍一下加法计数应用。

加法计数器应用电路图

1、4 脚为电源输入端,

2、3 脚为信号输入端,5、6 脚为内部常开触点输出端。

等效 plc 梯形图

工作原理

加法计数器时序图

从时序图中可以看出其工作原理:按下和松开常开按钮一次,计数器显示窗口加一显示,假设计数器预设值为 3,当按下和松开常开按钮数值到达 3 次后,内部常开触点闭合。