数电课程设计-30秒倒计时器

- 格式:doc

- 大小:261.25 KB

- 文档页数:13

数字电路课程设计报告题目:篮球竞赛30s计时器专业:电气工程及其自动化班级:09电气(6)班姓名:***学号: ************同组队员:徐英谋黄有义何耀成陈泽汉邹迪日期:2011 年6 月24日目录一、设计目的 (2)二、设计要求和设计任务 (2)2.1设计要求 (2)2.2设计任务 (2)三、总体框图设计、 (3)四、功能模块设计和原理说明 (3)4.1设计原理 (3)4.2设计方案 (3)4.3单元模块 (4)4.3.1时钟模块 (4)4.3.2 8421BCD码递减计数器模块 (5)4.3.3 控制模块 (7)4.3.4 译码显示模块 (8)五、总电路图程序说明 (10)六、电路仿真与调试 (11)6.1启动、暂停、置数 (11)6.2倒计时功能 (11)6.3报警功能 (12)七、总结 (13)一、设计目的现代社会电子计数器在许多领域中均得到普遍应用,诸如在体育比赛,定时报警器、游戏中的倒时器,交通信号灯、红绿灯、行人灯、交通纤毫控制机、还可以用来做为各种药丸,药片,胶囊在指定时间提醒用药等等,由此可见计时器在现代社会是何其重要的。

篮球作为一项全民健身项目,已有一定的历史。

在中国,篮球很盛行,篮球比赛也日趋职业化。

篮球比赛中有一项违例时间要用倒计时器,目前多数采用的是24秒制,但随着篮球制度的改革将会采用30秒制。

有需要就会有市场,因此设计一款30秒计时器是非常有必要也非常有前景的。

该款计时器是在原来的基础上把24秒制改为30秒制。

该计时器要有递减计时及报警功能。

因此符合比赛中违例判罚的需要。

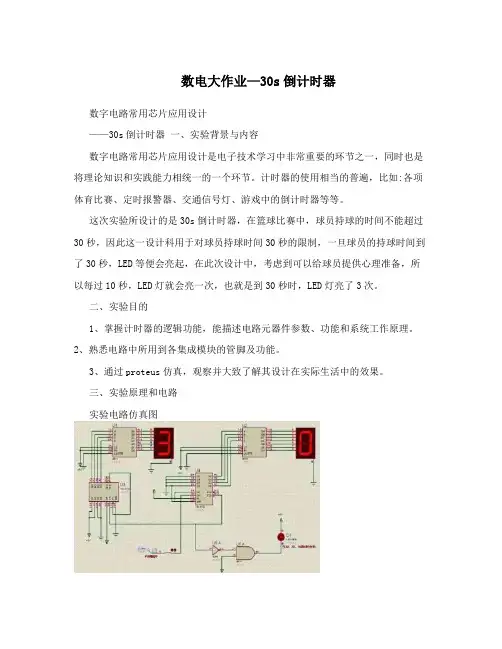

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。

本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。

一旦球员的持球时间超过了30秒,它自动的报警从而判定此球员的犯规。

本设计主要能完成:显示30秒倒计时功能;系统设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能;在直接清零时,数码管显示器灭灯;计时器为30秒递减计时其计时间隔为1秒;计时器递减计时到零时,数码显示器不灭灯,同时发出光电报警信号等。

电子技术课程设计报告设计题目:数字显示30秒倒计时器电路设计1、课程设计目的、意义设计目的:(1)依照原理图分析各单元电路的功能;(2)熟悉电路中所用到的1各集成块的1管脚及其功能;(3)进行电路的装接、调试,直到电路能达到规定的设计要求;(4)写出完整、详细的课程设计报告。

设计意义:数字显示30秒倒计时器是一个简单的数字电路,但是它能够扩展到很多实际应用当中来,比如篮球倒计时器、交通灯倒计时器等等。

2、设计题方案比较、论证设计方案:分析设计任务,计数器和操纵电路是系统的要紧部份。

计数器完成30秒计时功能,而操纵电路具有直接操纵计数器的启动设计、译码显示电路的显示和灭灯功能。

当启动开关闭合时,操纵电路应封锁时钟信号CP,同时计数器完成置数功能,译码显示电路显示“30”字样;当启动开关断开时,计数器开始计数;处于维持状态。

系统设计框图如图2-1所示。

数字显示30秒倒计时器实验电路如图2-2所示。

图2-1图2-23、各单元电路设计,元器件参数计算、选择、电路图绘制,整体电路图递减计数器模块计数器选用汇总规模集成电路74LS192进行设计较为简单,74LS192是十进制可编程同步加锁计数器,它采纳8421码二-十进制编码,而且有直接清零、置数、加锁计数功能。

图2-3是74LS192外引脚。

图中CPU 、CPD别离加计数、减计数的时钟脉冲输入端(上升沿有效)。

LD是异步并行置数操纵端(低电平有效),CO、BO别离是进位、借位输出端(低电平有效),CR是异步清零端,D3-D是并行数据输入端,Q3-Q是输出端。

74LS192的功能表见下表所示。

秒信号产生器秒信号产生器的电路是利用 555 按时器(图3-1)组成的秒信号发生器。

NE555 芯片有单稳态电路功能,可发生方波信号,可适当的选择电阻、电容,使其输出信号的周期为 1 秒。

本电路输出脉冲的周期为:T=*(R1+2*R2)*C,假设 T=1s,令 C=10μF,R1=39kΩ,那么R2=51k Ω。

吉林建筑大学城建学院课程设计报告题目名称30秒计数显示器设计院(系)电气信息工程系___________ 课程名称数字电子技术_____________ 班级建筑电气与智能化2013-1学号__________________________________ 学生姓名_______________________________ 指导教师_______________________________起止日期_______________________________摘要 (I)ABSTRACT .......................................................................... I I第1章绪论 (1)1.1设计目的 (1)1.2设计要求 (1)第2章总体方案设计 (2)2 .1设计方案 (2)2.2工作原理 (3)第3章单元电路设计 (4)3.174LS247 43.2555 定时器 (4)3.374LS48 译码器 (6)第4章安装调试 (7)4.1计时器电路 (7)4.2译码显示电路 (7)4.3仿真原理图 (8)4.4 电路测试 (10)总结 (11)致谢 (12)参考文献 (13)附录摘要电子课程设计是数字电子技术学习中非常重要的环节,它将理论知识和实践能力完美的结合,锻炼学生的能力。

本课程实际是脉冲数字电路的简单应用,设计30秒计时器。

此计时器有启动、暂停、和连续功能,可方便地实现断点计时功能。

计时间隔为1S,计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号。

本设计具有成本低,使用的元件少, 制作简单,计时准确、精确、稳定,使用简单方便的特点。

本设计实现了在许多场合进行时间追踪的功能,在社会上有广泛的应用价值。

关键计时器;数字电路;显示器ABSTRACTElectro nic course desig n is very importa nt role in digital electro nic tech no logy to leann, it would be a perfect comb in ati on of theoretical kno wledge and practical ability, trai ning stude nts' ability.This course is actually a simple application of the pulse digital circuit, design of 30 seconds timer. The timer has started, pause, and continuous function, can easily implement breakpo ints timer fun cti on. Timi ng in terval of 1 s, dimi nishi ng the timer timi ng to zero, thedigital display can't destroy the lamp, photoelectric alarm signal at the same time. This design is low cost, the use of fewer components, simple, time accurate, precise, stable, using the characteristics of simple and convenient. This design realized the function of time tracking in many occasi ons, has exte nsive applicati on value in society.Keywords: Timer ;Digital circuit ;Display第1章绪论1.1设计目的在学习了数字电子技术理论课和进行了基础实验后,进行课程设计,进一步提高学生运用所掌握的数字电子电路的分析和设计方法与分析实际电路的基本技能,并了解基本单元电路在实际生活中的应用。

30秒倒计时计数器设计——数字电子计数基础课程设计学院:计算机学院专业班级:通信工程10-2班时间:2013年1月7日目录设计要求 (3)正文一、倒计时器组成及原理 (3)1.1倒计时计数器组成 (3)1.2工作原理 (3)二、拟定设计方案 (4)2.1用Multisim进行仿真设计 (4)2.2设计实现数码管显示 (4)2.3设计555定时振荡实现秒振荡发生功能 (4)2.4设计实现减法计数功能 (5)2.5设计实现二位数减法计数功能 (5)2.6设计实现反馈电路实现30秒计数功能 (5)2.7设计实现控制电路实现启动、清零/复位和暂停/继续计数控制电路 (5)2.7.1清零/复位电路 (5)2.7.2暂停/继续计数电路 (6)2.7.3启动电路 (7)2.8设计实现闪烁报警电路 (8)三、功能说明总结 (9)四、课程设计小结 (9)参考文献 (10)附录:一、电路原理图 (11)二、元器件明细表 (11)设计要求:设计30秒倒计时计数器。

30秒倒计时器的设计功能要求包括:1、具有30秒倒计时功能;2、设置外部操作开关,控制计时器的直接清零/复位、开始和暂停/连续计数功能;3、计时器计时间隔为1秒;4、计时器递减计时到零时,数码显示器不灭灯,保持并闪烁光电报警。

5、计时器暂停计数时,数码管闪烁提醒;正文:一、倒计时器组成及原理1.1倒计时计数器组成倒计时计数器选用TTL集成电路,主要由秒定时振荡发生器、减法计数器、译码器、七段数码显示器、控制电路、闪烁报警电路等组成,在电路工作过程中,电路能够通过控制器实现开始计数、清零/复位、暂停/继续计数等功能,在倒计时结束保持00状态并不断闪烁提示报警,原理图如下:图11.2工作原理当电路工作时,由555定时器组成多谐振荡器,选取适当的电容使振荡周期为1s;用两片减法计数器芯片级联组成二位数计数器,用七段数码管显示计数;控制电路通过控制减法计数器的控制端实现对电路保留、启动、清零/复位和暂停/继续计数功能的控制;利用JK 触发器的翻转状态特性和译码器BI/RBO端的控制实现闪烁报警功能。

<<数字电子技术>>课程设计报告题目:数字倒计时设计专业:通信工程年级:2011级学学生姓名联系电指导老师:完成日期:2013年5月20日本课程设计利用了七段共阴显示数码管、74LS192芯片、74LS48芯片、蜂鸣器、电容、开关、电阻、74LS00芯片、74LS10芯片、NE555芯片、发光二极管、三极管、16脚底座、14脚底座、8脚底座等元件,完成了数字倒计时设计,这个设计能够实现具有显示计时功能,设置外部操作开关,启动和暂停/连续功能,计时器为递减计时,计时间隔为1S,计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号。

本设计具有成本低,使用的元件少,制作简单,计时准确、精确、稳定,使用简单方便的特点。

关键词:七段共阴显示数码管;74LS192芯片;NE555芯片。

ABSTRACTThis course is designed to use the seven paragraphs Yin shows that digital tube,74ls192,74ls48 chip,buzzer,capacitors,switches,resistors,74ls00,74ls10 chip,NE555 chip,light emitting diode,triode,14,16 foot base,8 feet base element etc,completed a digital countdown design,this design can be achieved with display timer function,set the external switch operation,start and pause/continuous functions,timer for decreasing timing,timing interval of 1s,diminishing the timer timing to zero,the digital display can't destroy the lamp,photoelectric alarm signal at the same time.This design is low cost and using less component,make simple,time accurate,precise,stable,simple to use convenient characteristic.Key words:7,a total of Yin shows that digital tube;74ls192 chips;NE555 chips.摘要........................................... 错误!未定义书签。

信息与计算机学院课程设计课程设计报告(2011/2012 第1学期)设计题目30秒定时器指导教师学生班级学生姓名学生学号考核成绩上海商学院2011年11月内容摘要此30秒计时器功能齐全,可以直接清零、启动、暂停和连续以及具有光电报警功能。

可以方便的实现断点计时功能,当设计器递减到零时,会发出光电报警信号。

在直接清零时,数码管显示器直接显示为00;计时器为30秒递减计时,计时间隔为1秒;计时器递减到0时,再回到30。

此设计器设计时,采用模块化得设计思想,使设计起来更加简单、方便、快捷。

关键词:秒脉冲发生器74LS192 计数器译码显示电路目录第一章引言 (1)1.1课程设计意义 (1)1.2研究状况概述 (1)第二章课程设计分析 (2)2.1 设计目的: (2)2.2 设计思路: (2)第三章系统方案论证过程 (3)3.1 30秒定时器总体方框图 (3)第四章模块电路设计 (4)4.1秒脉冲电路 (4)4.2 减计数电路 (4)4.3 译码和数码显示电路 (5)4.4时序控制电路.................................................................................... 错误!未定义书签。

4.5 整机框图 (6)第五章主要元器件与设备 (8)5.1元器件清单 (8)第六章系统调试与结果分析 (9)6.1 系统调试 (9)6.2 结果分析........................................................................................... 错误!未定义书签。

第七章总结.. (10)参考文献 (10)致谢 (10)附页: (11)第一章引言1.1课程设计意义数字显示30秒定时器是一个简单的数字电路,然而它可以扩展到很多实际应用当中来,比如篮球倒计时器,交通灯倒计时器等等。

课程设计任务书学生姓名:刘斌专业班级:通信0901指导教师:李文工作单位:题目: 篮球30秒计时器1 要求完成的主要任务:用中、小规模集成电路设计一台能显示并进行控制的30倒计时器,要求如下:1.具有显示30秒计时的功能。

2.设置外部工作开关,控制计时器的直接清零,启动与暂停/连续的功能。

3.计时器为30秒递减,时间间隔为1秒。

4.在直接清零是要求显示管灭灯。

5.计时器递减到零时,数码显示管不能灭灯,同时发出光电报警。

2 时间安排:时间:第1-12周理论设计,软件仿真,第15-18周实验室焊接、安装调试。

地点:理工楼E604实验室学生签名:年月日指导教师签名:年月日多功能数字钟电路设计摘要 (1)Abstract (2)1系统原理框图 (2)2方案设计与论证 (3)2.1秒脉冲发生电路 (4)2.2控制电路 (5)2.3计数电路 (7)2.4译码及显示单元电路 (8)2.5报警电路........................................................................................... 错误!未定义书签。

3单元电路的设计 (11)3.1秒脉冲产生电路的设计 (11)3.2计数电路的设计 (11)3.3控制电路的设计 (13)3.4译码及驱动显示电路设计 (12)3.5 报警电路 (16)3.6 电路总图 (14)4仿真结果及分析 (15)4.1 时钟结果仿真.................................................................................. 错误!未定义书签。

4.2 秒钟个位时序图.............................................................................. 错误!未定义书签。

《篮球竞赛30S计时器》课程设计说明书题目篮球竞赛30S计时器学生姓名学号所属学院专业班级 2指导教师教师职称目录一、设计要求 (1)二、电路设计与分析2.1设计原理 (1)2.2单元模块 (1)1、秒脉冲信号的产生 (1)2、计数器 (3)3、时钟信号控制电路 (4)4、显示模块电路 (5)5、报警电路 (6)三、外部操作开关 (6)四、设计原理图与电路总图 (6)五、仿真测试性能 (7)六、总结 (9)一、设计要求篮球竞赛30S计时器的基本要求:1)具有显示30S计时功能2)设置外部操作开关,控制计数器的直接清零,启动和暂停/连续功能3)在直接清零时,要求数码显示器灭灯4)计时器为30S递减计时,计时间隔为1S5)计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号〖主要元器〗:NE555(1),74LSl92(2)等二、电路分析与设计2.1设计原理篮球竞赛30S计时器的总体设计方案如下:它主要包括秒脉冲信号,30S 计数器,译码显示器部分,报警电路和外部操作开关五部分组成,其中外部操作开关包括接直接清零,启动和暂停/继续。

2.2单元模块1、秒脉冲信号的产生555定时器主要是通过外接电阻R和电容器C构成充、放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。

这就很方便地构成从微秒到数十分钟的延时电路、以及多谐振荡器、单稳态触发器、施密特触发器等脉冲波形产生和整形电路。

NE555为8脚时基集成电路,各脚主要功能1地 GND 2触发3输出 4复位5控制电压 6门限(阈值)7放电 8电压Vcc用555定时器构成多谐振荡器:用555定时器构成多谐振荡器电路如图(a)所示。

电路没有稳态,只有两个暂稳态,也不需要外加触发信号,利用电源VCC 通过R1和R2向电容器C充电,使uC逐渐升高,升到2VCC /3时,uO跳变到低电平,放电端D导通,这时,电容通过电阻R2和D端放电,使uC 下降,降到VCC/3时,uO跳变到高电平,D端截止,电源VCC又通过R1和R2向电容器C充电。

《篮球竞赛30S计时器》课程设计说明书题目篮球竞赛30S计时器学生姓名学号所属学院专业班级 2指导教师教师职称目录一、设计要求 (1)二、电路设计与分析2.1设计原理 (1)2.2单元模块 (1)1、秒脉冲信号的产生 (1)2、计数器 (3)3、时钟信号控制电路 (4)4、显示模块电路 (5)5、报警电路 (6)三、外部操作开关 (6)四、设计原理图与电路总图 (6)五、仿真测试性能 (7)六、总结 (9)一、设计要求篮球竞赛30S计时器的基本要求:1)具有显示30S计时功能2)设置外部操作开关,控制计数器的直接清零,启动和暂停/连续功能3)在直接清零时,要求数码显示器灭灯4)计时器为30S递减计时,计时间隔为1S5)计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号〖主要元器〗:NE555(1),74LSl92(2)等二、电路分析与设计2.1设计原理篮球竞赛30S计时器的总体设计方案如下:它主要包括秒脉冲信号,30S 计数器,译码显示器部分,报警电路和外部操作开关五部分组成,其中外部操作开关包括接直接清零,启动和暂停/继续。

2.2单元模块1、秒脉冲信号的产生555定时器主要是通过外接电阻R和电容器C构成充、放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。

这就很方便地构成从微秒到数十分钟的延时电路、以及多谐振荡器、单稳态触发器、施密特触发器等脉冲波形产生和整形电路。

NE555为8脚时基集成电路,各脚主要功能1地 GND 2触发3输出 4复位5控制电压 6门限(阈值)7放电 8电压Vcc用555定时器构成多谐振荡器:用555定时器构成多谐振荡器电路如图(a)所示。

电路没有稳态,只有两个暂稳态,也不需要外加触发信号,利用电源VCC 通过R1和R2向电容器C充电,使uC逐渐升高,升到2VCC /3时,uO跳变到低电平,放电端D导通,这时,电容通过电阻R2和D端放电,使uC 下降,降到VCC/3时,uO跳变到高电平,D端截止,电源VCC又通过R1和R2向电容器C充电。

华南理工大学广州学院数字电路课程设计报告题目:篮球竞赛30s计时器专业:自动化班级: 2姓名:同组队员:学号:日期: 2012 年 12 月 30日一.设计目的为了巩固课本所学知识,培养动手能力和实际解决问题的能力,加深对课堂知识的理解和运用,进一步学习和熟悉各种常用芯片的规格和使用,能掌握电路的组装和基本问题的排除。

二.设计要求和设计指标(1)具有30s计时功能,并且能够实时显示计数结果(2)设有外部操作开关,控制计数器实现直接清零、启动以及暂停/连续工作等操作。

(3)计时器为30s递减计时间隔为1s。

(4)计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号三.总体框图设计图1-1 30秒计时器系统设计框图四.功能模块设计和原理说明4.1秒脉冲发生器用555集成电路组成多谐振荡电路为系统提供时钟秒脉冲。

555定时器应用为多谐振荡电路时,当电源接通Vcc通过电阻R1、R2向电容C充电,其上电压按指数规律上升,当u上升至2/3Vcc,会使比较器C1输出翻转,输出电压为零,同时放电管T导通,电容C通过R2放电;当电容电压下降到1/3Vcc,比较器C2工作输出电压变为高电平,C放电终止,Vcc通过R1、R2又开始充电;周而复始,形成振荡。

则其振荡周期与充放电时间有关,也就是与外接元件有关,不受电源电压变化影响。

公式计算: T1=(R1+R2)Cln2; T2=R2Cln2;振荡周期T = T1+T2=0.7(R1+2R2)C =1(s)若取C=10μF ,结合实际选取电阻为R1=5.1K,R2=4.7K 。

图2-1 555多谐振荡电路图NE555为8脚时基集成电路,各脚主要功能(集成块图在下面) 1地 GND 2触发 3输出 4复位 5控制电压 6门限(阈值) 7放电 8电源电压VCCR2 C 10uf4.7K5.1K4.2 计数电路计数电路选用两片中规模集成电路74LS192进行设计,74LS192是十进制计数器,具有“异步清零”和“异步置数”功能,且有进位和借位输出端。

一、概述在篮球比赛中,规定了一方的持球时间不能超过30秒,否则就被判做犯规。

本课程设计的“篮球竞赛30秒计时器”,就可用于篮球比赛中,用于对球员持球时间30秒进行限制。

一旦球员的持球时间超过了30秒,它自动的报警。

这次课设设计了一个一个篮球竞赛30秒计时器电路。

它由秒脉冲发生器、计数器、译码显示电路、报警电路和时序控制电路五个部分组成。

当计数器接收到秒脉冲后开始倒记数,等递减到0时,发光二极管亮光报警。

通过控制电路来完成计时器的启动、计数、暂停/继续、译码显示电路的显示等功能。

本电路用两个74LS192芯片构成递减计数器(30进制);控制电路由74LS00和74LS08构成;秒脉冲发生器由555集成定时器构成;两个数码管构成显示电路。

二、方案论证秒脉冲发生器译码显示计数器控制电路报警电路外部操作开关{图1 篮球竞赛30秒计时器原理框图篮球竞赛30秒计时器原理框图如图1所示。

功能的电路采用模块化设计,分别都有各自的功能。

篮球竞赛30秒计时器包括秒脉冲发生器、计数器、译码显示电路、控制电路、报警电路等5个部分组成。

其中计数器和控制电路是系统的主要部分。

计数器完成30秒计时功能,而控制电路控制计数器的启动计数、暂停/继续计数。

当启动置数开关时,计数器完成置数功能显示30秒字样;当启动开关时,计数器开始计数;暂停/继续开关连接到连续计数端时,计数器开始连续计数,当连接到暂停计数端时,计数器暂停计数。

计数器递减到零时,发出光电报警信号。

三、电路设计(1) 8421BCD码递减计数器模块电路本实验中计数器选用中规模集成电路74LS192进行设计,74LS192是十进制同步加法/减法计数器,它采用8421BCD码二-十进制编码,其功能表如表1所示。

表1 74LS192的功能表CPU CPD CR 操作××0 0 置数↑ 1 1 0 加计数1 ↑ 1 0 减计数××× 1 清零由此看出,当LDˊ=1,CR=0,CPD=1时,如果有时钟脉冲加到CPU端,则计数器在预置数的基础上进行加法计数,当计数到9时,COˊ端输出进位下降沿跳变脉冲;当LDˊ=1,CR=0,CPU =1时,如果有时钟脉冲加到CPD端,则计数器在预置数的基础上进行减法计数,当计数到0时,BOˊ端输出借位下降沿跳变脉冲。

30秒计数器课程设计一、课程目标知识目标:1. 学生能理解30秒计数器的基本原理,掌握其计时功能。

2. 学生能运用所学知识,解释30秒计数器在实际生活中的应用。

3. 学生了解时间单位秒的概念,并将其与计数器相结合。

技能目标:1. 学生通过动手操作,培养观察、分析和解决问题的能力。

2. 学生能够独立完成30秒计数器的制作,提高动手实践能力。

3. 学生学会运用计数器进行时间管理,提高自我管理能力。

情感态度价值观目标:1. 学生培养对科学技术的兴趣,激发探索精神。

2. 学生在小组合作中,学会相互尊重、沟通和协作,培养团队精神。

3. 学生通过学习,认识到时间的重要性,养成珍惜时间的良好习惯。

课程性质:本课程为科学实践活动,结合数学和科学知识,旨在培养学生的动手能力、观察力和时间管理意识。

学生特点:四年级学生具有一定的观察、分析和动手能力,对新鲜事物充满好奇心,但注意力集中时间较短,需要引导和激发。

教学要求:教师需注重实践与理论相结合,引导学生主动参与,关注学生个体差异,鼓励学生提问和表达,确保每个学生都能在课程中取得实际成果。

通过对课程目标的分解,为后续的教学设计和评估提供明确方向。

二、教学内容本节课教学内容主要包括以下几部分:1. 计时器原理介绍:讲解30秒计时器的运作原理,如电磁继电器、计时脉冲发生器等,结合课本相关章节,让学生了解计时器的基本构造。

2. 时间单位秒的认识:回顾秒的定义,以及与分钟、小时的关系,使学生在实践中加深对时间单位秒的理解。

3. 制作30秒计数器:指导学生按照教材指导,动手制作一个简单的30秒计时器,培养学生的动手实践能力。

4. 实践应用:探讨30秒计时器在实际生活中的应用场景,如烹饪、运动等,让学生认识到所学知识在实际生活中的价值。

5. 时间管理教育:结合30秒计时器,教育学生珍惜时间,合理安排学习和生活,提高效率。

教学内容安排和进度:第一课时:介绍计时器原理,认识时间单位秒;第二课时:动手制作30秒计数器,进行实践操作;第三课时:讨论30秒计时器的实际应用,进行时间管理教育。

目录前言 (2)第一章设计任务及要求 (3)第二章电路设计原理与设计电路 (4)第三章单元模块3.1 秒脉冲发生器 (5)3.2 倒计时电路 (6)3.3 数码管驱动电路 (7)3.4 报警电路 (7)3.5 控制电路 (8)第四章电路仿真、安装与调试4.1 电路仿真 (10)4.2 安装与调试 (10)第五章实验总结 (11)参考文献 (12)附录一 (13)附录二 (14)附录三 (15)前言数字系统中,使用的最多的时序电路是计数器,计数器在生活中得到了广泛的应用。

篮球运动近几年在我国兴起,逐渐成为一种全民健身的项目。

篮球比赛中的30秒规定使得计数器再次发挥了它的功能。

本次设计中利用即为双向计时器的减计数功能完成电路的倒计时。

除了能够显示30秒倒计时外,本设计电路还具有直接清零、暂停、报警等功能。

在正规的篮球比赛中,对时间的精确度的要求较高,有时在最后的几分钟内赛事可以发生很大的逆转。

而运动员控球不可超过30秒的规定更是将比赛对时间的要求精确到了秒甚至更小的单位。

为了满足赛事对时间的要求,设计一个30秒倒计时器,通过显示倒计时,倒计时结束时发出警报帮助裁判更好的判定运动员是否违规。

通过控制电路报警,很大程度上避免了人为因素产生的误差,从而更体现了比赛中的公平公正原则。

并且,随着篮球运动的流行,这种计时器的市场十分可观。

因此,设计一个30秒倒计时器意义重大。

第一章设计任务及要求(1)具有显示30S计时功能;(2)设置外部操作开关,控制计数器的直接清零,启动和暂停/连续功能;(3)在直接清零时,要求数码显示器灭灯;(4)计时器为30S递减计时,计时间隔为1S;(5) 计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号。

第二章电路设计原理本设计是脉冲数字电路的简单应用。

基本设计思路为:利用555时基电路构成的多谐振荡器来产生频率为10Hz的脉冲,即输出周期为0.1秒的方波,再将该脉冲信号加到由74LS161构即周期为1秒,接着将该信号送到计数器74LS192的CP减计数脉冲端,再通过译码器74LS248把输入的8421BCD码经过内部作和电路“翻译”成七段输出,然后直接推成动LED,显示十进制数,然后在适当的位置设置开关或控制电路即可实现计数器的直接清零,启动和暂停/连续、译码显示电路的显示与灭灯及光电报警等功能,光电报警用发光二极管来代替,灯亮代表报警。

目录简介1 1 系统组成原理 (2)2 元器件的选择 (4)2.1 计时器电路元器件的选择 (4)2.2 译码显示电路元器件的选择 (5)七段发光二极管(LED)数码管 (5)2.3 555定时器 (6)3 各部分设计及其原理图 (8)3.1 30秒循环计数器的原理图 (8)3.2 开关控制电路 (9)3.3 秒脉冲发生电路 (9)3.4 报警电路 (10)4 总原理图 (10)5 课设小结 (11)6 参考文献 (12)简介随着信息时代的到来,电子技术在社会生活中发挥着越来越重要的作用,运用数电知识设计的电子产品成为社会生活不可缺少的一部分,特别是在各种竞技运动中,计时器成为检验运动员成绩的一个重要工具。

电子课程设计是电子技术学习中非常重要的一个环节,是将理论知识和实践能力相统一的一个环节,是真正锻炼学生能力的一个环节。

在许多领域中计时器均得到普遍应用,诸如在体育比赛,定时报警器、游戏中的倒时器,交通信号灯、红绿灯、行人灯、交通纤毫控制机、还可以用来做为各种药丸,药片,胶囊在指定时间提醒用药等等,由此可见计时器在现代社会是何其重要的。

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。

本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。

一旦球员的持球时间超过了30秒,它自动的报警从而判定此球员的犯规。

本设计主要能完成:显示30秒倒计时功能;系统设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能;在直接清零时,数码管显示器灭灯;计时器为30秒递减计时其计时间隔为1秒;计时器递减计时到零时,数码显示器不灭灯,同时发出光电报警信号等。

同时本课程设计是脉冲数字电路的简单应用,设计了篮球竞赛30秒计时器。

此计时器功能齐全,可以直接清零、启动、暂停和连续以及具有光电报警功能,同时应用了七段数码管来显示时间。

此计时器有了启动、暂停和连续功能,可以方便地实现断点计时功能,当计时器递减到零时,会发出光电报警信号。

《篮球竞赛30S计时器》课程设计说明书题目篮球竞赛30S计时器学生姓名学号所属学院专业班级 2指导教师教师职称目录一、设计要求 (1)二、电路设计与分析2.1设计原理 (1)2.2单元模块 (1)1、秒脉冲信号的产生 (1)2、计数器 (3)3、时钟信号控制电路 (4)4、显示模块电路 (5)5、报警电路 (6)三、外部操作开关 (6)四、设计原理图与电路总图 (6)五、仿真测试性能 (7)六、总结 (9)一、设计要求篮球竞赛30S计时器的基本要求:1)具有显示30S计时功能2)设置外部操作开关,控制计数器的直接清零,启动和暂停/连续功能3)在直接清零时,要求数码显示器灭灯4)计时器为30S递减计时,计时间隔为1S5)计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号〖主要元器〗:NE555(1),74LSl92(2)等二、电路分析与设计2.1设计原理篮球竞赛30S计时器的总体设计方案如下:它主要包括秒脉冲信号,30S 计数器,译码显示器部分,报警电路和外部操作开关五部分组成,其中外部操作开关包括接直接清零,启动和暂停/继续。

2.2单元模块1、秒脉冲信号的产生555定时器主要是通过外接电阻R和电容器C构成充、放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。

这就很方便地构成从微秒到数十分钟的延时电路、以及多谐振荡器、单稳态触发器、施密特触发器等脉冲波形产生和整形电路。

NE555为8脚时基集成电路,各脚主要功能1地 GND 2触发3输出 4复位5控制电压 6门限(阈值)7放电 8电压Vcc用555定时器构成多谐振荡器:用555定时器构成多谐振荡器电路如图(a)所示。

电路没有稳态,只有两个暂稳态,也不需要外加触发信号,利用电源VCC 通过R1和R2向电容器C充电,使uC逐渐升高,升到2VCC /3时,uO跳变到低电平,放电端D导通,这时,电容通过电阻R2和D端放电,使uC 下降,降到VCC/3时,uO跳变到高电平,D端截止,电源VCC又通过R1和R2向电容器C充电。

30秒倒计时计数器设计——数字电子计数基础课程设计学院:计算机学院专业班级:通信工程10-2班时间:2013年1月7日目录设计要求 (3)正文一、倒计时器组成及原理 (3)1.1倒计时计数器组成 (3)1.2工作原理 (3)二、拟定设计方案 (4)2.1用Multisim进行仿真设计 (4)2.2设计实现数码管显示 (4)2.3设计555定时振荡实现秒振荡发生功能 (4)2.4设计实现减法计数功能 (5)2.5设计实现二位数减法计数功能 (5)2.6设计实现反馈电路实现30秒计数功能 (5)2.7设计实现控制电路实现启动、清零/复位和暂停/继续计数控制电路 (5)2.7.1清零/复位电路 (5)2.7.2暂停/继续计数电路 (6)2.7.3启动电路 (7)2.8设计实现闪烁报警电路 (8)三、功能说明总结 (9)四、课程设计小结 (9)参考文献 (10)附录:一、电路原理图 (11)二、元器件明细表 (11)设计要求:设计30秒倒计时计数器。

30秒倒计时器的设计功能要求包括:1、具有30秒倒计时功能;2、设置外部操作开关,控制计时器的直接清零/复位、开始和暂停/连续计数功能;3、计时器计时间隔为1秒;4、计时器递减计时到零时,数码显示器不灭灯,保持并闪烁光电报警。

5、计时器暂停计数时,数码管闪烁提醒;正文:一、倒计时器组成及原理1.1倒计时计数器组成倒计时计数器选用TTL集成电路,主要由秒定时振荡发生器、减法计数器、译码器、七段数码显示器、控制电路、闪烁报警电路等组成,在电路工作过程中,电路能够通过控制器实现开始计数、清零/复位、暂停/继续计数等功能,在倒计时结束保持00状态并不断闪烁提示报警,原理图如下:图11.2工作原理当电路工作时,由555定时器组成多谐振荡器,选取适当的电容使振荡周期为1s;用两片减法计数器芯片级联组成二位数计数器,用七段数码管显示计数;控制电路通过控制减法计数器的控制端实现对电路保留、启动、清零/复位和暂停/继续计数功能的控制;利用JK 触发器的翻转状态特性和译码器BI/RBO端的控制实现闪烁报警功能。

二、拟定设计方案2.1用Multisim进行仿真设计Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

Multisim中提供了丰富的硬件数据可供选择,它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

通过Multisim可以及时仿真实现电路设计功能并及时发现存在的问题进行改正,可以确保设计的电路能够正常实现应有的功能。

2.2设计实现数码管显示选取共阴极七段红色数码管作为显示器,译码器选择74LS48N,将译码器的LT、RBI 端直接接高电平,BI/RBO也接高电平,将七段数码管的七个引脚分别接100Ω电阻后于译码器输出端相连,在译码器输入端输入电平实现了数码管显示功能。

2.3设计555定时振荡实现秒振荡发生功能如图2,用555定时器、电容电阻组成多谐振荡发生器,C1选择1uF,图中C1为100nF 为仿真实验用数据,C2选择10nF,电阻均为5.1kΩ,由周期计算公式:T≈0.7(R1+2R2)C1 ≈ 1s图22.4设计实现减法计数功能选用74LS191N加减计数器作为减法计数器芯片,U/D加减控制端接高电平将74LS191N 设置为减法计数状态,将74LS191N输出端与74LS48N译码器的输入端相接,脉冲接555定时振荡电路产生的谐振脉冲,实现减法计数功能。

2.5设计实现二位数减法计数功能级联两片均设置为减法计数器的74LS191N,将低位减计数器的进位端RCO接高位减计数器的EN使能端(图中为CTEN端),将数码管、电阻及译码器74LS48N按2.2中说明连接,实现二位数减计数功能。

2.6设计实现反馈电路实现30秒计数功能如图3,采用74LS191N异步置数,高位反馈输出OA、OB通过两个2输入与非门两次与非反馈给D触发器RESET端,为实现控制功能准备,最终反馈给预制LD端(电路图中为LOAD端);低位反馈输出OB、OD同高位方法实现。

高位预置数端DCBA预置0100,低位预置数端DCBA预置1001,实现30秒计数。

图32.7设计实现控制电路实现启动、清零/复位和暂停/继续计数控制电路2.7.1清零/复位电路高、低位74LS191N的反馈信号分别通过两个2输入与非门两次与非输入D触发器的RESET端,同时D端与清零/复位控制电路相连,D触发器输出Q再反馈会LOAD端(即LD端),两个D触发器的D端均与开关J4所在清零/复位控制电路电阻、二极管右端,开关左端相接(如图3),高位74LS191N的高电平预置数与低位74LS191N的高电平预置数端与D输入接线位置相同,使得开关闭合前高低位74LS191N的高电平预置数及D为高电平,闭合后高低位74LS191N的高电平预置数及D为低电平,从而控制LD预置端实现清零和复位功能。

如图4,J4控制电路为清零/复位控制电路,J4为控制开关,闭合清零,开启复位。

图42.7.2暂停/继续计数电路单刀单掷开关J1所在电路为暂停/继续计数功能电路。

如上图4,开关J1闭合前,J1所在电路反馈低电平,当J1闭合后,J1所在电路反馈高电平,反馈信号经如下图5两个或非门两次或非输入D触发器输入D端(如下图5),D触发器输出Q接低位74LS191N的CTEN端(及EN使能端),上面的JK触发器的输出端与第一个或非门的另一输入端相连。

电路工作时,当J1断开,正常工作,当J1闭合时,使能端CTEN变为高电平,低位74LS191N 输出保持,使电路进入暂停状态,断开J1则继续计数。

图52.7.3启动电路如上图5,J3所在为启动控制电路,当J1处于断开状态,RESET端为低电平,当闭合J1后,RESET端为高电平,JK触发器输出置0,正常工作状态下第一级或非门另一输入为0,经两级或非后输入D触发器,且输入为低电平,即输出端Q输出低电平至CTEN(EN 使能端)使电路启动。

74LS191N功能表如图:预置使能加/减控制时钟预置数据输入输出工作模式LD EN D/U CP D3 D2 D1 D0Q3 Q2 Q1 Q00 x x x d3 d2 d1 d0d3 d2 d1 d0异步置数1 1 x x x x x x 保持数据保持1 0 0 x x x x 加法计数加法计数1 0 1 x x x x 加法计数减法计数图62.8设计实现闪烁报警电路 根据译码器控制端BI/RBO 功能 功能(输入)输入输入/输出 输出LT RBI A 3 A 2 A 1 A 0 BI/RBOa b c d e f g 灭灯xxxxxx 00 0 0 0 0 0 0图7如图7,当BI/RBO 为0时,不论LT ,RBI 及A3A2A1A0为何值,输出为0且数码管为灭灯状态。

当BI/RBO 为1时,正常输出输入数据。

对于JK 触发器,J 端接高电平,K 端与低位74LS191N 的使能端EN (电路图中CTEN 端)相接,则K 端在计数使能时为低电平,暂停或计数到00时为高电平,由JK 触发器功能表如下:图8如图9,将74LS48N 译码器的BI/RBO 与该JK 触发器的输出端相连,由图8可知当J=1,K=0时,BI/RBO 置1,数码管正常工作;当J=1,K=1时,BI/RBO 翻转,使数码管时亮时灭闪烁。

图9JK输出1置111翻转经过以上功能分析、设计和仿真,30s计数器的各项功能得到实现,在清零/复位与暂停/继续控制电路中,当J1闭合,暂停计数时,发光二极管点亮,J1断开,继续计数时,发光二极管灭;当J4闭合,数码管清零,发光二极管点亮,当J4断开后,发光二极管灭。

三、功能说明总结实现从29到00的30秒倒计时计数功能,时间间隔为1s,具有启动,清零/复位与暂停/继续计数功能;同时当清零与暂停时,清零/复位或暂停/继续计数功能电路中的发光二极管点亮,作为功能标识;暂停时,数码管显示闪烁提醒,倒计时到00时计数保持00,并且闪烁报警,提示计数结束。

J1为单刀单掷开关,是暂停/继续计数功能控制开关,闭合J1,开关,计数暂停,断开J1开关,计数继续;J3为自动复位开关,时计数启动开关,当清零/复位开关断开复位后,按下J3启动计数;J4为单刀单掷开关,是清零/复位功能控制开关,闭合J3开关,数码管清零保持,再断开J3开关,复位29,等待启动开关J3启动。

四、课程设计小结课程设计过程中对学到的各种芯片的功能,作用有了更加深入的学习,尤其是通过Multisim的设计与仿真,Multisim之前没有接触过,这几天学习了其基本功能和仿真实验。

在设计30秒倒计时计数器时,用到了74LS191N加/减计数器,共阴极数码管,74LS48N译码器,555定时器组成多谐振荡器电路,JK触发器和D触发器等元器件,对这些元器件的特性,功能有了进一步深入的了解。

通过555定时器构成多谐振荡电路的仿真对其电路结构有了更深刻的印象,掌握了通过改变RC的值对振荡周期进行调整。

当然在设计各各功能的过程中也遇到了许多问题,如最初使用74LS191N加/减计数器的时候对其反馈和异步置数功能不是很清楚,在查阅书本和实践多次的基础上终于解决异步置数问题,又如在设计反馈控制电路的过程中,时选用JK触发器还是D触发器,最初的设想是用的JK触发器,但是实验多次后才觉得如果用D触发器会更好,最终用D触发器实现清零/复位控制电路和计数器反馈电路;另一个问题是倒计时计数到00时的保持与闪烁问题,当计数到00时,74LS191N的MAX/MIN端输出将从低电平变为高电平,试了不少方法,有些无法保持00状态,有些在00状态无法闪烁,最终通过反馈两个74LS191N的MAX/MIN端与非两次后的输控制D触发器U21的SET端控制低位74LS191N的使能端CTEN端(即EN端)实现保持00计数状态,并利用JK触发器的翻转和置1功能特性控制74LS48译码器的BI/RBO端输入实现闪烁功能。

每遇到一个问题都时进一步学习和加深对电路,原理,元器件学习的过程,每解决一个问题,没实现一个功能,都会十分的兴奋,总之,课程设计是一个提高能力,实践所学知识的过程,当然,还有许多的元器件,电路原理等有待于进一步的学习,对Multisim的学习也是一个开始,希望今后也能进一步学习到更多这一功能强大仿真软件的功能。

参考文献:艾永乐付子义《数字电子计数基础》2008 [北京] 中国电力出版社;邱关源罗先觉《电路》第五版2011 [北京] 高等教育出版社;《Multisim原件介绍》百度文库;附录:一、电路原理图二、元器件明细表555定时器1个七段共阴极红色数码管2个74LS48N译码器2个74LS191N加/减计数器2个74LS00(四-2输入与非门)2个(一共需要7个2输入与非门)74LS02(四-2输入或非门)1个(共需要2个或非门)D触发器3个JK触发器2个电容2个(C1 1uF,C2 10nF)。