集成电路版图设计师培训

- 格式:pdf

- 大小:85.57 KB

- 文档页数:1

电路图培训计划一、培训背景电路图是电子工程中的重要工具,用来描述电路中各个元件之间的连接关系。

掌握电路图的绘制和阅读技能对于电子工程师来说是至关重要的。

因此,为了提高员工的电路图绘制能力和工作效率,我们计划进行一次电路图培训。

二、培训目标1. 让员工掌握基本的电路图符号和常见的电路图元件。

2. 提高员工的电路图绘制能力,能够根据实际需求绘制各种复杂的电路图。

3. 增强员工的电路图阅读能力,能够准确理解和分析电路图中的信息。

4. 培养员工的团队合作意识,提高工作效率和质量。

三、培训内容1. 电路图的基本概念和符号- 介绍电路图的概念和作用- 讲解电路图中常见的符号和元件,如电源、电阻、电容、电感等2. 电路图的绘制方法- 介绍常见的电路图绘制软件,如CAD、Altium Designer等- 演示电路图的绘制步骤和技巧- 练习绘制简单的电路图3. 电路图的阅读与分析- 演示电路图的阅读方法,如如何分析电路图中的电流路径、电压分布等- 练习阅读和分析复杂的电路图4. 团队合作与海报设计- 设计一个小组项目,要求小组成员合作绘制一个复杂的电路图- 每个小组根据自己设计的电路图,制作相应的海报,为其他员工解读电路图四、培训实施1. 培训形式- 采用线上线下相结合的方式进行培训,包括在线直播、视频课程和实地操作。

- 将培训内容分为多个阶段,每个阶段安排一次集中培训和多次分散练习。

2. 培训时间- 总计培训时间为两个月,每周安排两次培训课程,每次课程时间为两小时。

3. 培训课程安排- 第一周:介绍电路图的基本概念和符号,培训员工基本的电路图绘制方法。

- 第二周:练习绘制简单的电路图,并进行互评和讨论。

- 第三周:讲解电路图的阅读与分析方法,演示如何分析电路图中的电流路径和电压分布。

- 第四周:练习阅读和分析复杂的电路图,培训员工在小组中进行合作练习。

- 第五周至第八周:设计一个小组项目,小组成员合作绘制一个复杂的电路图,并为其他员工解读电路图。

总结集成电路培训内容,重点描述最感兴趣、对自身工作指导性最强

1. 基础知识:集成电路的定义、历史、发展进程、基本构成单元、常用工艺、材料及其特性、尺寸、制造流程

2. 设计流程:设计前的准备工作、电路设计原理、模拟/数字设计的基本流程、验证与仿真、版图设计、电性能分析等。

3. 工具使用:常见EDA工具的使用、设计规范、模拟与验证工具的使用、版图设计工具的使用、检查与修复工具的使用等。

4. 应用案例分析:将所学的知识应用到实际的集成电路设计中,分析不同应用场景下的实际设计案例,掌握实践经验和技巧。

对于自身工作指导性最强的内容,一般建议关注以下几个方面:

1. 设计流程和工具使用:集成电路设计需要遵循一定的流程,并使用专业的EDA工具进行设计、验证和仿真。

了解这些步骤和工具的使用,可以有效提高设计效率,降低出错率,并使自身工作更加规范和系统化。

2. 版图设计:版图设计是实现电路设计的最后一步,也是最为关键的一步。

需要注意的是,版图设计中一些微小的错误可能会导致整个电路失效,因此应重视版图设计中的各项规格和流程,以确保电路可以正常工作。

3. 应用案例分析:集成电路设计的应用场景非常广泛,因此了解不同应用场景的需求和设计要求,对于自身的工作指导性也是非常有帮助的。

通过分析实际的设计案例,可以更好地掌握设计技能和经验,提高自身的工作质量和效率。

集成电路版图设计师职业标准(试行)一.、职业概况1.1职业名称集成电路版图设计师1.2职业定义通过EDA设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII数据。

1.3 职业等级本职业共设四个等级,分别是版图设计员(职业资格四级)、助理版图设计师(职业资格三级)、版图设计师(职业资格二级)、高级版图设计师(职业资格一级)。

1.4 职业环境条件室内、常温1.5 职业能力特征具有良好的电脑使用基础与较强的外语阅读能力;具备一定的半导体微电子基础理论。

具有很强的学习能力。

1.6 基本文化程度理工科高等专科学历。

1.7 培训要求1.7.1 培训期限全日制职业学校教育:根据其培养目标和教学计划确定。

晋级培训期限:版图设计员不少于240标准学时;助理版图设计师不少于240标准学时;版图设计师不少于200标准学时;高级版图设计师不少于180标准学时。

1.8 鉴定要求1.8.1 适用对象从事或准备从事集成电路版图设计的人员。

1.8.2 申报条件以上各等级申报条件均参照“关于职业技能鉴定申报条件的暂行规定”1.8.3 鉴定方式分为理论知识考试和技能操作考核。

技能操作考核采用上机实际操作方式,由3-5名考评员组成考评小组,根据考生现场操作表现及实际操作输出结果,按统一标准评定得分。

两项鉴定均采用100分制,皆达60分及以上者为合格。

1.8.4 考评人员与考生理论知识考试:平均15名考生配一名考评员。

技能操作考核:平均5-8 名考生配1名考评员。

1.8.5 鉴定时间理论知识考试:设计员、助理设计师90分钟,设计师、高级设计师120分钟。

技能操作考核:设计员、助理设计师90分钟,设计师、高级设计师120分钟。

1.8.6 鉴定场地设备用于理论知识考试的标准教室;用于操作技能考试的场所:具有EDA设计平台和网络教学系统等设备和软件,不少于20个考位。

二、基本要求三、工作要求本标准对版图设计员(四级)、助理版图设计师(三级)、版图设计师(二级)和高级版图设计师(一级)的工作内容和职业能力要求依次递进,高级别覆盖低级别。

模拟集成电路设计实习培训内容介绍培训目的经过本培训,学员将会学到在模拟集成电路设计过程中的绝大部分环节。

1.学会使用数模混合集成电路设计EDA工具进行简单的模拟集成电路设计的流程,包括Cadence的Virtuoso原理图输入、版图设计,Cadence的Spectre电路仿真,及Mentor Graphics 的Calibre版图规则检查(DRC)、电路图版图一致性检查(LVS)。

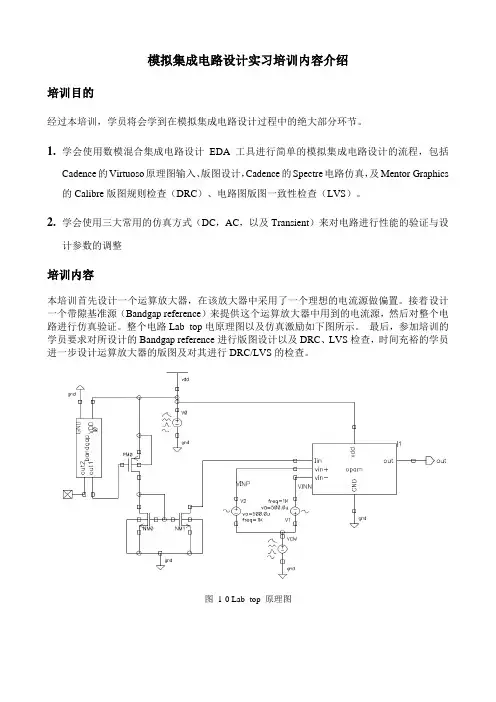

2.学会使用三大常用的仿真方式(DC,AC,以及Transient)来对电路进行性能的验证与设计参数的调整培训内容本培训首先设计一个运算放大器,在该放大器中采用了一个理想的电流源做偏置。

接着设计一个带隙基准源(Bandgap reference)来提供这个运算放大器中用到的电流源,然后对整个电路进行仿真验证。

整个电路Lab_top电原理图以及仿真激励如下图所示。

最后,参加培训的学员要求对所设计的Bandgap reference进行版图设计以及DRC、LVS检查,时间充裕的学员进一步设计运算放大器的版图及对其进行DRC/LVS的检查。

图1-0 Lab_top 原理图上图中的运算放大器(opam)电路如下图所示,值得注意的是,该运算放大器需要一个current sink做偏置,该current sink由上图中的NM1来提供。

其中的bandgap电路如下图。

Schematic 到layout的Quick start一、Schematic (opam)1. 运行虚拟机vmware;2. 在虚拟机界面中打开并运行CentOS.vmx;3. 用户登陆,登录名:eda,登录密码:123456;4. 界面按鼠标右键->选Open Terminal进入eda根目录下的命令行界面;5. 输入csh并回车;6. 输入icfb&命令后台运行Cadence的工具进入icfb界面。

图1-1 icfb的主界面在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell由多个CellView组成,CellView可以是schematic(电路原理)和layout(版图)或symbol(符号),或者其他Cadence工具所调用的hspiceS等。

集成电路版图设计学习计划一、学习目标1. 掌握集成电路版图设计的基本原理和流程2. 熟练掌握版图设计工具及其使用技巧3. 能够独立完成简单的集成电路版图设计和验证4. 深入了解当前集成电路设计的前沿技术和发展趋势二、学习内容1. 基础知识学习(1)集成电路原理(2)版图设计基础(3)版图设计工具的使用2. 实践项目(1)完成若干简单的版图设计项目(2)参与某个复杂的版图设计项目3. 前沿技术学习(1)学习并掌握新型版图设计工具(2)研究当前集成电路设计的前沿技术和趋势三、学习计划和安排1. 第一阶段(一个月)(1)学习基础知识,包括集成电路原理和版图设计基础(2)使用版图设计工具进行简单的练习(3)阅读相关书籍和论文,对集成电路版图设计有一个初步了解2. 第二阶段(两个月)(1)参与一个简单的版图设计项目,并在导师的指导下完成(2)学习并掌握版图设计工具的高级使用技巧(3)针对项目中出现的问题进行总结和学习3. 第三阶段(三个月)(1)参与某个复杂的版图设计项目(2)深入学习前沿技术和趋势,包括新型版图设计工具和技术(3)关注和研究当前集成电路设计的前沿技术四、学习方法和途径1. 师傅领进门,修行靠个人在学习的过程中,我将争取多向导师请教、向同行交流,查找相关资料和论文,同时注重自己的动手实践和尝试。

2. 多方面学习针对集成电路版图设计的不同领域和方向,我将综合利用书籍、网络资源、实验和项目等多种途径,努力拓宽自己的知识面和视野。

3. 注重实践实践是检验理论的有效途径,我将尽可能参与各种实际项目和练习,将理论知识转化为实际能力。

5. 学习成果的检验1)定期进行实践项目的检验和总结2)对一些重要的知识点进行定期的答辩或演讲3)在实际项目的合作中检验自己的设计能力和技巧六、学习风险和应对措施1)知识面过于宽泛,很难专精某一个方向应对措施:合理规划学习计划,结合实际项目进行学习,注重实践。

2)对前沿技术和趋势了解不深入应对措施:关注一些学术交流和讨论,认真阅读相关论文和杂志,多参与行业研讨会和讲座。

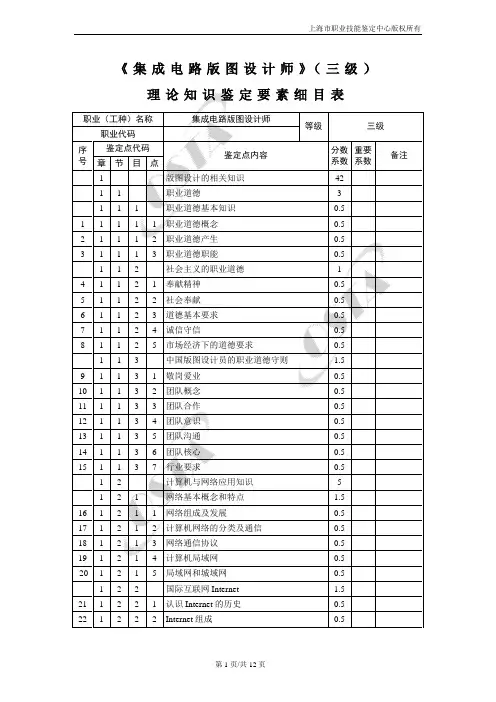

《集成电路版图设计师》(三级)理论知识鉴定要素细目表职业(工种)名称集成电路版图设计师等级三级职业代码序号鉴定点代码鉴定点内容分数系数重要系数备注章节目点1 版图设计的相关知识421 1 职业道德 31 1 1 职业道德基本知识0.51 1 1 1 1 职业道德概念0.52 1 1 1 2 职业道德产生0.53 1 1 1 3 职业道德职能0.51 12 社会主义的职业道德 14 1 1 2 1 奉献精神0.55 1 1 2 2 社会奉献0.56 1 1 2 3 道德基本要求0.57 1 1 2 4 诚信守信0.58 1 1 2 5 市场经济下的道德要求0.51 1 3 中国版图设计员的职业道德守则 1.59 1 1 3 1 敬岗爱业0.510 1 1 3 2 团队概念0.511 1 1 3 3 团队合作0.512 1 1 3 4 团队意识0.513 1 1 3 5 团队沟通0.514 1 1 3 6 团队核心0.515 1 1 3 7 行业要求0.51 2 计算机与网络应用知识 51 2 1 网络基本概念和特点 1.516 1 2 1 1 网络组成及发展0.517 1 2 1 2 计算机网络的分类及通信0.518 1 2 1 3 网络通信协议0.519 1 2 1 4 计算机局域网0.520 1 2 1 5 局域网和城域网0.51 2 2 国际互联网Internet 1.521 1 2 2 1 认识Internet的历史0.522 1 2 2 2 Internet组成0.523 1 2 2 3 Internet的地址0.524 1 2 2 4 Internet的域名0.525 1 2 2 5 Internet的服务0.526 1 2 2 6 Internet的特点及应用[1] 0.527 1 2 2 7 Internet的特点及应用[2] 0.51 2 3 显微镜的使用 228 1 2 3 1 显微镜的基本知识0.529 1 2 3 2 显微镜的结构0.530 1 2 3 3 显微镜的光学参数0.531 1 2 3 4 显微镜的安放调节0.532 1 2 3 5 显微镜的使用操作流程0.533 1 2 3 6 物镜和照相目镜的选择0.534 1 2 3 7 分辨率的选择0.535 1 2 3 8 显微镜的维护[1] 0.536 1 2 3 9 显微镜的维护[2] 0.537 1 2 3 10 显微镜的维护[3] 0.51 3 半导体物理知识121 3 1 半导体物理基本理论 3.538 1 3 1 1 半导体基本性质0.539 1 3 1 2 晶体结构0.540 1 3 1 3 能带0.541 1 3 1 4 半导体掺杂0.542 1 3 1 5 掺杂时的能级0.543 1 3 1 6 能级与能带0.544 1 3 1 7 带隙0.545 1 3 1 8 载流子0.546 1 3 1 9 非平衡载流子0.547 1 3 1 10 非平衡载流子的扩散0.548 1 3 1 11 载流子迁移率0.51 32 半导体器件基础知识8.549 1 3 2 1 pn结结构[1] 0.550 1 3 2 2 pn结结构[2] 0.551 1 3 2 3 pn结的偏置0.552 1 3 2 4 pn结的击穿0.553 1 3 2 5 二极管的击穿0.554 1 3 2 6 肖特基二极管0.555 1 3 2 7 双极型器件0.556 1 3 2 8 双极型器件导电0.557 1 3 2 9 双极型器件工作模式0.558 1 3 2 10 双极型器件特性参数0.559 1 3 2 11 双极型晶体管放大倍数0.560 1 3 2 12 MOS管结构0.561 1 3 2 13 MOS管工作原理0.562 1 3 2 14 MOS管工作0.563 1 3 2 15 MOS管的阈值电压[1] 0.564 1 3 2 16 MOS管的阈值电压[2] 0.565 1 3 2 17 NMOS衬底偏置效应0.566 1 3 2 18 PMOS衬底偏置效应0.567 1 3 2 19 FET和NPN晶体管的开关特性0.568 1 3 2 20 器件综述0.569 1 3 2 21 失效机制0.570 1 3 2 22 静电泻放0.571 1 3 2 23 静电放电保护和衬底耦合0.572 1 3 2 24 电迁移和介质击穿0.573 1 3 2 25 天线效应[1] 0.574 1 3 2 26 天线效应[2] 0.575 1 3 2 27 反相器[1] 0.576 1 3 2 28 反相器[2] 0.577 1 3 2 29 CMOS 模拟电路-常用单元0.578 1 3 2 30 CMOS 模拟电路运算放大器0.579 1 3 2 31 集成电路设计0.51 4 半导体器件的基本制造工艺191 4 1 集成电路基础知识 1.580 1 4 1 1 集成电路发明0.581 1 4 1 2 集成电路的概念[1] 0.582 1 4 1 3 集成电路的概念[2] 0.583 1 4 1 4 器件特点0.584 1 4 1 5 集成电路设计简介0.51 42 集成电路制造工艺885 1 4 2 1 工艺概论0.586 1 4 2 2 二氧化硅性质及作用0.587 1 4 2 3 二氧化硅的生长0.588 1 4 2 4 二氧化硅的制备0.589 1 4 2 5 光刻0.590 1 4 2 6 去胶0.591 1 4 2 7 光刻流程0.592 1 4 2 8 刻蚀0.593 1 4 2 9 扩散概论0.594 1 4 2 10 扩散原理0.595 1 4 2 11 离子注入[1] 0.596 1 4 2 12 离子注入[2] 0.597 1 4 2 13 淀积概论0.598 1 4 2 14 淀积原理0.599 1 4 2 15 PECVD 0.5 100 1 4 2 16 二氧化硅化学气相淀积0.5 101 1 4 2 17 多晶硅和氮化硅的气相淀积0.5 102 1 4 2 18 单晶硅的化学气相淀积0.5 103 1 4 2 19 接触和互连0.5 104 1 4 2 20 外延生长0.5 105 1 4 2 21 外延技术0.5 106 1 4 2 22 氧化工艺0.5 107 1 4 2 23 CVD硅外延反应剂0.5 108 1 4 2 24 光刻工艺0.5 109 1 4 2 25 刻蚀工艺0.5 110 1 4 2 26 掺杂[1] 0.5 111 1 4 2 27 掺杂[2] 0.5 112 1 4 2 28 工艺-综合0.5 113 1 4 2 29 IC制作工艺0.51 4 3 外围器件及阻容元件设计7 114 1 4 3 1 场开启[1] 0.5 115 1 4 32 场开启[2] 0.5 116 1 43 3 隔离环概念0.5 117 14 3 4 隔离环连接0.5 118 1 4 3 5 隔离环作用0.5 119 1 4 36 倒比管0.5 120 1 4 37 集成电路的电阻0.5 121 1 4 38 方块电阻0.5 122 1 4 39 无源电阻0.5 123 1 4 3 10 集成电路中的电容器0.5 124 1 4 3 11 压焊块版图设计0.5 125 1 4 3 12 金属膜互连0.5 126 1 4 3 13 电源和地线0.5 127 1 4 3 14 对寄生的考虑0.5 128 1 4 3 15 集成电路设计中的寄生[1] 0.5129 1 4 3 16 集成电路设计中的寄生[2] 0.5 130 1 4 3 17 对Latch-up的抑制0.5 131 1 4 3 18 电路静电防护0.5 132 1 4 3 19 运算放大器电路设计0.5 133 1 4 3 20 MOS管的表面势0.5 134 1 4 3 21 集成电容器0.5 135 1 4 3 22 集成电感设计准则0.51 4 4 半导体器件的基本制造工艺 2.5 136 1 4 4 1 典型的双极集成电路制造工艺流程0.5137 1 4 4 2 双极集成电路中元件的形成过程和元件结构0.5138 1 4 4 3 MOS工艺概述0.5 139 1 4 4 4 PMOS工艺/NMOS工艺0.5 140 1 4 4 5 CMOS工艺0.5 141 1 4 4 6 双阱CMOS工艺0.5 142 1 4 4 7 BiCMOS工艺0.5 143 1 4 4 8 隐埋层0.5 144 1 4 4 9 外延层考虑因素0.5 145 1 4 4 10 工艺综述0.5 146 1 4 4 11 金属互连及多层布线0.51 5 模拟版图设计 31 5 1 版图设计概论 3 147 1 5 1 1 模拟和数字电路比较0.5 148 1 5 12 模拟版图设计0.5 149 1 5 13 铝栅CMOS 0.5 150 1 5 14 双极型晶体管的设计0.5 151 1 5 1 5 双极型晶体管的设计步骤0.5 152 1 5 16 双极型NPN 0.5 153 1 5 17 横向PNP晶体管0.5 154 1 5 18 纵向PNP 0.5 155 1 5 19 双极型版图设计基本规则0.5 156 1 5 1 10 双极型版图设0.5 157 1 5 1 11 典型TTL和CMOS电路0.5 158 1 5 1 12 版图设计技巧0.52 集成电路版图设计582 1 Unix操作系统和cadence软件152 1 1 SUN工作站简况、SOLARIS操作系统 2.5 159 2 1 1 1 UNIX、LINX的历史、发展和特点0.5160 2 1 1 2 常用管理命令的使用[1] 0.5 161 2 1 1 3 常用管理命令的使用[2] 0.5 162 2 1 1 4 常用管理命令的使用[3] 0.5 163 2 1 1 5 Vi编辑器的使用0.5 164 2 1 1 6 Bourne shell和C-SHELL基础0.5 165 2 1 1 7 系统管理知识简介0.5 166 2 1 1 8 用户管理知识简介0.5 167 2 1 1 9 UNIX网络管理知识0.5168 2 1 1 10 WWW、FTP、EMAIL、NIS、NFS等网络服务0.52 1 2 Unix基础知识7 169 2 1 2 1 UNIX操作系统0.5 170 2 1 2 2 改变目录0.5 171 2 1 23 目录操作[1] 0.5 172 2 1 24 目录操作[2] 0.5 173 2 1 2 5 文件操作0.5 174 2 1 26 文件显示0.5 175 2 1 27 文件权限0.5 176 2 1 28 命令处理0.5 177 2 1 29 权限更改0.5 178 2 1 2 10 命令处理器0.5 179 2 1 2 11 命令处理器提示符0.5 180 2 1 2 12 命令与进程[1] 0.5 181 2 1 2 13 命令与进程[2] 0.5 182 2 1 2 14 使用vi 0.5 183 2 1 2 15 退出vi 0.5 184 2 1 2 16 vi中光标移动0.5 185 2 1 2 17 光标移动0.5 186 2 1 2 18 屏幕控制0.5 187 2 1 2 19 正文输入0.5 188 2 1 2 20 正文的删除和查找0.52 13 EDA软件和工具概况 5 189 2 1 3 1 Cadence公司0.5 190 2 1 3 2 Cadence工具0.5 191 2 1 3 3 Synopsys公司0.5 192 2 1 34 其他EDA[1] 0.5 193 2 1 3 5 其他EDA[2] 0.5 194 2 1 36 其他EDA[3] 0.5195 2 1 3 7 EDA厂商比较0.5 196 2 1 3 8 EDA软件发展[1] 0.5 197 2 1 3 9 EDA软件发展[2] 0.5 198 2 1 3 10 EDA软件发展[3] 0.5 199 2 1 3 11 电路编辑工具0.5 200 2 1 3 12 仿真器0.5 201 2 1 3 13 版图验证工具[1] 0.5 202 2 1 3 14 版图验证工具[2] 0.5 203 2 1 3 15 自动布局布线0.5 204 2 1 3 16 版图编辑工具0.52 1 4 版图编辑环境设置0.5 205 2 1 4 1 环境文件0.5 206 2 1 4 2 环境设置0.52 2 版图的基本理论262 2 1 版图的概念、层次与相关术语 5 207 2 2 1 1 版图设计目的0.5 208 2 2 1 2 层次布线0.5 209 2 2 13 层间连线[1] 0.5 210 2 2 14 层间连线[2] 0.5 211 2 2 1 5 版图基本图形0.5 212 2 2 16 版图基本规则0.5 213 2 2 17 版图引线0.5 214 2 2 18 版图与工艺的关系[1] 0.5 215 2 2 19 版图与工艺的关系[2] 0.5 216 2 2 1 10 版图与器件性能0.5 217 2 2 1 11 英文术语[1] 0.5 218 2 2 1 12 英文术语[2] 0.5 219 2 2 1 13 英文术语[3] 0.5 220 2 2 1 14 英文术语[4] 0.5 221 2 2 1 15 英文术语[5] 0.5 222 2 2 1 16 设计规则术语解读[1] 0.5 223 2 2 1 17 设计规则术语解读[2] 0.5 224 2 2 1 18 设计规则术语解读[3] 0.52 2 2 版图设计规则和方法7 225 2 2 2 1 版图设计规则0.5 226 2 2 2 2 关于线宽[1] 0.5 227 2 2 23 关于线宽[2] 0.5 228 2 2 24 关于线宽[3] 0.5229 2 2 2 5 关于间距[1] 0.5 230 2 2 2 6 关于间距[2] 0.5 231 2 2 2 7 设计规则解析0.5 232 2 2 2 8 注意事项0.5 233 2 2 2 9 布线的合理性0.5 234 2 2 2 10 布局技巧0.5 235 2 2 2 11 全定制设计方法0.5 236 2 2 2 12 其他版图设计方法0.5 237 2 2 2 13 BJT版图设计原则0.5 238 2 2 2 14 版图的评价0.5 239 2 2 2 15 版图上抑制Latch-up 0.5 240 2 2 2 16 双极型集成电路的剖片0.5 241 2 2 2 17 双极型晶体管的设计0.5 242 2 2 2 18 符号法版图设计0.5 243 2 2 2 19 CMOS保护电路0.5 244 2 2 2 20 版图中提高可靠性的措施0.5 245 2 2 2 21 工艺上提高可靠性的措施0.5 246 2 2 2 22 可测试性设计0.52 23 基本功能电路版图设计 5 247 2 2 3 1 器件图形0.5 248 2 2 3 2 电路保护0.5 249 2 2 3 3 BJT开关特性0.5 250 2 2 34 MOS管版图原理0.5 251 2 2 3 5 场区与有源区0.5 252 2 2 36 寄生电容0.5 253 2 2 37 寄生电阻0.5 254 2 2 38 器件版图匹配0.5 255 2 2 39 ESD二极管0.5 256 2 2 3 10 集成电感0.5 257 2 2 3 11 集成电容和电阻0.5 258 2 2 3 12 集成电阻器0.5 259 2 2 3 13 MOS电容器[1] 0.5 260 2 2 3 14 MOS电容器[2] 0.5 261 2 2 3 15 内连线0.5 262 2 2 3 16 集成齐纳二极管0.52 2 4 版图的绘制9 263 2 24 1 版图库的建立0.5 264 2 2 4 2 库管理0.5265 2 2 4 3 文件的进入0.5 266 2 2 4 4 电路绘制中的快捷方式[1] 0.5 267 2 2 4 5 电路绘制中的快捷方式[2] 0.5 268 2 2 4 6 层选择窗口0.5 269 2 2 4 7 几何图形的建立0.5 270 2 2 4 8 常用版图绘制命令[1] 0.5 271 2 2 4 9 常用版图绘制命令[2] 0.5 272 2 2 4 10 常用版图绘制命令[3] 0.5 273 2 2 4 11 常用版图绘制命令[4] 0.5 274 2 2 4 12 Option菜单0.5 275 2 2 4 13 格点设置0.5 276 2 2 4 14 层次化设计0.5 277 2 2 4 15 layout 快捷键使用[1] 0.5 278 2 2 4 16 layout 快捷键使用[2] 0.5 279 2 2 4 17 Layout的基本操作[1] 0.5 280 2 2 4 18 Layout的基本操作[2] 0.5 281 2 2 4 19 常用命令[1] 0.5 282 2 2 4 20 常用命令[2] 0.5 283 2 2 4 21 环境设置0.5 284 2 2 4 22 版图层次选择0.5 285 2 2 4 23 层间连接[1] 0.5 286 2 2 4 24 层间连接[2] 0.5 287 2 2 4 25 电路的选择[1] 0.5 288 2 2 4 26 电路的选择[2] 0.52 3 设计规则和物理验证知识172 3 1 版图设计规则 4 289 2 3 1 1 硅栅CMOS设计规则[1] 0.5 290 2 3 1 2 硅栅CMOS设计规则[2] 0.5 291 2 3 1 3 硅栅CMOS设计规则[3] 0.5 292 2 3 1 4 硅栅CMOS设计规则[4] 0.5 293 2 3 1 5 硅栅CMOS设计规则[5] 0.5 294 2 3 1 6 硅栅CMOS设计规则[6] 0.5 295 2 3 1 7 硅栅CMOS设计规则[7] 0.5 296 2 3 1 8 硅栅CMOS设计规则[8] 0.5 297 2 3 1 9 硅栅CMOS设计规则[9] 0.5 298 2 3 1 10 硅栅CMOS设计规则[10] 0.5 299 2 3 1 11 规则解析—线宽[1] 0.5 300 2 3 1 12 规则解析—线宽[2] 0.5301 2 3 1 13 版图解析—间距[1] 0.5 302 2 3 1 14 版图解析—间距[2] 0.5 303 2 3 1 15 版图设计的注意事项0.52 3 2 验证工具应用 3 304 2 3 2 1 DIV A概述0.5 305 2 3 2 2 DIV A验证0.5 306 2 3 2 3 DRC验证简介0.5 307 2 3 2 4 器件提取Extraction简介0.5 308 2 3 2 5 LVS验证简介0.5 309 2 3 2 6 层次运算0.5 310 2 3 2 7 逻辑、尺寸运算命令0.5 311 2 3 2 8 逻辑操作命令0.5 312 2 3 2 9 选择、产生和保存运算命令[1] 0.5 313 2 3 2 10 选择、产生和保存运算命令[2] 0.5 314 2 3 2 11 版图验证项目0.52 3 3 DRC流程 5 315 2 3 3 1 DRC命令0.5 316 2 3 3 2 DRC/Extract文件结构0.5 317 2 3 3 3 DRC功能[1] 0.5 318 2 3 3 4 DRC功能[2] 0.5 319 2 3 3 5 DRC功能[3] 0.5 320 2 3 3 6 模型的定义和提取0.5 321 2 3 3 7 Dracula版图验证过程0.5 322 2 3 3 8 Diva DRC规则文件建立0.5 323 2 3 3 9 规则文件中命令0.5 324 2 3 3 10 Dracula 规则文件结构0.5 325 2 3 3 11 Dracula 规则文件建立0.5 326 2 3 3 12 编写Dracula 规则文件[1] 0.5 327 2 3 3 13 编写Dracula 规则文件[2] 0.5 328 2 3 3 14 运行Diva DRC 0.5 329 2 3 3 15 运行Dracula DRC 0.52 3 4 LVS 流程 3 330 2 3 4 1 LVS步骤0.5 331 2 3 4 2 LVS命令和使用0.5 332 2 3 4 3 版图数据0.5 333 2 3 4 4 Cadence数据格式转换0.5 334 2 3 4 5 网表的产生[1] 0.5 335 2 3 4 6 网表的产生[2] 0.5336 2 3 4 7 运行过程0.5 337 2 3 4 8 运行Dracula LVS 0.5 338 2 3 4 9 描述块命令解读0.5 339 2 3 4 10 输入层块命令解读0.5 340 2 3 4 11 DRC验证0.5 341 2 3 4 12 LVS验证0.5 342 2 3 4 13 其他验证0.52 3 5 版图分析 2 343 2 3 5 1 划分区域0.5 344 2 3 5 2 划分区域0.5 345 2 3 5 3 读图标线0.5 346 2 3 5 4 图形识别0.5 347 2 3 5 5 工艺模块识别0.5 348 2 3 5 6 器件图形0.5 349 2 3 5 7 保护电路0.5 350 2 3 5 8 CMOS保护电路0.5《集成电路版图设计师》(三级)操作技能鉴定要素细目表职业(工种)名称集成电路版图设计师等级三级职业代码序号鉴定点代码鉴定点内容分数系数重要系数备注项目单元点1 版图编辑70 91 1 版图基本功能单元设计25 91 1 1 1 基本数字功能电路的CMOS版图实现15 92 1 1 2 版图的合理布局布线 5 93 1 1 3 合理减小版图的面积 5 91 2 版图基本模块设计20 94 1 2 1 5个器件构成的模块版图实现10 95 1 2 2 版图的合理布局布线 5 96 1 2 3 器件之间的连接 5 91 5 版图基本模拟单元设计25 97 1 5 1 基本模拟电路的CMOS版图实现10 98 1 5 2 模拟电路的版图技巧应用10 99 1 5 3 合理减小版图的面积 5 92 版图识别30 92 1 版图错误修改20 910 2 1 1 查找连接错误 4 911 2 1 2 查找间距、线宽错误 4 912 2 1 3 查找层次错误 4 913 2 1 4 查找宽、长比错误 4 914 2 1 5 修改版图错误 4 92 2 提取电路图10 915 2 2 1 P管、N管栅长、栅宽数据的提取和实现 3 916 2 2 2 基本单元电路的版图提取 3 917 2 2 3 基本功能电路的版图提取 4 9(注:将“操作技能鉴定要素细目表”和“理论知识鉴定要素细目表”组合成为《鉴定要素细目表》)。

系统集成类项目技术培训方案目录一、前言 (2)1.1 培训背景 (2)1.2 培训目标 (3)1.3 培训对象 (4)二、培训内容概述 (4)2.1 系统集成基础知识 (5)2.2 集成项目需求分析与设计 (6)2.3 集成项目实施与部署 (7)2.4 集成项目测试与验证 (8)2.5 集成项目后期维护与优化 (9)三、培训方法与手段 (10)3.1 课堂讲授 (11)3.2 实践操作 (12)3.3 案例分析 (13)3.4 小组讨论 (15)3.5 在线学习资源 (16)四、培训课程设置 (17)4.1 系统集成基础课程 (18)4.2 集成项目实战课程 (18)4.3 集成项目管理课程 (19)4.4 集成项目质量保证课程 (21)五、培训师资 (22)5.1 师资介绍 (23)5.2 师资资质 (24)5.3 师资培养 (25)六、培训时间与地点 (26)6.1 培训时间安排 (26)6.2 培训地点选择 (27)七、培训效果评估 (29)7.1 培训效果评价标准 (30)7.2 培训效果反馈机制 (31)7.3 培训效果改进措施 (32)八、培训预算与费用 (33)8.1 培训预算编制 (34)8.2 培训费用明细 (35)一、前言随着信息技术的飞速发展,系统集成技术在各行各业中的应用越来越广泛,对于从事系统集成项目的工程师来说,掌握先进的技术和不断学习新知识变得尤为重要。

为了提高系统集成类项目工程师的专业技能,提升项目实施质量和效率,我们制定了这份系统集成类项目技术培训方案。

本培训方案旨在通过系统的理论讲解、案例分析和实践操作,使参训人员熟练掌握系统集成的基本原理、常用技术和方法,了解最新的行业动态和发展趋势。

通过培训,培养参训人员的团队协作能力、沟通能力和解决问题的能力,为他们在系统集成领域的发展奠定坚实的基础。

在接下来的章节中,我们将详细介绍培训的目标、内容、方式以及培训效果评估等内容,以帮助大家更好地理解和掌握本次培训的内容。

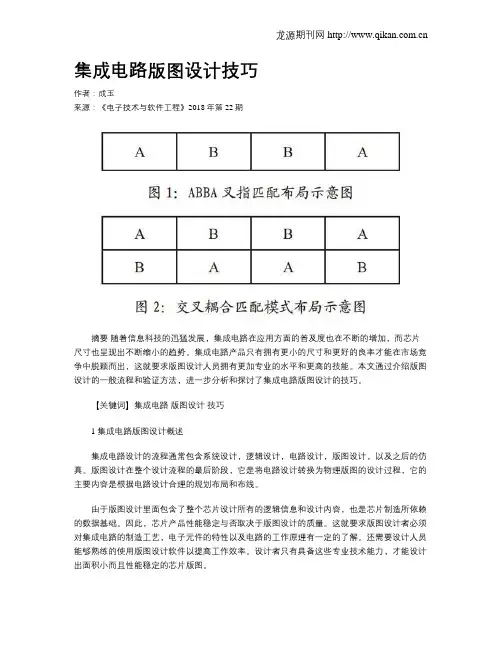

集成电路版图设计技巧作者:成玉来源:《电子技术与软件工程》2018年第22期摘要随着信息科技的迅猛发展,集成电路在应用方面的普及度也在不断的增加,而芯片尺寸也呈现出不断缩小的趋势。

集成电路产品只有拥有更小的尺寸和更好的良率才能在市场竞争中脱颖而出,这就要求版图设计人员拥有更加专业的水平和更高的技能。

本文通过介绍版图设计的一般流程和验证方法,进一步分析和探讨了集成电路版图设计的技巧。

【关键词】集成电路版图设计技巧1 集成电路版图设计概述集成电路设计的流程通常包含系统设计,逻辑设计,电路设计,版图设计,以及之后的仿真。

版图设计在整个设计流程的最后阶段,它是将电路设计转换为物理版图的设计过程,它的主要内容是根据电路设计合理的规划布局和布线。

由于版图设计里面包含了整个芯片设计所有的逻辑信息和设计内容,也是芯片制造所依赖的数据基础。

因此,芯片产品性能稳定与否取决于版图设计的质量。

这就要求版图设计者必须对集成电路的制造工艺,电子元件的特性以及电路的工作原理有一定的了解。

还需要设计人员能够熟练的使用版图设计软件以提高工作效率。

设计者只有具备这些专业技术能力,才能设计出面积小而且性能稳定的芯片版图。

目前企业应用比较多的版图设计软件是Cadence。

它的设计功能比较强大,几乎涵盖了整个集成电路设计和验证所需的大部分功能,软件界面十分人性化,软件操作也十分稳定和方便。

2 集成电路版图设计流程2.1 与电路设计者进行有效的沟通首先,在版图设计开始之前,版图设计师需要跟电路设计师取得良好的沟通。

需要了解他对于工作进度的安排,以及对版图面积的要求。

知道哪些功能模块在电路中特别重要,哪些器件需要进行高度的匹配以及哪些模块之间可以就近摆放或者需要进行相应的隔离处理。

还包括要了解电路中哪些是大电流的部分,需要多大的线宽等等一系列版图设计的细节。

版图设计师只有在设计的初始阶段尽可能多的了解和熟悉版图设计中的要点和值得注意的事项,才能在整个芯片设计过程中更有针对性的进行优化以符合电路设计师的要求。

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。

集成电路版图设计师_职业标准一.、职业概况1.1职业名称集成电路版图设计师1.2职业定义通过EDA设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII数据。

1.3 职业等级本职业共设四个等级,分别是版图设计员(职业资格四级)、助理版图设计师(职业资格三级)、版图设计师(职业资格二级)、高级版图设计师(职业资格一级)。

1.4 职业环境条件室内、常温1.5 职业能力特征具有良好的电脑使用基础与较强的外语阅读能力;具备一定的半导体微电子基础理论。

具有很强的学习能力。

1.6 基本文化程度理工科高等专科学历。

1.7 培训要求1.7.1 培训期限全日制职业学校教育:根据其培养目标和教学计划确定。

晋级培训期限:版图设计员不少于240标准学时;助理版图设计师不少于240标准学时;版图设计师不少于200标准学时;高级版图设计师不少于180标准学时。

1.8 鉴定要求1.8.1 适用对象从事或准备从事集成电路版图设计的人员。

1.8.2 申报条件以上各等级申报条件均参照“关于职业技能鉴定申报条件的暂行规定”1.8.3 鉴定方式分为理论知识考试和技能操作考核。

技能操作考核采用上机实际操作方式,由3-5名考评员组成考评小组,根据考生现场操作表现及实际操作输出结果,按统一标准评定得分。

两项鉴定均采用100分制,皆达60分及以上者为合格。

1.8.4 考评人员与考生理论知识考试:平均15名考生配一名考评员。

技能操作考核:平均5-8 名考生配1名考评员。

1.8.5 鉴定时间理论知识考试:设计员、助理设计师90分钟,设计师、高级设计师120分钟。

技能操作考核:设计员、助理设计师90分钟,设计师、高级设计师120分钟。

1.8.6 鉴定场地设备用于理论知识考试的标准教室;用于操作技能考试的场所:具有EDA设计平台和网络教学系统等设备和软件,不少于20个考位。

二、基本要求三、工作要求本标准对版图设计员(四级)、助理版图设计师(三级)、版图设计师(二级)和高级版图设计师(一级)的工作内容和职业能力要求依次递进,高级别覆盖低级别。

集成电路版图培训实验报告文件编码(008-TTIG-UTITD-GKBTT-PUUTI-WYTUI-8256)淮海工学院电子工程学院实习报告书实习名称:专业实习实习地点:苏州集成电路设计中心实习时间:—专业名称:电子科学与技术班级:电科121*名:**学号:1 引言大学生专业实习是大学学习阶段在完成一定的课程后所要进行的非常重要的一个实践环节,实习是每一个合格的大学生必须拥有的一段,它使我们在实践中增强专业意识和实践意识。

这次专业实习学校安排我们到苏州国际科技园进行为期五天的实习,在实习期间,我们得到了实习公司的大力支持,更有相关培训老师的的悉心培训指导,通过实习使我们对自己未来工作方向有了更清晰认识,为我们以后进一步走向社会打下坚实的基础。

2 实习目的专业实习是电子科学与技术专业安排在校外进行的实践性教学环节,也是在专业基础课、专业课等基本学完之后的又一次实践性教学。

其目的让学生了解实际的集成电路芯片的设计、版图绘制和检测等过程。

把学过的理论知识与实际有机结合起来,为后续专业课的学习以及以后走向工作岗位打下一定的基础。

3 实习目标(1)熟悉集成电路版图设计、集成电路测试技术、半导体器件识别等。

(2)熟悉集成电子产品制造技术,了解集成电子产品生产装配工艺和过程,生产安全操作规范。

熟悉集成电子产品检测,集成电子产品的调试。

(3)通过行业报告、参观展厅、参观封装厂等了解集成电路行业。

CMOS电路设计。

学会行业软件使用:Linux基本操作及实践练习、EDA工具培训与练习、物理版图设计的基础概念。

(4)学习现场工作人员的优秀品质和敬业精神,培养正确的劳动观念和独立工作能力。

4 实习内容(1)集成电路行业报告、实训课(测试、版图、行业软件使用)、参观展厅、参观工厂(芯片封装厂)。

(2)基础理论:集成电路行业介绍、CMOS电路设计、半导体物理。

工具使用:Linux基本操作及实践练习、EDA工具培训与练习、物理版图设计的基础概念。