3-8线译码器的74HC138芯片课程设计资料

- 格式:doc

- 大小:1.79 MB

- 文档页数:33

哈尔滨理工大学软件学院课程设计报告课程数字IC设计(双语)题目 3线-8线译码器班级集成12—1专业集成电路设计与集成系统学生张铭学号 1214020130 指导教师陆学斌2014年12月31日目录1、课程设计目的介绍………………………………………………2、课程设计题目介绍………………………………………………3、课程设计报告内容………………………………………………4、体会总结…………………………………………………………5、参考书目…………………………………………………………1.课程设计目的训练学生综合运用学过的数字集成电路的基本知识,独立设计相对复杂的数字集成电路的能力。

2.课程设计题目用与非门组成的3线-8线译码器3.课程设计报告内容3.1 设计要求按题目要求的逻辑功能进行设计,电路各个组成部分须有设计说明;必须采用网表输入法;3.2 设计内容拿到题目后首先进行电路设计。

然后在微机上进行HSPICE网表输入、编译和软件仿真,满足设计要求。

3.3 查找有关书籍设计电路原理图3.4 根据原理图编写网表*74 HC138.include 'd:\lib\180nm_bulk.l'.param Supply=1.8.global Vdd Gnd.opt scale=0.1uVdd Vdd Gnd 'Supply'.subckt nand ina inb inc ind outmpa out ina Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpb out inb Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpc out inc Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpd out ind Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mna out ina x Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnb x inb y Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnc y inc z Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnd z ind Gnd Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 .ends.subckt nor ina inb inc outmpa out ina x Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mpb x inb y Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mpc y inc Vdd Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mna out ina Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 mnb out inb Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 mnc out inc Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 .ends.subckt Inverter in outmpa out in Vdd Vdd PMOS l=2 w=4 ad=4 pd=4 as=20 ps=20 mpb out in Gnd Gnd NMOS l=2 w=2 ad=4 pd=4 as=10 ps=10 .endsx1 s1 s1b Inverterx2 s1b s2b s3b s norx3 a0 a0b Inverterx4 a1 a1b Inverterx5 a2 a2b Inverterx6 a0b a0bb Inverterx7 a1b a1bb Inverterx8 a2b a2bb Inverterx9 a0b a1b a2b s y0b nandx10 a0bb a1b a2b s y1b nandx11 a0b a1bb a2b s y2b nandx12 a0bb a1bb a2b s y3b nandx13 a0b a1b a2bb s y4b nandx14 a1b a2bb a0bb s y5b nandx15 a0b a2bb a1bb s y6b nandx16 a1bb a0bb a2bb s y7b nandCinv y1b Gnd 6000fVs1 s1 Gnd pulse 0 'Supply' 7.5ns 200ps 200ps 130ns 140ns Vs2b s2b Gnd pulse 'Supply' 0 0ns 200ps 200ps 100ns 110ns Vs3b s3b Gnd pulse 'Supply' 0 0ns 200ps 200ps 65ns 75ns Va0 a0 Gnd pulse 0 'Supply' 0ns 200ps 200ps 17.5ns 35ns Va1 a1 Gnd pulse 0 'Supply' 0ns 200ps 200ps 40ns 80ns Va2 a2 Gnd pulse 0 'Supply' 0ns 200ps 200ps 70ns 140ns .tran 100ps 140ns.plot tran V(s1).end3.5画图编写3线—8线译码器的功能表说明:s1 s2b s3b 为附加的控制端,当s1 = 1,s2b + s3b = 0时,译码器处于工作状态,否则译码器被禁止,所有的输出端被封锁在高电平。

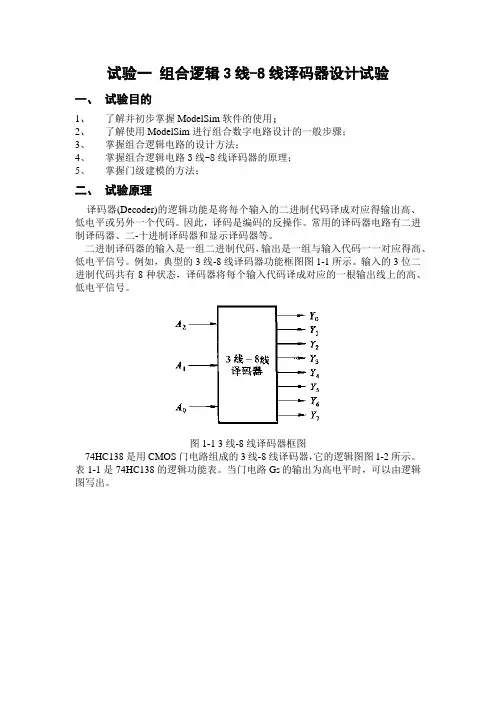

试验一组合逻辑3线-8线译码器设计试验一、试验目的1、了解并初步掌握ModelSim软件的使用;2、了解使用ModelSim进行组合数字电路设计的一般步骤;3、掌握组合逻辑电路的设计方法;4、掌握组合逻辑电路3线-8线译码器的原理;5、掌握门级建模的方法;二、试验原理译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应得输出高、低电平或另外一个代码。

因此,译码是编码的反操作。

常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器等。

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应得高、低电平信号。

例如,典型的3线-8线译码器功能框图图1-1所示。

输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图1-1 3线-8线译码器框图74HC138是用CMOS门电路组成的3线-8线译码器,它的逻辑图图1-2所示。

表1-1是74HC138的逻辑功能表。

当门电路G S的输出为高电平时,可以由逻辑图写出。

图1-2 74HC138逻辑功能图表1-1 74HC138逻辑功能表由上式可以看出,由''07Y Y -同时又是210,,A A A 这三个变量的全部最小项的译码输出,所以也将这种译码器称为最小项译码器。

74HC138有3个附加的控制端''123,S S S 和。

当''123S 1,S S 0=+=时,s G 输出为高电平,译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁为高电平。

这3个控制端也称为“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能;三、 预习要求1、数字电子技术基础组合逻辑电路设计一般设计方法;2、74HC138的逻辑功能;3、门级建模的一般方法和基本语句;4、ModelSim 软件的一般使用方法(ModelSim SE Tutorial);四、 实验步骤(一)、熟悉ModelSim 软件环境 1、建立一个新Project1-1双击左面快捷方式或者电击[程序]/[ModelSim SE 6.1f]/[ModelSim]启动ModelSim 6.1(如图1-3);注意:必须首先关闭IMPORTANT Information 对话框才能开始其它操作;图1-31-2 [File]/[New]/[Project…]新建一个project,会弹出Create Project对话框(如图1-4);图1-4⏹Project Name(项目名称)需要填入你所建立的项目的名称;⏹指定项目所在路径;如果所指定的目录不存在,会弹出对话框提示是否建立这个目录;一般选择是;⏹缺省的工作库名;注意:1、路径一般不应包含汉字;2、逻辑应在ModelSim的安装目录下指定;3、缺省的工作库的名称一般不需要改动;2、载入HDL元文件2-1设定好1-2步骤的每项内容后,点击OK,弹出Add items to the Projects对话框;如图1-5所示。

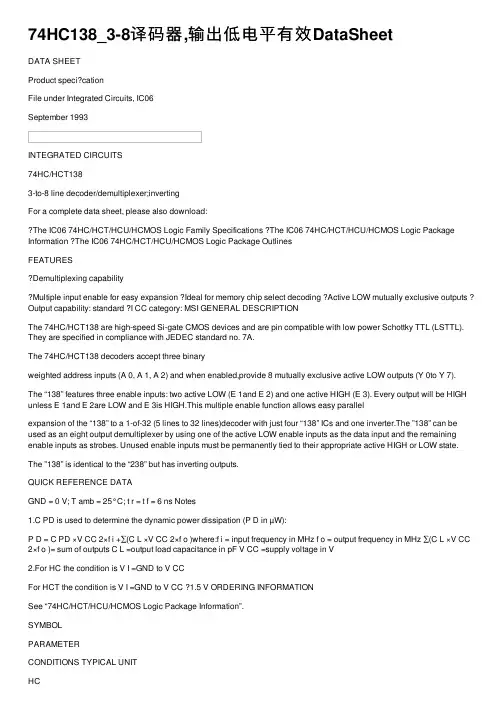

74HC138_3-8译码器,输出低电平有效DataSheetDATA SHEETProduct speci?cationFile under Integrated Circuits, IC06September 1993INTEGRATED CIRCUITS74HC/HCT1383-to-8 line decoder/demultiplexer;invertingFor a complete data sheet, please also download:The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications The IC06 74HC/HCT/HCU/HCMOS Logic Package Information ?The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURESDemultiplexing capabilityMultiple input enable for easy expansion Ideal for memory chip select decoding Active LOW mutually exclusive outputs Output capability: standard ?I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT138 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT138 decoders accept three binaryweighted address inputs (A 0, A 1, A 2) and when enabled,provide 8 mutually exclusive active LOW outputs (Y 0to Y 7).The “138” features three enable inputs: two active LOW (E 1and E 2) and one active HIGH (E 3). Every output will be HIGH unless E 1and E 2are LOW and E 3is HIGH.This multiple enable function allows easy parallelexpansion of the “138” to a 1-of-32 (5 lines to 32 lines)decoder with just four “138” ICs and one inverter.The ”138” can be used as an eight output demultiplexer by using one of the active LOW enable inputs as the data input and the remaining enable inputs as strobes. Unused enable inputs must be permanently tied to their appropriate active HIGH or LOW state.The ”138” is identical to the “238” but has inverting outputs.QUICK REFERENCE DATAGND = 0 V; T amb = 25°C; t r = t f = 6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D = C PD ×V CC 2×f i +∑(C L ×V CC 2×f o )where:f i = input frequency in MHz f o = output frequency in MHz ∑(C L ×V CC 2×f o )= sum of outputs C L =output load capacitance in pF V CC =supply voltage in V2.For HC the condition is V I =GND to V CCFor HCT the condition is V I =GND to V CC ?1.5 V ORDERING INFORMATIONSee “74HC/HCT/HCU/HCMOS Logic Package Information”.SYMBOLPARAMETERpropagation delayC L = 15 pF; V CC = 5 Vt PHL / t PLH A n to Y n 1217ns t PHL / t PLH E 3to Y n E n to Y n1419ns C I input capacitance3.5 3.5pF C PD power dissipation capacitance per packagenotes 1 and 26767pFPIN DESCRIPTION PIN NO.SYMBOL NAME AND FUNCTION 1, 2, 3A 0to A 2address inputs4, 5E 1,E 2enable inputs (active LOW)6E 3enable input (active HIGH)8GND ground (0 V)15, 14, 13, 12, 11, 10, 9, 7Y 0 to Y 7outputs (active LOW)16V CCpositive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.handbook, halfpageMLB312A 0A 1A 212315131179101214Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7456E 1E 2E 3Fig.3 IEC logic symbol.(a)(b)Fig.4 Functional diagram.FUNCTION TABLENotes1.H =HIGH voltage levelL =LOW voltage level X =don’t careINPUTSOUTPUTS E 1E 2E 3A 0A 1A 2Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7H X X X H X X X L X X X X X X X X X H H H H H H H H H H H H H H H H H H H H H H H H L L L L L L L L H H H H L H L H L L H H L L L L L H H H H L H H H H L H H H H L H H H H H H HL L H HH H H HH H H HH H H HH H H HH H H HL H H HH L H HH H L HH H H LFig.5 Logic diagram.DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standard I CC category: MSIAC CHARACTERISTICS FOR 74HCGND = 0 V; t r= t f= 6 ns; C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25?40to+85?40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayA n to Y n411512150304538ns2.04.56.0Fig.6t PHL/ t PLH propagation delay E3to Y n471714150302619038332254538ns2.04.56.0Fig.6t PHL/ t PLH propagation delay E n to Y n471738332254538ns2.04.56.0Fig.7t THL/ t TLH output transitiontime19767515139519161102219ns2.04.56.0Figs 6 and 7DC CHARACTERISTICS FOR 74HCTI CC per input, multiply this value by the unit load coefficient shown in the table below.AC CHARACTERISTICS FOR 74HCT GND = 0 V; t r = t f = 6 ns; C L = 50 pFINPUT UNIT LOAD COEFFICIENT A n 1.50E n 1.25E 31.00SYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS 74HCTV CC (V)WAVEFORMS +25?40to +85?40to +125min.typ.max.min.max.min.max.t PHL / t PLH propagation delay A n to Y n20354453ns 4.5Fig.6t PHL / t PLH propagation delay E 3to Y n18405060ns 4.5Fig.6t PHL / t PLH propagation delay E n to Y n19405060ns 4.5Fig.7t THL / t TLHoutput transition time7151922ns4.5Figs 6 and 7AC WAVEFORMS(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.6Waveforms showing the address input (A n)and enable input (E3) to output (Y n) propagation delays and the output transition times.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.7Waveforms showing the enable input (E n) to output (Y n)propagation delays and the output transition times. PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。

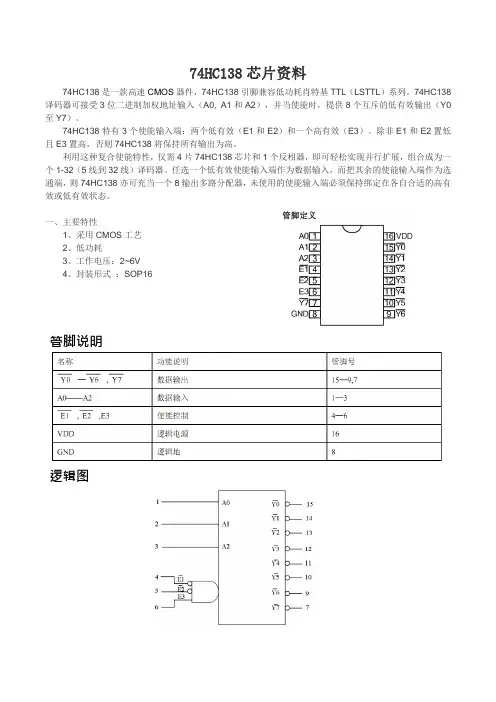

74HC138芯片资料74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

一、主要特性1、采用CMOS工艺2、低功耗3、工作电压:2~6V4、封装形式:SOP16管脚说明逻辑图真值表:电气参数正常工作范围(Ta=-40~+80℃)参数符号最小典型最大单位测试条件逻辑电源电压VDD 3.0 5.0 5.5 V -高电平输入电压V IH 3.0 V VDD=5.0V 低电平输入电压V IL 2.0 V VDD=5.0V极限参数(Ta=25℃)参数符号范围单位逻辑电源电压VDD -0.5~+7.0 V逻辑输入电压VII -0.5~ VDD+0.5 V 功率损耗PD <400 mW工作温度Topt -40~+80 ℃储存温度Tstg -50~+150 ℃直流特性参数 符号 最小 典型 最大 单位 测试条件 高电平输出电压 V OH 4.9 V VDD=5.0V 低电平输出电压 V OL 0.1 V VDD=5.0V 静态电流损耗 IDD 1 uA VDD=6.0V 输出端口驱动电流 I OH -32 -40 mA VDD=5.0V I OL46 56 mA VDD=5.0V交流特性参数符号 最小 典型 最大 单位 测试条件 输出上升延时 t PLH 4 ns VDD=5.0V F=250KHz C L =30P波形图见图一 测试电路见图二输出下降延时 t PHL 5 ns 输出上升沿 t r 5 ns 输出下降沿 t f5ns。

实验六 3线8线译码器及其应用一、实验目的1、掌握中规模集成电路译码器的工作原理及逻辑功2、学习译码器的灵活应用。

二、实验设备及器件1、实验箱(台) 1套2、数字万用表 1块3、74LS138 3-8线译码器 2片4、74LS20 二四输入与非门 1片三、实验内容与步骤74LS138管脚图见附录。

当控制输入端S1=1,时,译码器工作,否则译码器禁止,所有输出端均为高电平。

1、译码器逻辑功能测试(1)按图13-1接线。

根据表13-1,利用开关设置S1、、、及A2、A1、A0的状态,借助指示灯或万用表观测~的状态,记入表13-1中。

2、用两片74LS138组成4-16线译码器按图13-2接线,利用开关改变输入D0-D3的状态,借助指示灯或万用表监测输出端,记入表13-2中,写出各输出端的逻辑函数。

图13-2表13-2 输入输出D 3D2D1D0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 13、利用译码器组成全加器线路用74LS138和74LS20按图13-3接线,74LS20芯片14脚接 +5v,7脚接地。

利用开关改变输入A i、B i、C i-1的状态,借助指示灯或万用表观测输出S i、C i的状态,记入表13-3中,写出输出端的逻辑表达式。

图13-3表13-3 输入输出S 1AiBiCi-1SiCi0ΦΦΦ10001001101010111100110111101111四、实验要求:1、整理各步实验结果,列出相应实测真值表。

2、总结译码器的逻辑功能及灵活应用情况。

3、交出完整的实验报告。

实验五 3-8线译码器一、实验目的:1、熟悉常用译码器的功能逻辑。

2、掌握复杂译码器的设计方法。

二、实验原理:1、总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

2、3-8线译码器原理图如下图所示:三、实验连线:1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上。

四、实验步骤:按照步骤三正确连线,参考实验二步骤,完成项目的建立,文件的命名,文件的编辑,语法检查,引脚分配,编译,下载。

实验参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY shiyan5 ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END shiyan5;ARCHITECTURE ADO OF shiyan5 ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;IF(DIN="000") THEN OUTA<="00111111" ;D_OUT<="00000000"; --"0"ELSIF(DIN="001") THEN outa<="00000110" ;D_OUT<="00000001"; --"1" ELSIF(DIN="010") THEN outa<="01011011";D_OUT<="00000010"; --"2" ELSIF(DIN="011") THEN outa<="01001111";D_OUT<="00000100"; --"3" ELSIF(DIN="100") THEN outa<="01100110";D_OUT<="00001000"; --"4" ELSIF(DIN="101") THEN outa<="01101101";D_OUT<="00010000"; --"5" ELSIF(DIN="110") THEN outa<="01111101";D_OUT<="00100000"; --"6"ELSIF(DIN="111") THEN outa<="00000111";D_OUT<="01000000"; --"7"ELSE OUTA<="XXXXXXXX";D_OUT<="XXXXXXXX";END IF;END PROCESS;END ADO;五、实验现象:(程序:EP2C5\dencode\dencode.sof)3-8线译码器的三个输入C、B、A分别对应拨位开关SW3,SW2,SW1,改变SW3,SW2,SW1的位置,以改变C、B、A 的状态,于LED1上观察译码实验结果。

贵州大学

电路EDA电路技术课程考

核报告

姓名:田泽民

学号:PZ082014131 班级:08级计维班

一、实验目的:

1、会PSpice软件的仿真应用。

2、知道全加器的原理,进行仿

真。

二、实验名称:

仿真用与非门组成的3-8译码器(74HC138)。

三、实验内容:

画出电路图,进行参数的设置,截图,分析得到仿真结果。

四、实验原理:

译码器74HC138有三个附加的控制端,当状态为(1,0,0)时,译码器工作。

输入端A2,A1,A0;输出端Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7.

五、实验过程:

1、实验电路:

2、参数设置:

DSTM4、DSTM5、DSTM6高低电平交互的时间分别设为:4ms、2ms 和1ms,0—30ms,步长为5ms

3、仿真结果:

从上图可以看出,当输入端为000的时候选择Y0输出,当输入端为001的时候选择Y1输出……

010 Y2 011 Y3 100 Y4

101 Y5 110 Y6 111 Y7

4、真值表对照:

5、结果截图(与理论值相符):

六、实验结论:

本次实验,所得到的显示结果与预计:完全相同,因而证明本次实验是正确的。

七、实验总结:

进行参数设置的时候,时间不能设得太短,最好是以(ms)为单位。

在输入端时间设置应该注意取到每个输入组合,否则实验就不一定仿真出真实的结果。

DATA SHEETProduct specificationFile under Integrated Circuits, IC06September 199374HC/HCT1383-to-8 line decoder/demultiplexer;invertingFor a complete data sheet, please also download:•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications •The IC06 74HC/HCT/HCU/HCMOS Logic Package Information •The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURES•Demultiplexing capability•Multiple input enable for easy expansion •Ideal for memory chip select decoding •Active LOW mutually exclusive outputs •Output capability: standard •I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT138 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT138 decoders accept three binaryweighted address inputs (A 0, A 1, A 2) and when enabled,provide 8 mutually exclusive active LOW outputs (Y 0to Y 7).The “138” features three enable inputs: two active LOW (E 1and E 2) and one active HIGH (E 3). Every output will be HIGH unless E 1and E 2are LOW and E 3is HIGH.This multiple enable function allows easy parallelexpansion of the “138” to a 1-of-32 (5 lines to 32 lines)decoder with just four “138” ICs and one inverter.The ”138” can be used as an eight output demultiplexer by using one of the active LOW enable inputs as the data input and the remaining enable inputs as strobes. Unused enable inputs must be permanently tied to their appropriate active HIGH or LOW state.The ”138” is identical to the “238” but has inverting outputs.QUICK REFERENCE DATAGND = 0 V; T amb = 25°C; t r = t f = 6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D = C PD ×V CC 2×f i +∑(C L ×V CC 2×f o )where:f i = input frequency in MHz f o = output frequency in MHz ∑(C L ×V CC 2×f o )= sum of outputs C L =output load capacitance in pF V CC =supply voltage in V2.For HC the condition is V I =GND to V CCFor HCT the condition is V I =GND to V CC −1.5 V ORDERING INFORMATIONSee “74HC/HCT/HCU/HCMOS Logic Package Information”.SYMBOLPARAMETERCONDITIONS TYPICAL UNITHCHCTpropagation delayC L = 15 pF; V CC = 5 Vt PHL / t PLH A n to Y n 1217ns t PHL / t PLH E 3to Y n E n to Y n1419ns C I input capacitance3.5 3.5pF C PD power dissipation capacitance per packagenotes 1 and 26767pFPIN DESCRIPTION PIN NO.SYMBOL NAME AND FUNCTION 1, 2, 3A 0to A 2address inputs4, 5E 1,E 2enable inputs (active LOW)6E 3enable input (active HIGH)8GND ground (0 V)15, 14, 13, 12, 11, 10, 9, 7Y 0 to Y 7outputs (active LOW)16V CCpositive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.handbook, halfpageMLB312A 0A 1A 212315131179101214Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7456E 1E 2E 3Fig.3 IEC logic symbol.(a)(b)Fig.4 Functional diagram.FUNCTION TABLENotes1.H =HIGH voltage levelL =LOW voltage level X =don’t careINPUTSOUTPUTS E 1E 2E 3A 0A 1A 2Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7H X X X H X X X L X X X X X X X X X H H H H H H H H H H H H H H H H H H H H H H H H L L L L L L L L H H H H L H L H L L H H L L L L L H H H H L H H H H L H H H H L H H H H H H H H H H H H H H H H L L L L L L L LH H H HL H L HL L H HH H H HH H H HH H H HH H H HH H H HL H H HH L H HH H L HH H H LFig.5 Logic diagram.DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standardI CC category: MSIAC CHARACTERISTICS FOR 74HCGND = 0 V; t r= t f= 6 ns; C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayA n to Y n411512150302619038332254538ns2.04.56.0Fig.6t PHL/ t PLH propagation delayE3to Y n471714150302619038332254538ns2.04.56.0Fig.6t PHL/ t PLH propagation delayE n to Y n471714150302619038332254538ns2.04.56.0Fig.7t THL/ t TLH output transitiontime19767515139519161102219ns2.04.56.0Figs 6 and 7DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standard I CC category: MSI Note to HCT typesThe value of additional quiescent supply current (∆I CC ) for a unit load of 1 is given in the family specifications. To determine ∆I CC per input, multiply this value by the unit load coefficient shown in the table below.AC CHARACTERISTICS FOR 74HCT GND = 0 V; t r = t f = 6 ns; C L = 50 pFINPUT UNIT LOAD COEFFICIENT A n 1.50E n 1.25E 31.00SYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS 74HCTV CC (V)WAVEFORMS +25−40to +85−40to +125min.typ.max.min.max.min.max.t PHL / t PLH propagation delay A n to Y n20354453ns 4.5Fig.6t PHL / t PLH propagation delay E 3to Y n18405060ns 4.5Fig.6t PHL / t PLH propagation delay E n to Y n19405060ns 4.5Fig.7t THL / t TLHoutput transition time7151922ns4.5Figs 6 and 7AC WAVEFORMS(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.6Waveforms showing the address input (A n)and enable input (E3) to output (Y n) propagation delays and the output transition times.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.7Waveforms showing the enable input (E n) to output (Y n)propagation delays and the output transition times.PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。

74HC138中文资料(功能,真值表,引脚图)

74HC138功能:

CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS*器,适合内存地址*或数据路由应用。

74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

74HC138真值表:

74HC238真值表:

74HC138引脚图:

图1 引脚图。

集成电路课程设计----含2个2-4线译码器的74HC139芯片一.目的与任务本课程设计是《集成电路分析与设计》的实践课程,其主要目的是为了在了解了集成电路的基本结构的基础上进一步的学习集成电路的设计,本次设计通过对TANNER TOOLS PRO工具的使用让我们能够从简单入手到能设计一个完整的芯片,。

并进行电路仿真对比。

二.课程设计题目、内容及要求2.1 设计题目1.器件名称:一个3-8译码器的74HC138芯片;2.要求的电路性能指标:(1)可驱动10个LSTTL电路(相当于15pF电容负载);(2)输出高电平时,︱IoH︱≤20uA,Voh,min=4.4V;(3)输出低电平时,︱IoL︱≤4mA,Vol,max=0.4V;(4)输出级充放电时间tr = tf,tpd<25ns;(5)工作电源5V,常温工作,工作频率fwork =30MHz,总功耗Pmax=150mW。

2.2 设计内容(1)功能分析及逻辑设计(2)电路设计(3)估算功耗与延时(4)电路模拟与仿真(5)版图设计(全手工、层次化设计)(6)版图检查:DRC与LVS(7)后仿真(选做)(8)版图数据提交2.3 设计要求(1)独立完成设计74HC138 芯片的全过程;(2)设计时使用的工艺及设计规则:MOSIS:mamin08;(3)根据所用的工艺,选取合理的模型库;(4)选用以lambda(λ)为单位的设计规则;(5)全手工、层次化设计版图;(6)达到指导书提出的设计指标要求。

三、74HC139电路简介3.1 通用74HC139芯片的引脚图74HC139芯片包含两个2-4译码器,它的通用引脚图入图1其中,(1A0、1A1)和(2A0、2A1)分别为两个译码器的地址输入端,而1E (以下取名为Csa )和2E (以下取名为Csb )分别为两个译码器的使能端(低电平有效),1Y0~1Y7和2Y0~2Y7为译码器的数据输出端。

3.2通用74HC139的真值表 通用74HC139的真值表如表一3.3通用74HC139的逻辑表达式根据表一,我们可以很容易得到一下的逻辑表达式 Y0=E+A1+A0=01A A E ∙∙ Y1=E+A1+0A =01A A E ∙∙ Y2=E+1A +A0=01A A E ∙∙ Y3=E+1A +0A =01A A E ∙∙3.4通用74HC139的逻辑图,如图2所示图二所示为通用74HC139芯片的其中一个译码器的逻辑图。

74hc138 3-8线译码器/复工器哈里斯(Texas Instruments)CD74HC138 ,CD74HC238和CD74HCT138 ,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

74HC138 74HCT138 T1TRUTH TABLE真值功能表INPUTS输入Outputs输出ENABLE使能ADDRE SS地址E 3E2E1A2A1A0Y0Y1Y2Y3Y4Y5Y6Y7X X H X X X H H H H H H H HL X X X X X H H H H H H H HX H X X X X H H H H H H H HH L L L L L L H H H H H H HH L L L L H H L H H H H H HH L L L H L H H L H H H H HH L L L H H H H H L H H H HH L L H L L H H H H L H H HH L L H L H H H H H H L H HH L L H H L H H H H H H L HH L L H H H H H H H H H H LAbsolute Maximum Ratings绝对最大额定值DC Supply V oltage, VCC 直流供电电压-0.5V to 7VDC Input Diode Current, IIKFor VI < -0.5V or VI > VCC + 0.5V 输入二极管电流±20mADC Output Diode Current, IOKFor VO < -0.5V or VO > VCC + 0.5V直流输出二极管电流±20mADC Output Source or Sink Current per Output Pin, IOFor VO > -0.5Vor VO < VCC + 0.5V±25mADC VCC or Ground Current, ICC or IGND直流电流虚拟通道连接或接地±50mA Operating Conditions 操作条件Temperature Range (TA) 温度范围-55℃ to 125℃Supply V oltage Range, VCC 电源电压范围,虚拟通道连接HC Types2V to 6V HCT Types 4.5V to 5.5VDC Input or Output V oltage, VI, VO 输入或输出直流电压0V to VCCInput Rise and Fall Time输入上升和下降时间2V 1000ns (Max) 4.5V 500ns (Max) 6V . 400ns (Max)Thermal Information热特性Thermal Resistance (Typical, Note 3)热电阻qJA (℃/W) PDIP 封装90SOIC 封装115SSOP 封装155 Maximum Junction Temperature最高结温150℃Maximum Storage Temperature Range储存温度范围-65℃ to 150℃Maximum Lead Temperature 焊接温度(Soldering 10s)(SOIC -Lead Tips Only)300℃DC SPECIFICA TIONS直流电气规格:Paramete r 参数符号T est Condition测试条件VCC25℃-40℃TO85℃-55℃to125℃Unit单位VI(V)IO(mA)(V)最小典型最大最小最大最小最大High Level Input VIH--21.5-- 1.5- 1.5-V4.5 3.-- 3.1- 3.15-V oltage输入高电平电压15564.2-- 4.2- 4.2-Low LevelInputV oltage输入低电平电压VIL--2--0.5-0.5-0.5V4.5--1.35-1.35- 1.356-- 1.8- 1.8- 1.8High Level OutputV oltage输出高电平电压CMOS Loads VOHVIHorVIL-0.0221.9-- 1.9- 1.9-V4.54.4-- 4.4- 4.4-65.9-- 5.9- 5.9-High Level OutputV oltage输出高电平电压TTL Loads ----------4 4.53.98--3.84- 3.7--5.265.48--5.34- 5.2-Low Level OutputV oltage输出低电平电压CMOS Loads VOLVIHorVIL0.022--0.1-0.1-0.1V4.5--0.1-0.1-0.16--0.1-0.1-0.1Low Level OutputV oltage输出低电平电压TTL Loads ---------4 4.5--0.26-0.33-0.4 5.26--0.26-0.33-0.4InputLeakage Current输入漏电流IIVCCorGND-6--±0.1-±1-±1μAQuiescent Device Current静ICCVCCor06--8-80-160μA态电源电流GN DDC SPECIFICA TIONS直流电气规格(续)Parameter 参数SYMBOL符号T est Condition测试条件VCC25℃-40℃ TO85℃-55℃ TO 125℃Unit单位VI(V)IO (mA)(V)最小典型最大最小最大最小最大High Level Input V oltage VIH-- 4.5 to 5.52--2-2-VLow Level Input V oltage输入低电平电压VIL-- 4.5 to 5.5--0.8-0.8-0.8VHigh Level OutputV oltage输出高电平电压CMOS LoadsVOH VIHorVIL-0.024.54.4--4.4-4.4-VHigh Level OutputV oltage输出高电平电压TTL Loads -4 4.53.98--3.84-3.7-VLow Level OutputV oltage输出低电平电压CMOS Loads VOL VIHorVIL0.024.5--0.1-0.1-0.1VLow Level OutputV oltage输出低电平电压TTL Loads 4 4.5--0.26-0.33-0.4VInput Leakage Current输入漏电流IIVCCandGND0 5.5-±0.1-±1-±1μAQuiescent Device Current ICCVCCorGN0 5.5--8-80-160μADAdditional Quiescent Device Current Per Input Pin: 1 Unit 单位 Load (Note 4)DI CCV C C -2.1-4.5 to5.5- 100 360-450-490μASwitching Specifications Input tr, tf = 6ns 开关规格Parameter 参数SYM BOL 符号T est Condition 测试条件SVC C (V ) 25℃ -40℃ TO 85℃-55℃ TO 125℃ Unit 单位S最小 典型 最大最小最大 最小最大Propagation Delay 传播延迟 Address to Output 地址输出 tPLH, tPHLCL = 50pF2- - 150 -190 - 225 ns4.5 - -30 - 38 - 45 ns CL = 15pF 5 - 13 - - - - - ns CL = 50pF6- -26- 33-38ns应用电路(点击放大):舞台发光二极管灯光可编程时钟定时器电路74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

项目三3线-8线译码器电路设计

班级:09电信姓名:朱丽丝学号:41

1.实训目标

1)通过3线-8线译码器的设计,让学生掌握组合逻辑电路的设计方法。

2)掌握译码器的设计原理。

3)掌握Altera MAX+PLUS II原理图输入设计和VHDL语言输入设计的全过程。

2.实训原理

3线-8线译码器的真值表见表3-1。

表3-1

3.实训步骤

1)利用原理图编辑法,在Mf函数的maxplus2里面调用74138器件(3线-8线译码

器),加入输入和输出引脚。

编程器件型号选择ACE1k系列的EP1K30TC144-3。

完成项目编辑及功能仿真。

2)采用文本编辑法,即利用VHDL语言描述3线-8线译码器,代码如下。

然后对其进行编译,编程器件型号选择ACE1k系列的EP1K30TC144-3,完成程序仿真,记录仿真数据。

4.实训数据

1)原理图编辑法设的3线-8线译码器的电路。

2)原理图编辑法仿真结果。

简述仿真波形的意义。

3)采用VHDL语言设计的3线-8线译码器的仿真结果。

简述仿真波形的意义。

5.思考题

根据BCD-7段显示译码器的真值表,见表4-2,用VHDL语言描述BCD-7段显示译码器。

进行编辑和仿真,写出设计的VHDL程序,并记录仿真数据。

课程设计任务书学生姓名:陈莲专业班级:自动化0607指导教师:李向舜工作单位:自动化学院题目: 3线-8线译码器初始条件:1.以上版本软件;2.课程设计辅导资料:“数字电路EDA入门”、“VHDL程序实例集”、“EDA技术与VHDL”、“EDA与数字系统设计”等;3.先修课程:电路、电子设计EDA、电子技术基础等。

4.要紧涉及的知识点:门电路、组合逻辑电路、时序逻辑电路等。

要求完成的要紧任务:(包括课程设计工作量及其技术要求,和说明书撰写等具体要求)1.课程设计时刻:1周;2.课程设计内容:依照指导教师给定的题目,按规定选择其中1套完成;3.本课程设计统一技术要求:研读辅导资料对应章节,对选定的设计题目进行理论分析,针对具体设计部份的原理分析、建模、必要的推导和可行性分析,画出程序设计框图,编写程序代码(含注释),上机调试运行程序,记录实验结果(仿真结果),并对实验结果进行分析和总结。

具体设计要求包括:①温习EDA的相关技术与方式;②把握VHDL或Verilog语言,并要求能编写程序。

③Quartus软件的利用:把握程序编辑、编译、调试、仿真方式。

④设计相关简单的电路,完成既定的功能。

4.课程设计说明书按学校“课程设计工作标准”中的“统一书写格式”撰写,具体包括:①目录;②译码器相关的理论分析、归纳和总结;③3线-8线译码器的结构组成、原理分析及真值表。

④程序设计框图、程序代码(含注释);⑤给出程序中要紧函数或语句的功能说明和利用说明;⑥给出程序仿真运行结果和图表、和实验结果分析和总结;⑦课程设计的心得体会(至少500字);⑧参考文献;⑨其它必要内容等。

时刻安排:指导教师签名:年月日系主任(或责任教师)签名:年月日摘要本次能力拓展训练要求设计一个3线-8线译码器,要紧在于分析3线-8线译码器的组成和其实现原理,本次拓展训练要紧目的在于研读辅导资料对应章节,对选定的设计题目进行理论分析,针对具体设计部份的原理分析、建模、必要的推导和可行性分析,画出程序设计框图,编写程序代码,上机调试运行程序,记录实验结果,并对实验结果进行分析和总结。

实验三3-8译码器的设计

一.实验目的:

1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、初步掌握VHDL语言的常用语句。

3、掌握VHDL语言的基本语句及文本输入的EDA设计方法。

二、设计要求

设计一个3—8译码器使其满足如下真值表:

1.采用原理图输入法利用门电路进行设计并实现仿真、下载。

2.利用VHDL语言输入进行设计并进行仿真。

三、预习要求:

1.熟悉3-8译码器原理

2.根据原理绘制原理图。

3.初步写出VHDL语言程序。

四、实验记录

1.原理图及源程序。

2.仿真波形。

(两种方法)

3.延时分析。

(两种方法)。

课程设计课程名称集成电路课程设计题目名称 74HC138芯片3-8线译码器学生学院材料与能源学院专业班级学号学生姓名指导教师2015年7 月 11 日目录【摘要】...........................................................................................................................................................1. 设计目的与任务....................................................................................................................................- 1 -2. 设计要求及内容....................................................................................................................................- 1 -3. 设计方法及分析....................................................................................................................................- 2 -3.1 74HC138芯片简介 ......................................................................................................................- 2 -3.2 工艺和规则及模型文件的选择 .................................................................................................- 3 -3.3 电路设计......................................................................................................................................- 4 -3.3.1 输出级电路设计.............................................................................................................- 4 -3.3.2.内部基本反相器中的各MOS 尺寸的计算................................................................- 6 -3.3.3.四输入与非门MOS尺寸的计算.................................................................................- 7 -3.3.4.三输入与非门MOS尺寸的计算.................................................................................- 8 -3.3.5.输入级设计...................................................................................................................- 9 -3.3.6.缓冲级设计.................................................................................................................- 10 -3.3.7.输入保护电路设计................................................................................................... - 11 -3.4. 功耗与延迟估算.......................................................................................................................- 13 -3.4.1. 模型简化........................................................................................................................- 13 -3.4.2. 功耗估算........................................................................................................................- 14 -3.4.3. 延迟估算........................................................................................................................- 14 -3.5. 电路模拟...................................................................................................................................- 15 -3.5.1 直流分析.........................................................................................................................- 16 -3.5.2 瞬态分析.......................................................................................................................- 18 -3.5.3 功耗分析.......................................................................................................................- 20 -3.6. 版图设计...................................................................................................................................- 21 -3.6.1 输入级的设计...............................................................................................................- 21 -3.6.2 内部反相器的设计.......................................................................................................- 22 -3.6.3 输入和输出缓冲门的设计 ...........................................................................................- 22 -3.6.4 三输入与非门的设计...................................................................................................- 23 -3.6.5 四输入与非门的设计...................................................................................................- 24 -3.6.6 输出级的设计...............................................................................................................- 24 -3.6.7 调用含有保护电路的pad元件 ...................................................................................- 25 -3.6.8 总版图...........................................................................................................................- 25 -3.7. 版图检查...................................................................................................................................- 25 -3.7.1 版图设计规则检查(DRC).......................................................................................- 25 -3.7.2 电路网表匹配(LVS)检查........................................................................................- 26 -3.7.3 后模拟...........................................................................................................................- 26 -4. 经验与体会..........................................................................................................................................- 27 -5. 参考文献..............................................................................................................................................- 28 - 附录A:74HC138电路总原理图 ...........................................................................................................- 29 - 附录B:74HC138 芯片版图....................................................................................................................- 30 -【摘要】现代社会正在飞速的发展,集成电路已经成为现代科技发展的支柱产业,现代技术产业的心脏,可以说,没有集成电路,就没有现代社会。