锁存器和触发器进入不可预测状态的分析与解决方法

- 格式:doc

- 大小:360.00 KB

- 文档页数:6

实验报告课程名称:实验项目名称:锁存器、触发器功能测试及应用专业:报告人:学号:班级:实验时间:天津城建大学控制与机械工程学院1.基本RS锁存器基本RS锁存器可以是由两个与非门在输出端交互反馈组成双稳态存储电路。

图1所示为用与非门构成的基本RS锁存器。

图1用与非门构成的基本RS锁存器74LS00外引线排列和逻辑符号如图2所示:图2 74LS00的外引线排列图2.D触发器D触发器在时钟脉冲CP的前沿(上升沿01)触发翻转,触发器的次态取决于CP脉冲上升沿来到之前D端的状态,特性方程为 = Dn。

因此,它具置0、置1两种功能。

在CP = 0、CP = 1期间和下降沿到来,D端的数据状态变化,都不会影响触发器的输出状态。

图3 74LS74逻辑符号图图4 74LS74引脚排列图3.JK触发器JK触发器(74HC112)是一种利用传输延迟时间的边沿JK触发器,它在时钟脉冲CP的后沿即在CP脉冲的(下降沿10)触发翻转。

本实验采用的集成芯片为74LS112型(双JK下降沿触发,带清零),引脚排列图形符号如图所示。

图5和必须接高电平。

JK触发器利用CP的下降沿触发,D触发器利用CP 的上升沿触发。

4 触发器的转换触发器的转换是在实际中是经常用到的,其方法是将两种触发器的状态方程相比较得到到J,K端的表示即可。

例如将JK触发器转换成触发器的功能。

图61.基本RS锁存器的功能测试选用一片74LS00组成一个RS锁存器。

按图1连接好测试电路,按照表1中条件,观察并记录锁存平触发的特点。

表1基本RS锁存器的功能表功能0 00 11 01 12.JK触发器的功能测试根据图5,选用74LS112,按表2要求测试74LS112的逻辑功能,观察并记录触发器输出端(1)直接复位、置位端的功能测试,体会它决定触发器初态的作用。

(2)逻辑功能的测试。

要求在不同的输入状态和初始状态下测试输出端状态。

表2 JK触发器功能测试表CP J K0 1 ×××1 0 ×××1 1 ↓0 01 1 ↓0 01 1 ↓0 11 1 ↓0 11 1 ↓ 1 01 1 ↓ 1 01 1 ↓ 1 11 1 ↓ 1 11 1 ↑ 1 13.JK触发器构成触发器按图6连接好测试电路,用实验室提供的连续脉冲做时钟脉冲,用示波器观测并记录CP和Q的表3 分频作用波形图波形CP4.D触发器的功能测试选用74LS74,按表4要求测试74LS74的逻辑功能,观察并记录触发器输出端的变化情况。

电路中的触发器与锁存器电路中的触发器和锁存器是数字电子电路中非常重要的组件。

它们在计算机、通信设备和各种数字系统中起着关键的作用。

触发器和锁存器可以存储和传输二进制数据,是数字电路中的存储单元。

一、触发器触发器是一种多稳态逻辑电路,可以存储和处理二进制数据。

它可以将输入信号通过时钟脉冲的触发而切换到输出端。

触发器有两个稳态,即使时钟信号停止,触发器的输出也会保持不变。

在数字电路中,常用的触发器有SR触发器、D触发器、JK触发器和T触发器等。

SR触发器是最简单的触发器之一,它有两个输入端,分别是S (Set,设定)和R(Reset,复位)。

当S和R都为低电平时,输出保持不变;当S为高电平,R为低电平时,输出为高电平;当S为低电平,R为高电平时,输出为低电平;而当S和R都为高电平时,则为禁止状态。

D触发器也是一种常用的触发器,它只有一个输入端D。

当时钟信号到来时,输入端的值被传送到输出端。

这使得D触发器非常适用于数据存储、寄存器和移位寄存器等应用。

JK触发器是一种可改变输出状态的触发器。

它有两个输入端,分别是J(Set)和K(Reset)。

当时钟信号到来时,JK触发器的输出将根据J、K的状态进行切换。

当J和K同时为1时,输出反转;当J和K同时为0时,输出保持上一个状态不变;当J为1,K为0时,输出为1;而当J为0,K为1时,输出为0。

T触发器是一种特殊的JK触发器,它只有一个输入端T(Toggle,翻转)。

当时钟信号到来时,T触发器的输出将根据输入端的状态进行翻转。

如果T为1,输出翻转;如果T为0,输出保持不变。

二、锁存器锁存器是一种用来存储和传输二进制数据的电路。

它可以在时钟信号的作用下,将数据保持在输出端,并在时钟信号改变时刷新数据。

常用的锁存器有RS锁存器、D锁存器和JK锁存器等。

RS锁存器和SR触发器的工作原理类似,有两个输入端R和S,用于设置和复位。

当R和S同时为0时,输出保持不变;当R为1,S为0时,输出为1;当R为0,S为1时,输出为0;而当R和S同时为1时,则为禁止状态。

一、锁存器锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。

锁存器也称为透明锁存器,指的是不锁存时输出对于输入是透明的。

锁存器(latch):我听过的最多的就是它是电平触发的,呵呵。

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。

(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DA TA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DA TA_IN的值传给Q,也就是锁存的过程)。

应用场合:数据有效迟后于时钟信号有效。

这意味着时钟信号先到,数据信号后到。

在某些运算器电路中有时采用锁存器作为数据暂存器。

缺点:时序分析较困难。

不要锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比ff要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff来组成锁存器,这样就浪费了资源。

优点:面积小。

锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

二、触发器触发器(Flip-Flop,简写为FF),也叫双稳态门,又称双稳态触发器。

是一种可以在两种状态下运行的数字逻辑电路。

触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。

当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发。

三态输出触发器和锁存器实验报告有数据1. 理解三态输出触发器和锁存器的工作原理;2. 掌握三态输出触发器和锁存器的实验方法;3. 熟悉使用示波器进行实验测量和数据分析。

实验器材:- 简易逻辑实验箱- 三态输出触发器芯片(例如74LS373)- 锁存器芯片(例如74LS175)- 计时器芯片(例如555)- 示波器- 电源和电线等其他辅助器材实验原理:1. 三态输出触发器(Tri-state Output Flip-Flop):三态输出触发器是一种特殊的双稳态触发器,其输出可以处于三种状态之一: 高电平、低电平和高阻态(High-Z)。

利用一个使能端(Enable)来控制输出状态,当使能端为低电平时,输出处于高阻态,此时输出不受触发器的状态控制;当使能端为高电平时,输出由触发器的状态决定。

74LS373是一种广泛使用的三态输出触发器芯片,其引脚功能如下(以16位为例):- D0 ~ D15: 数据输入端,用于输入要存储的数据;- OE:输出使能端,用于控制输出状态;- LE:锁存使能端,用于控制存储操作;- Q0 ~ Q15: 输出端,输出存储的数据。

实验中,我们将通过控制OE和LE端的电平来实现三态输出触发器的控制和数据存储。

2. 锁存器(Latch):锁存器是一种具有存储功能的触发器,可以通过控制使能端来实现数据的锁存和释放。

常见的锁存器有SR锁存器和D锁存器等。

74LS175是一种广泛使用的锁存器芯片,其引脚功能如下(以四位为例):- D0 ~ D3: 数据输入端,用于输入要存储的数据;- EN: 使能端,用于控制存储操作;- Q0 ~ Q3: 输出端,输出存储的数据。

实验中,我们将通过控制EN端的电平来实现锁存器的控制和数据存储。

实验步骤:实验一: 三态输出触发器实验1. 连接电路: 将74LS373芯片插入实验箱中,并按照引脚功能连接电路,包括数据输入端、输出端、输出使能端和锁存使能端等。

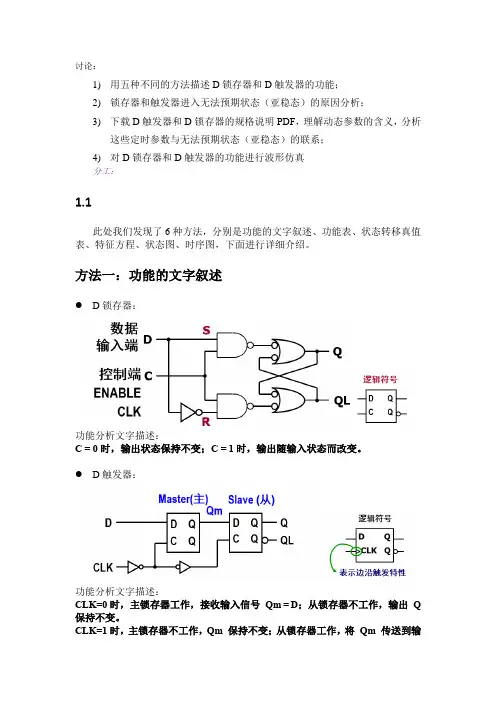

1)用五种不同的方法描述D锁存器和D触发器的功能;2)锁存器和触发器进入无法预期状态(亚稳态)的原因分析;3)下载D触发器和D锁存器的规格说明PDF,理解动态参数的含义,分析这些定时参数与无法预期状态(亚稳态)的联系;4)对D锁存器和D触发器的功能进行波形仿真分工:1.1此处我们发现了6种方法,分别是功能的文字叙述、功能表、状态转移真值表、特征方程、状态图、时序图,下面进行详细介绍。

方法一:功能的文字叙述●D锁存器:功能分析文字描述:C = 0时,输出状态保持不变;C = 1时,输出随输入状态而改变。

●D触发器:功能分析文字描述:CLK=0时,主锁存器工作,接收输入信号Qm = D;从锁存器不工作,输出Q 保持不变。

CLK=1时,主锁存器不工作,Qm 保持不变;从锁存器工作,将Qm 传送到输方法二:功能表●D锁存器功能表D触发器功能表方法三:状态转移真值表●D锁存器状态转移真值表D触发器状态转移真值表方法四:特征方程●D锁存器特征方程:Q n+1 = D(C=1)●D触发器特征方程:Q n+1 = D方法五:状态图●D锁存器状态图●D锁存器状态图方法六:时序图●D锁存器时序图●D触发器时序图1.2什么是亚稳态:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

●锁存器进入亚稳态的原因:⏹对于S-R锁存器:1.当S=R=1,然后同时取消时;2.当S和R端输入信号脉冲宽度过窄时;3.当S和R端输入信号同时取反时;均会出现亚稳态。

⏹对于D触发器:当输入信号脉冲宽度过窄时,会进入亚稳态。

●触发器进入亚稳态的原因:在同步系统中,如果触发器的建立时间(setup time)/保持时间(hold time)不满足要求,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。

彻底理解锁存器,让你不再为锁存器头疼!锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

分为普通锁存器和门控锁存器,普通锁存器无控制信号,输出状态始终直接由输入决定。

在实际的数字系统中,为了协调各部分的工作,往往需要有一个特定的控制信号去控制锁存器状态转换的时间,在控制信号无效时,输出保持不变,不随输入变换;当控制信号有效时,输出由输入决定,跟随输入变化。

基本锁存器门控锁存器①正是因为门控锁存器在控制信号有效的期间内,都可以接收输入信号,所以,激励信号的任何变化,都将直接引起锁存器输出状态的改变。

这时输入信号若发生多次变化,输出状态也可能发生多次变化,这一现象称为锁存器的空翻。

②其次,当门控锁存器的控制信号有效时,锁存器就变成了一个组合电路,时序逻辑电路的模型就等效为两个各组合电路互为反馈的反馈系统,因此,系统有可能会因为瞬态特性不稳定而产生振荡现象。

触发器(flip-flop)是边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内)。

(钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器)触发器分为两种,一种是主从触发器和边沿触发器。

主从触发器在时钟有效期内(主触发器)接收数据,在时钟边沿输出状态转换。

边沿触发器在时钟边沿期间,触发器才接收数据并使输出状态转换。

主从触发器目前,主从触发器基本上已经很少见了,实际使用的大都是边沿触发器。

寄存器(register):用来暂时存放参与运算的数据和运算结果。

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

区别与联系:由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。

由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

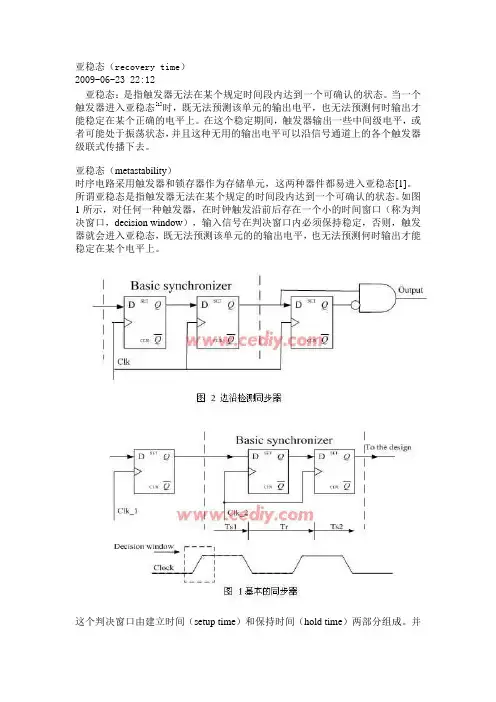

亚稳态(recovery time)2009-06-23 22:12亚稳态:是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态[1]时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

亚稳态(metastability)时序电路采用触发器和锁存器作为存储单元,这两种器件都易进入亚稳态[1]。

所谓亚稳态是指触发器无法在某个规定的时间段内达到一个可确认的状态。

如图1所示,对任何一种触发器,在时钟触发沿前后存在一个小的时间窗口(称为判决窗口,decision window),输入信号在判决窗口内必须保持稳定,否则,触发器就会进入亚稳态,既无法预测该单元的的输出电平,也无法预测何时输出才能稳定在某个电平上。

这个判决窗口由建立时间(setup time)和保持时间(hold time)两部分组成。

并且时间窗口也是多种因素的函数,包括触发器设计、实现技术、运行环境以及无缓冲输出的负载等。

输入信号陡峭的边沿可以将此窗口减至最小,随着时钟频率的升高,会出现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率会增加,即进入亚稳态的概率会增加。

亚稳态不能从根本上消除,但可以通过采取一定的措施使其对电路造成的影响降低。

[2]通常我们用故障间隔平均时间(MTBF,mean time between failures)来衡量亚稳态的影响。

MTBF越大则说明亚稳态对电路产生地影响越小,反之亦然。

如当MTBF等于几十年或者上百年时,我们就认为它对电路的影响基本上可以忽略。

实验结果表明:对于输入为异步信号的电路,其MTBF与从亚稳态状态下恢复的时间长度(如图1所示的)有着指数的关系[3]。

2 同步器(synchronizer)在实际中,我们常用的是采用两级触发器串联的同步器(如图1)[4]。

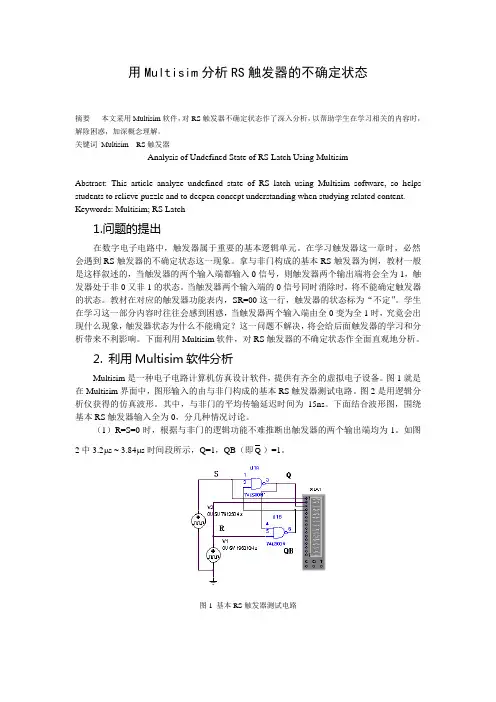

用Multisim分析RS触发器的不确定状态摘要本文采用Multisim软件,对RS触发器不确定状态作了深入分析,以帮助学生在学习相关的内容时,解除困惑,加深概念理解。

关键词Multisim RS触发器Analysis of Undefined State of RS Latch Using MultisimAbstract: This article analyze undefined state of RS latch using Multisim software, so helps students to relieve puzzle and to deepen concept understanding when studying related content. Keywords: Multisim; RS Latch1.问题的提出在数字电子电路中,触发器属于重要的基本逻辑单元。

在学习触发器这一章时,必然会遇到RS触发器的不确定状态这一现象。

拿与非门构成的基本RS触发器为例,教材一般是这样叙述的,当触发器的两个输入端都输入0信号,则触发器两个输出端将会全为1,触发器处于非0又非1的状态。

当触发器两个输入端的0信号同时消除时,将不能确定触发器的状态。

教材在对应的触发器功能表内,SR=00这一行,触发器的状态标为“不定”。

学生在学习这一部分内容时往往会感到困惑,当触发器两个输入端由全0变为全1时,究竟会出现什么现象,触发器状态为什么不能确定?这一问题不解决,将会给后面触发器的学习和分析带来不利影响。

下面利用Multisim软件,对RS触发器的不确定状态作全面直观地分析。

2. 利用Multisim软件分析Multisim是一种电子电路计算机仿真设计软件,提供有齐全的虚拟电子设备。

图1就是在Multisim界面中,图形输入的由与非门构成的基本RS触发器测试电路。

图2是用逻辑分析仪获得的仿真波形。

山东科技大学数电研究性专题《锁存器、触发器构造与性能浅析》学院:自动化学院班级:小组成员:)指导教师:一、锁存器1、锁存器介绍锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。

锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

2、锁存器工作原理CMOS反相器的功能是可以使输出获得跟输入相反的逻辑值,那如果把两个反相器的输入跟输出连接在一起会出现什么情况呢?我们来看下图,假设某个时刻反向器A的输入是1,那么其输出会是0;因为A的输出连接到B的输入端,即反相器B的输入为0,那么其输出会变为1;又因为B的输出连接到A的输入端,即B输出的1反馈回A的输入,对刚才假设的“A的输入为1”进行了确认和加强。

此时A的输入确实为1,按A和B的输入输出连接关系,又走了一遍刚才的路程,如此循环,结果是反相器A的输出稳定为0,反相器B的输出稳定为1。

这个结构的电路有两个稳定的状态,一般称之为双稳态电路。

可见类似的双稳态电路可以稳定地保持其节点中的值(数据),具有记忆功能,这就是锁存器工作的原理。

从上面介绍可看出,首尾相接的两个反相器构成了互相反馈耦合的形态,这就是锁存器的基本电路结构。

但是这里是基于一个假设,假设反相器A的输入为1,那么它的输出为0,两个反相器连在一起通过互相反馈加强,则能保持0和1两个值。

如果没有这个假设,它能保存的值将是不确定的。

这类似于“鸡生蛋还是蛋生鸡”的谜局,要将此电路当锁存器使用,就必须打破这个“是输入先有0,还是输出先反馈回1”的僵局。

于是给它加了两个输入端,由于反相器只有1个输入,因此改用或非门来代替。

电路结构如下图,根据或非门“只要有一个输入为1,其输出就为0”的特性,当R为1时,虽然有反馈存在,也可以强制输出Q=0;当S为1时,则强制输出Q=1。

电子电路中常见的触发器问题及解决方法电子电路中触发器是一种重要的数字电路元件,用于存储和传输二进制信号。

在实际应用中,触发器也常常会遇到一些问题。

本文将介绍电子电路中常见的触发器问题,并探讨相应的解决方法。

一、RS触发器的问题及解决方法RS触发器是最为基础的触发器之一,由于其简单可靠的特点,在数字电路中得到广泛应用。

然而,RS触发器也存在一些常见问题。

1. 电路不稳定在RS触发器中,输入端R和S为低电平时,输出端往往会出现不稳定的情况。

这是由于输入变化可能导致反馈环路中的干扰,进而影响输出结果。

解决方法:通过添加稳态保持器来解决这一问题。

稳态保持器可在输入发生变化时稳定输出,提高电路的稳定性。

2. 存储违规在RS触发器中,输入端R和S同时为高电平时,会导致存储违规问题,即输出无法确定。

解决方法:通过添加使能信号,控制RS触发器的输入使能,避免输入违规情况的发生。

例如,使用带使能端的JK触发器。

二、JK触发器的问题及解决方法JK触发器是一种常用的触发器,具有更多的功能和灵活性。

然而,JK触发器也会出现一些常见问题。

1. JK翻转在JK触发器中,输入端J和K同时为高电平时,可能会导致翻转问题,即输出值出现错误的跳变。

解决方法:通过添加稳态保持器来解决JK翻转问题。

稳态保持器可稳定输出,避免由于输入同时为高电平引起的错误跳变。

2. 数据不稳定当触发器中的时钟信号在不稳定的状态下,输入数据可能会无法稳定传输到输出端。

解决方法:使用时钟同步电路来确保输入数据在时钟的控制下进行稳定传输。

时钟同步电路可以通过控制时钟信号的边沿来保证数据的稳定性。

三、D触发器的问题及解决方法D触发器是数字电路中最常用的触发器之一,具有简单、稳定的特点。

不过,D触发器也存在一些常见问题。

1. D触发器的输入重复如果在D触发器的输入端输入的是重复的数字信号,可能会导致输出端出现错误的跳变。

解决方法:通过添加去抖动电路来解决输入重复问题。

锁存器和触发器进入不可预测状态的分析与解决方法

一.锁存器

1.S-R锁存器

S-R锁存器进入亚稳态的可能情况:1.S,R同时由“1”变为“0”。

2.S,R任一端口输入脉冲很短(毛刺)。

区域2:

当S和R为“0”时,保持输出和上一状态相同,但由于S和R同时变化为“0”,各个器件传输延迟不同,那么保持的上一状态将是未知的。

区域 2 的作用就是人为地增加R的传输延迟,从而在.S,R同时由“1”变为“0”时,使输出为确定状态(Q为1 QN为0)。

也可以将区域2移到S输入端,这样在.S,R同时由“1”变为“0”时输出状态确定为Q为0 QN为1。

区域1:

区域1 可以一定程度上解决毛刺问题,区域1为D锁存器,当输入为脉冲宽度很小的毛刺时,D锁存器将其识别为没有变化,这样D锁存器输出就没有了此毛刺,后级的S-R锁存器就不会遇到此毛刺。

如果D锁存器将一个一定脉冲宽度的脉冲识别为变化,那么输出给S-R锁存器。

(其实没有什么严格规定,小于多少纳秒就是毛刺,所以我能想到的就是用其它器件来作前级“过滤”,至少可以消除一些宽度过小的毛刺。

)

关于区域1和2的作用会在以下的几个锁存器和触发器的波形仿真中具体解释。

S-R with enable 锁存器

S-R with enable锁存器进入亚稳态的可能情况:1 .S R C同时为“1”时,C由

“1”变为“0”,或者S ,R同

时由“1”变为“0”。

2. 毛刺

区域1:

区域1的作用同S_R锁存器,为“毛刺过滤”。

区域2:

两个区域2 都是由偶数个反相器组成,都是用来做延时。

上面的区域2的作用是:S R C同时为“1”,C由“1”变为“0”时,S通路较R通路变化滞后,这样在这种情况下,亚稳态被固定为Q为1 QN为0;(之所以这里用到四个反相器,而不是两个,是因为实验室两个也出现亚稳态。

也就是延时不足。

)

下面的区域2的作用是:C为“1”,S ,R同时由“1”变为“0”时,R通路较S通路变化滞后,这样在这种情况下,亚稳态被固定为Q为0 QN为1。

以下是Timing Simulation 时序图。

Figure 1

Figure 2 D 锁存器

D 锁存器进入亚稳态的可能情况 :1.C 由“1”变为“0”时(T setup ~T hold ),D

发生变化;

2. 毛刺。

区域1

区域1 的作用同上。

C 由“1”变为“0”时,

D 发生变化,这种情况造成的亚稳态,我现在无法解决。

二.触发器

1.D 触发器(正边沿和负边沿)

亚稳态出现的情况有:1. Clk 的上升沿(下降沿)T setup ~T hold 内,D 输入变化。

2.毛刺

2.具有使能输入的边沿D 触发器

.

亚稳态出现的情况有:1. Clk 的上升沿,且EN 为1,D 输入变化;

或 T setup ~T hold 内,EN 变化。

2.毛刺

扫描触发器与此相同。

CLRN D PRN Q DFF inst PRN CLRN D ENA Q DFFE inst4

3.主从时S_R 触发器

亚稳态出现的情况有:1.在时钟脉冲信号内,S ,R 同时由“1”变为“0” 或者时钟脉冲下降沿到来时,S ,R 保持为1。

(原理同

S-R Latch with enable )。

2. 毛刺。

4.主从式J-K 触发器

PRN CLRN

K J

Q JKFF

inst3

主从式J K 触发器内部构造相对于主从式SR触发器只是将主从式SR 触发器的 输入S (J )相与反馈QN ,R (K )相与Q 。

由于Q 和QN 在正常情况下是相反 的,因此就避免了主从式SR 触发器的第一种不稳定状态。

所以

亚稳态出现的情况有:1. 毛刺。

5.边沿J-K 触发器

亚稳态出现的情况有:1. 在时钟上升沿有效地J 或K (与J 或K 相与的反馈Q

或QN 为“1”)在T setup ~T hold 内发生变化;

2. 毛刺。

PRN CLRN S R Q SRFF inst5

触发器亚稳态的解决:

1.降低系统时钟;

2.使用更快的触发器;

3.改善时钟质量,使用边沿变化更快的时钟信号

4.引入同步机制,防止亚稳态的传播;

1.最可靠同步器设计

最可靠的同步器就是具有最大亚稳定性分辨时间的同步器。

但是,在数字系统的设计中,我们不仅很少因为系统的可靠性而奢侈地降低时钟频率,而且为了让系统具有更好的性能还常常要求提高时钟频率。

因此,通常需要能够在很短的时钟内可靠工作的同步器。

Tr=Tclk-Tcomb-Tsetup

速度越快的触发器建立时间就越短。

Tcomb(组合逻辑的传播延迟)最小值为0;

2.用两级D触发器构成同步器,时钟异步信号输入DFF1,这个信号可能

会违反触发器的建立时间和保持时间的规定。

一旦发生这种情况。

输出

信号就会进入亚稳态,而且这个状态停留一个任意长的时间。

然而,我们已经假设在时钟沿之后,亚稳定性保持的最长时间为Tr(称为亚稳定分辨时间)。

只要时钟周期比Tr与DFF2的建立时间之和要大,那么从下

一个时钟触发沿开始,DFF2的输出信号就是异步信号(DFF的输入信号)的同步拷贝,而且不会进入亚稳态。

于是就可以把DFF2的输出信号(时钟异步信号)分发到系统的其余部分!

通过两极触发器其实就是给亚稳态足够的脱离时间!。