用VHDL语言实现的交通灯

- 格式:doc

- 大小:356.50 KB

- 文档页数:20

基于VHDL的智能交通灯控制器1 设计任务及要求交通灯在指挥道路交叉部分的车辆,行人安全,有序,高效地通行,缓解城市交通拥堵状况起着重要作用,交通灯的出现大大降低了交汇路段的交通事故率,极大地提高了通行效率,是现代交通控制系统不可缺少的一部分。

本次将设计基于VHDL语言的交通灯控制系统,实现如下功能: 1. 本设计用总共8个LED灯分别指示南北和东西方向的红黄绿以及左转信号灯。

并规定在非紧急情况下各个方向车辆在不影响其他直行车道车辆正常行驶是情况下均能右转向,因此本设计未包含右转向信号。

2. 本设计具有状态实时显示功能,即各个状态的剩余时间将在对应的数码管上显示。

3. 复位功能:在紧急情况键未按下时复位键可以使系统从任意状态回到第一种状态。

4. 紧急状态限行功能:在紧急情况时可以按下紧急情况按钮,可使系统在任意情况,转向限制所有方向车辆通行,同时数码管显示“00”,发出警告音 5. 系统的六个状态为:东西方向绿灯,南北方向红灯,持续30s;东西方向黄灯,南北方向红灯,持续5s;东西方向绿灯,南北方向左转,持续10;东西方向红灯,南北方向绿灯,持续30s;东西方向红灯,南北方向黄灯,持续5s;东西方向左转,南北方向绿灯,持续10s;6.要求在无人工干预条件下各个状态能自动转换,系统正常运行。

2设计原理及总体框图本交通灯设计总共用8个数码管分别指示东西和南北方向的红灯,黄灯,绿灯以及左转指示灯。

共有六种状态,如下表所示:状态 1 2 3 4 5 6 南北方向东西方向LED指示LED状态绿灯黄灯绿灯红灯红灯左转计数器初值30 5 10 35 5 10 LED状态红灯红灯左转绿灯黄灯绿灯计数器初值35 5 10 305 10 LED代码00101000 01001000 00100001 10000010 10000100 00010010 设计的总体框图为:时钟输入交通灯控制核心模块东西方向数码管时间显示南北方向数码管时间显示LED显示交通灯控制模块在时钟的控制下,实现各个状态的自动转换,并且负责输出LED的控制信号和,数码管倒计时的BCD码输入信号。

一:十字路口交通灯实现程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY traffic ISPORT ( clk,urgency:IN STD_LOGIC;led:BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0);East_West,South_North:BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0));END traffic;ARCHITECTURE A OF traffic ISBEGINPROCESS(clk)BEGINIF urgency='0' THEN --紧急情况两方向都禁止led<="10000001";--全红灯East_West<="00000000";South_North<="00000000";ELSIF clk'event AND clk='1' THENIF East_West>"01000110"OR South_North>"01000110" THENEast_West<="01000101";--45sSouth_North<="01000000";--40Sled<="10000100";--东西红灯南北绿灯(红黄绿--绿黄红)ELSIF East_West="00000110"AND South_North="00000001" THENEast_West<="00000101";--5SSouth_North<="00000101";--5Sled<="10000010";--东西红灯南北黄灯ELSIF East_West="00000001"AND South_North="00000001"andled="10000010" THEN--East_West<="01000000";--40SSouth_North<="01000101";--45Sled<="00100001";--东西绿灯南北红灯ELSIF East_West="00000001"AND South_North="00000110" THENEast_West<="00000101";South_North<="00000101";led<="01000001";--东西黄灯南北红灯ELSIF East_West<="00000001"AND South_North="00000001"AND LED="01000001" THEN East_West<="01000101";South_North<="01000000";led<="10000100";--东西红灯南北绿灯ELSIF East_West(3 DOWNTO 0)=0 THENEast_West<=East_West-7;--计数超出范围则减7South_North<=South_North-1;ELSIF South_North(3 DOWNTO 0)=0 THENEast_West<=East_West-1;South_North<=South_North-7;ELSEEast_West<=East_West-1;--正常情况下东西南北各计数值减1(上升沿触发)South_North<=South_North-1;END IF;END IF;END PROCESS;END A;二:模式选择与引脚定义如下:1:选择模式52:引脚定义如下:三:硬件说明:数码管2和数码管1作为东西方向灯的时间显示,数码管4和数码管3作为南北方向灯的时间显示。

library ieee; -----分频电路use ieee.std_logic_1164.all;entity fen isport(clk:in std_logic;clk1:out std_logic); ---实体端口声明end fen;architecture fen_arc of fen is ---结构体描述开始beginprocess(clk) --进程开始variable cnt:integer range 0 to 99;beginif clk'event and clk='1' then ---高电平到if cnt=99 thencnt:=0; ---0开始计数clk1<='1'; --输出高电平elsecnt:=cnt+1; ---加计数clk1<='0'; --输出低电平end if;end if;end process; ---进程描述结束end fen_arc; ---结构体描述结束--------------------------------------------------A路控制library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Alu isport(clk:in std_logic;ar,ag,al,ay:out std_logic; ----红、绿、黄、左转timas,timag:out std_logic_vector(3 downto 0)); ----十位、个位计数end Alu;architecture alu_arc of Alu istype rgly is(red,green,left,yellow); ---灯亮顺序为红、绿、左转、黄beginprocess(clk)variable a:std_logic; ----变量声明variable ts,tg:std_logic_vector(3 downto 0);variable state:rgly;beginif clk'event and clk='1' then ---高电平case state iswhen green=>if a='0' then --绿灯状态ts:="0010"; --十位计2tg:="0100"; --个位计4a:='1';ag<='0';ar<='1';elseif not(ts="0000" and tg="0001") then --若计数值不为1if tg="0000" then --若个位为1tg:="1001"; --个位置9ts:=ts-1; --十位自减1 elsetg:=tg-1; --个位自减1 end if;elsets:="0000";tg:="0000";a:='0';state:=left; ---转为左转灯状态end if;end if;when left=>if a='0' then ---------------左转灯ts:="0000"; -----------十位置0tg:="1001"; --------------个位置9a:='1';aL<='0';ag<='1';elseif not (ts="0000" and tg="0001")thenif tg="0000" thentg:="1001";ts:=ts-1;elsetg:=tg-1;end if;elsets:="0000";tg:="0000";a:='0';state:=yellow;----转为黄灯状态end if;end if;when yellow=>if a='0' then -----黄灯状态ts:="0000"; ---十位置0tg:="0100"; ----个位置9a:='1';ay<='0';aL<='1';elseif not(ts="0000" and tg="0001") thenif tg="0000" thentg:="1001";ts:=ts-1;elsetg:=tg-1;end if;elsets:="0000";tg:="0000";a:='0';state:=red;end if;end if;when red=>if a='0' then --------红灯状态ts:="0011"; ----十位置3tg:="1001"; ---个位置9a:='1';ar<='0';ay<='1';elseif not(ts="0000" and tg="0001") thenif tg="0000" thentg:="1001";ts:=ts-1 ;elsetg:=tg-1;end if;elsets:="0000";tg:="0000";a:='0';state:=green;end if;end if;end case;timas<=ts;timag<=tg;end if;end process;end alu_arc;-----------------------------------------------------B路灯控制程序。

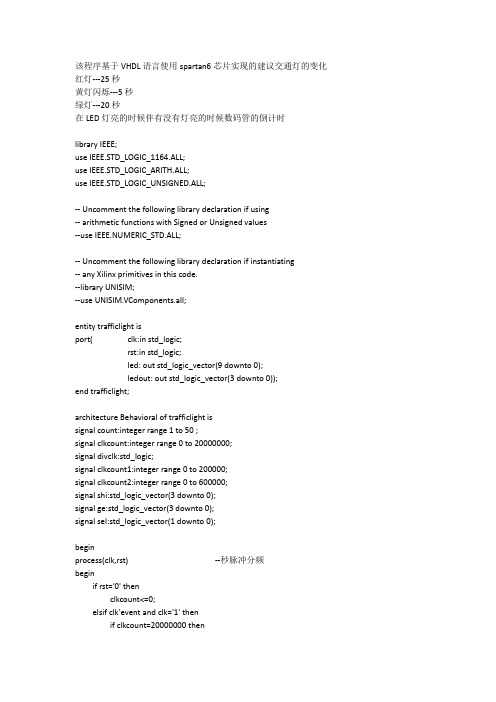

该程序基于VHDL语言使用spartan6芯片实现的建议交通灯的变化红灯---25秒黄灯闪烁---5秒绿灯---20秒在LED灯亮的时候伴有没有灯亮的时候数码管的倒计时library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entitytrafficlight isport( clk:instd_logic;rst:instd_logic;led: out std_logic_vector(9 downto 0);ledout: out std_logic_vector(3 downto 0)); endtrafficlight;architecture Behavioral of trafficlight issignalcount:integer range 1 to 50 ;signalclkcount:integer range 0 to 20000000;signaldivclk:std_logic;signal clkcount1:integer range 0 to 200000;signal clkcount2:integer range 0 to 600000;signalshi:std_logic_vector(3 downto 0);signalge:std_logic_vector(3 downto 0);signalsel:std_logic_vector(1 downto 0);beginprocess(clk,rst) --秒脉冲分频beginifrst='0' thenclkcount<=0;elsifclk'event and clk='1' thenifclkcount=20000000 thenclkcount<=0;divclk<=not divclk;elseclkcount<=clkcount+1;end if;end if;end process;process(clk,clkcount2,sel,rst) --数码管扫描分频beginifrst='0' thenclkcount2<=0;elsifclk'event and clk='1' thenif clkcount2=600000 thenclkcount2<=0;else clkcount2<=clkcount2+1;end if;end if;if (clkcount2<300000) thensel<="01";elsesel<="10";end if;end process;process(divclk,rst)beginifrst='0' thencount<=1;elsifdivclk'event and divclk='1' thenif count=50 thencount<=1;elsecount<=count+1;end if;end if;end process;process(divclk,rst)beginif (rst='0' ) thenge<="0101";shi<="0010";elsif(divclk'event and divclk='1')thenif(count<=25)thenif(ge="0001"and shi="0000")thenge<="0101";shi<="0000";elsif(ge="0000")thenshi<=shi-1;ge<="1001";elsege<=ge-1;end if;elsif(count<=30)thenif(ge="0001"and shi="0000")thenge<="0000";shi<="0010";elsege<=ge-1;end if;elsif(count<=50)thenif(ge="0001"and shi="0000")thenge<="0101";shi<="0010";elsif(ge="0000")thenshi<=shi-1;ge<="1001";elsege<=ge-1;end if;end if;end if;end process;process(count,divclk,rst)beginifrst='0' thenledout<="0000";elsifdivclk'event and divclk='1' thenif(count=50)thenledout<="0001";elsif(count<=24)thenledout<="0001";elsif(count<=29)thencase count iswhen 25=>ledout<="0100";when 26=>ledout<="0000";when 27=>ledout<="0100";when 28=>ledout<="0000";when 29=>ledout<="0100";when others=>ledout<="0100";end case;elseledout<="0010";end if;end if;end process;process(ge,shi,sel)beginif(sel="01")thencasege iswhen"0000"=> led <="010*******";when"0001"=> led <="010*******";when"0010"=> led <="010*******";when"0011"=> led <="010*******";when"0100"=> led <="010*******";when"0101"=> led <="010*******";when"0110"=> led <="010*******";when"0111"=> led <="010*******";when"1000"=> led <="010*******";when"1001"=> led <="010*******";when others=> led <="010*******";end case;elsecaseshi iswhen"0000"=> led <="1000111111";when"0001"=> led <="1000000110";when"0010"=> led <="1001011011";when others => led <="1001111111";end case;end if;end process;end Behavioral;。

目录序言 (3)第1章任务和要求 (4)1.1 设计任务 (4)1.2设计要求 (4)第2章功能分析 (6)2.1交通灯控制系统总体框架图 (6)2.2模块功能分析 (6)第3章设计过程 (7)3.1 分频模块的设计及仿真图 (7)3.2 显示模块的设计及仿真图 (7)3.3 数码管显示模块设计及仿真图 (8)3.4 译码驱动模块的设计及仿真图 (8)3.5顶层文件设计及仿真图 (9)3.6交通灯顶层原理图 (9)第4章外部电路结构图及引脚分配 (11)4.1电路主要结构 (11)4.2下载引脚分配 (12)第五章分析与小结5.1测试及结果分析 (13)5.2实验小结 (13)参考文献 (14)附录 (15)具有五种信号灯和倒计时显示的交通灯控制器序言随着社会经济的发展,城市交通问题越来越引起人们的关注。

人、车、路三者关系的协调,已成为交通管理部门需要解决的重要问题之一。

城市交通控制系统是用于城市交通数据监测、交通信号灯控制与交通疏导的计算机综合管理系统,它是现代城市交通监控指挥系统中最重要的组成部分。

、上海、南京等出现了交通超负荷运行的情况,因此,自80年代后期,这些城市纷纷修建城市高速道路,在高速道路建设完成的初期,它们也曾有效地改善了交通状况。

然而,随着交通量的快速增长和缺乏对高速道路的系统研究和控制,高速道路没有充分发挥出预期的作用。

而城市高速道路在构造上的特点,也决定了城市高速道路的交通状况必然受高速道路与普通道路耦合处交通状况的制约。

所以,如何采用合适的控制方法,最大限度利用好耗费巨资修建的城市高速道路,缓解主干道与匝道、城区同周边地区的交通拥堵状况,越来越成为交通运输管理和城市规划部门亟待解决的主要问题。

交通信号灯的出现,使交通得以有效管制,对于疏导交通流量、提高道路通行能力,减少交通事故有明显效果。

随着中国加入WTO,我们不但要在经济、文化、科技等各方面与国际接轨,在交通控制方面也应与国际接轨。

交通灯控制器的设计智能交通灯控制器的源程序如下:library ieee;use ieee.std_logic_1164.all;entity traffic_control isport( clk: in std_logic;sense0,sense1: in std_logic; --分别为东西路和南北路车辆指示器counter: out integer range 0 to 44;r0,y0,g0: out std_logic; --r0,y0,g0为南北路的红、黄、绿灯r1,y1,g1:out std_logic); --r1,y1,g1为东西路的红、黄、绿灯end;architecture art of traffic_control2 issignal state:std_logic_vector(1 downto 0);signal cnt:integer range 0 to 44;beginprocess(clk)variable nclr,en:bit; --nclr为倒计时计数器清零端,en为计数器使能端beginif clk'event and clk='1' thenif nclr='0' thencnt<=0; --同步清零elsif en='0'thencnt<=cnt; --计数器停止计数elsecnt<=cnt+1; --计数器值增加end if;case state iswhen "00"=>r0<='1';y0<='0';g0<='0';r1<='0';y1<='0';g1<='1';if(sense0 and sense1)='1' then --东西道和南北道都有车if cnt=44 thenstate<="01";nclr:='0';en:='0';elsestate<="00";nclr:='1';en:='1';end if;elsif(sense0 and (not sense1))='1' then --东西道有车,南北道无车state<="01";nclr:='0';en:='0';elsestate<="00";nclr:='1';en:='1';end if;when "01"=>r0<='1';y0<='0';g0<='0';r1<='0';y1<='1';g1<='0';if cnt=5 thenstate<="10";nclr:='0';en:='0';elsestate<="01";nclr:='1';en:='1';end if;when "10"=>r0<='0';y0<='0';g0<='1';r1<='1';y1<='0';g1<='0';if(sense0 and sense1)='1' then --东西道和南北道都有车if cnt=29 thenstate<="11";nclr:='0';en:='0';elsestate<="10";nclr:='1';en:='1';end if;elsif sense0 ='0' then --东西道有车,南北道无车state<="11";nclr:='0';en:='0';elsestate<="10";nclr:='1';en:='1';end if;when "11"=>r0<='1';y0<='1';g0<='0';r1<='1';y1<='0';g1<='0';if cnt=5 thenstate<="00";nclr:='0';en:='0';elsestate<="11";nclr:='1';en:='1';end if;end case;end if;end process;counter<=cnt;end art;。

基于VHDL语言的交通灯控制器设计与实现1引言在交通发达的当代,交通灯控制器无疑是最实用的的工具。

为了使交通行驶有一个很高的效率,人工指挥交通已经显得效率不高,所以一个高智能的交通灯控制器是十分的必要的。

交通灯的控制方式,是根据时间来改变状态,产生不同的控制信号以控制红、绿、黄三盏灯的开关,达到控制交通的目的。

目前VHDL语言已成为EDA领域首选的硬件设计语言,越来越多的数字系统设计使用VHDL语言来完成。

原因是通过VHDL描述的硬件系统“软核”便于存档,程序模块的移植和ASC设计源程序的交付更为方便。

因此,他在IP核的应用等方面担任着不可或缺的角色。

在某扩频通信系统中,我们使用VHDL语言设计了交通灯控制器,并经过了在FPGA芯片上的验证实验。

2课题背景及相关技术2.1 Max+plusII简介Max+plusII(或写成Maxplus2或MP2) 是Altera公司推出的的第三代PLD开发系统(Altera第四代PLD开发系统被称为:Quartus,主要用于设计6万-100万门的大规模CPLD/FPGA)。

使用MaX+PLUSII的设计者不需精通器件内部的复杂结构。

设计者可以用自己熟悉的设计工具(如原理图输入或硬件描述语言)建立设计,MaX+PLUSII把这些设计转自动换成最终所需的格式。

其设计速度非常快。

对于一般几千门的电路设计,使用MaX+PLUSII,从设计输入到器件编程完毕,用户拿到设计好的逻辑电路,大约只需几小时。

设计处理一般在数分钟内内完成。

特别是在原理图输入等方面,Maxplus2被公认为是最易使用,人机界面最友善的PLD开发软件,特别适合初学者使用。

通常可将Maxplus2设计流程归纳为以下7个步骤:(1)使用文本编辑器输入设计源文件。

在传统设计中,设计人员是应用传统的原理图输入方法来开始设计的。

自90年代初,Verilog、VHDL、AHDL等硬件描述语言的输入方法在大规模设计中得到了广泛应用。

基于VHDL的交通灯设计摘要随着社会上特别是城市中机动车辆保有量的不断增加,在现代城市的日常运行控制中,车辆的交通控制越来越重要,在十字交叉路口,越来越多的使用红绿灯进行交通指挥和管理。

本文以VHDL硬件描述语言为设计手段,完成了交通信号灯控制电路的设计,其中交通信号灯控制电路的开发目的是设计一个适用于主、支干道十字交叉路口的红黄绿交通灯的控制系统,通过合理设计系统功能,使红黄绿灯的转换有一个准确的时间间隔和转换顺序。

所设计的交通信号灯控制电路经过在QuartusⅡ 6.0软件下进行模拟仿真,观察其波形,证明所设计的交通信号灯控制电路完全可以实现预定的功能,并有一定的实用性。

关键词:FPGA; VHDL; QuartusⅡ; 交通灯一、设计思路本设计主要是利用状态机控制,交通灯的工作分成5个状态,如下:St0:支干道亮红灯,主干道亮绿灯,数码管不显示。

St1:主干道亮绿灯45秒,数码管显示45秒倒计时;支干道亮红灯,数码管显示从49秒倒计时到05秒。

St2::主干道亮黄灯5秒,数码管显示5秒倒计时;支干道亮红灯,数码管显示从04秒倒计时到00秒。

St3:支干道亮绿灯25秒,数码管显示25秒倒计时;主干道亮红灯,数码管显示从29秒倒计时到05秒。

St4:支干道亮黄灯5秒,数码管显示5秒倒计时;主干道亮红灯,数码管显示从04秒倒计时到00秒。

把交通灯的工作分成五个状态,则写程序的时候思路就比较清晰,只要在相应的状态里完成相应的工作,控制好黄绿红灯和数码管的倒计时显示,而且把握好五个状态转换的条件即可。

实现起来也方便。

二、设计分析根据设计思路可以把整体设计分为三个模块:1、分频模块:把实验板上的50MHz的频率分成1Hz信号(用于倒计时计数的时钟信号)、1kHz信号(用于数码管扫描显示的片选时钟信号)和2hz(用于黄灯的闪烁);2、交通灯控制以及倒计时(五个状态的控制)模块;3、数码管译码扫描显示模块。

目录序言 (3)第1章任务和要求 (4)1.1 设计任务 (4)1.2设计要求 (4)第2章功能分析 (6)2.1交通灯控制系统总体框架图 (6)2.2模块功能分析 (6)第3章设计过程 (7)3.1 分频模块的设计及仿真图 (7)3.2 显示模块的设计及仿真图 (7)3.3 数码管显示模块设计及仿真图 (8)3.4 译码驱动模块的设计及仿真图 (8)3.5顶层文件设计及仿真图 (9)3.6交通灯顶层原理图 (9)第4章外部电路结构图及引脚分配 (11)4.1电路主要结构 (11)4.2下载引脚分配 (12)第五章分析与小结5.1测试及结果分析 (13)5.2实验小结 (13)参考文献 (14)附录 (15)具有五种信号灯和倒计时显示的交通灯控制器序言随着社会经济的发展,城市交通问题越来越引起人们的关注。

人、车、路三者关系的协调,已成为交通管理部门需要解决的重要问题之一。

城市交通控制系统是用于城市交通数据监测、交通信号灯控制与交通疏导的计算机综合管理系统,它是现代城市交通监控指挥系统中最重要的组成部分。

、上海、南京等出现了交通超负荷运行的情况,因此,自80年代后期,这些城市纷纷修建城市高速道路,在高速道路建设完成的初期,它们也曾有效地改善了交通状况。

然而,随着交通量的快速增长和缺乏对高速道路的系统研究和控制,高速道路没有充分发挥出预期的作用。

而城市高速道路在构造上的特点,也决定了城市高速道路的交通状况必然受高速道路与普通道路耦合处交通状况的制约。

所以,如何采用合适的控制方法,最大限度利用好耗费巨资修建的城市高速道路,缓解主干道与匝道、城区同周边地区的交通拥堵状况,越来越成为交通运输管理和城市规划部门亟待解决的主要问题。

交通信号灯的出现,使交通得以有效管制,对于疏导交通流量、提高道路通行能力,减少交通事故有明显效果。

随着中国加入WTO,我们不但要在经济、文化、科技等各方面与国际接轨,在交通控制方面也应与国际接轨。

俗话说“要想富,先修路”,但路修好了如果在交通控制方面做不好道路还是无法保障畅通安全。

作为交通控制的重要组成部份的交通信号灯也应适合社会实际情况。

因此,本人选择制作十字路口交通灯。

运用VHDL语言编写一个交通灯控制器模块,该模块由四部分组成,分别是分频模块clk_10,灯模块js,数码显示模块sm和译码驱动模块dec47。

交通灯控制器用于自动控制十字路口交通灯和计时器,指挥各种车辆和行人安全通行。

摘要:本设计中选用目前应用较广泛的VHDL硬件电路描述语言,实现对路口交通灯系统的控制器的硬件电路描述,在Altera公司的EDA软件平台MAX+PLUSⅡ环境下通过了编译、仿真,并下载到CPLD器件上进行编程制作,实现了交通灯系统的控制过程。

关键词:EDA;VHDL;控制器;CPLDAbstract: And select and use Description Language applying broader VHDL hardware circuit at present in capital being designed, the hardware circuit coming true to systematic controller of crossing traffic light describes that, have passed compiling , have simulated under EDA of Altera company software platform MAX + PLUS II environment, download the control procedure having made , realizing traffic light systematically to the programming being in progress on CPLD component. Keywords: EDA; VHDL; Controller; CPLD第1章任务和要求1.1 设计任务设计一个十字路口交通控制器,方向和方向分别设置左拐(L),绿(G),黄(Y),和红(R),人行道(p)五盏灯,以及倒计时显示器,用以指挥车辆和行人有序的通行。

左拐灯(L)亮表示左转车辆可以通行;绿灯(G)亮表示直行车辆可以通行;黄灯(Y)亮表示左转或直行车辆即将禁行;红(R)灯亮表示左转和直行车辆禁行,人行道的绿灯亮表示人可以通行,红灯表示人行道不可以通行;倒计时显示器用来显示允许通行或禁止通行的时间。

1.2设计要求1.在十字路口A和B两个方向各设一组左拐,绿灯,黄灯,红灯,人行道红绿灯。

显示顺序:绿灯——黄灯——红灯(左拐灯以及人行道绿灯)。

2.在A和B两个方向各设一组倒计时显示器。

A、B方向绿灯,黄灯,红灯和左拐灯显示时间分别是39s,6s,45s,和15s。

3.交通灯的显示状况:39s 6s 左拐15s 人绿30sA 绿灯黄灯红灯45s左拐15s人绿30s 39s 6sB 红灯绿灯黄灯45s除人行道绿灯亮之外,人行道红灯亮。

4.设有一个特殊情况按钮con,当为高电平的时候可以让人行道的交通灯的红灯都亮,为低电平的时候可以恢复正常。

5.设有停止按钮rst,当为高电平的时候可以让所有的灯以及数码管都停止,当为低电平的时候恢复正常。

第2章 功能分析2.1控制系统总体框架图con A 、B 道灯输出(12个灯)clk 数码管Rst图2—1交通灯控制系统总体框架图2.2各模块功能分析根据设计要求和系统所具有的功能,交通灯控制分为四个部分:分频电路:用555电路也可以产生1HZ 的脉冲,但是由于频率太低不稳定,所有用555产生10HZ 的脉冲,而我们需要的是1HZ 的脉冲,所有我们在软件内部加了一个10分频的电路。

灯显示电路:按照交通灯的亮灯时间和亮灯顺序,在进行计数的同时控制灯的亮和分频电路灯控制电路数码显示电路译码驱动电路译码驱动电路译码驱动电路 译码驱动电路灭。

数码显示电路:这是数码管显示控制电路,利用计数控制数码管的显示,数码管是以BCD的来显示的,而且显示是以减计数的形式来显示的。

译码显示电路:这是个译码电路,与外部的数码管相连接。

第3章设计过程3.1分频模块clk_10的设计控制模块的输入是由555产生的10HZ脉冲,输出是经过分频之后的1HZ 脉冲,分频模块的仿真如下:图3-1 交通灯分频模块波形仿真图3.2 灯显示模块js的设计控制12个灯的亮和灭。

灯显示模块的仿真如下:图3-2交通灯计时模块波形仿真图3.3数码显示模块sm的设计控制数码管的显示。

该模块的仿真如下:图3-3交通灯译码驱动模块波形仿真图3.4 译码驱动模块dec47的设计显示模块用来显示倒计时时间和系统的工作状态。

其输出用来驱动六位数码管,其中四位用于显示倒计时时间,两位显示工作状态,采用动态扫描显示。

该模块的仿真如下:图3-4交通灯显示模块波形仿真图3.5 顶层文件设计由分频模块clk_10,灯显示模块js,数码显示模块sm和译码驱动模块dec47四部分组成,其仿真如下:图3-6交通灯顶层文件波形仿真图3.6交通灯顶原理图图3-7交通灯顶层原理图第4章 电路结构图及引脚分配4.1电路主要结构 VCC12个灯图4-1交通灯控制器外部电路主要结构说明:电路中的电阻都为1K ,555的外部电路有两个电阻,分别是75K 和33K,电容是1uF 和10nF 。

灯和数码管都用底座插,开关也用底座,开关至1为闭合(接地),开关至0为打开(接高电平)。

三五产生一个10KHz 的脉冲信号。

数码管 数码管 数码管 数码管4.2下载引脚分配表4-2下载引脚分配第五章分析与小结5.1测试及结果分析1.灯显示测试当电路连接完毕后,将写好的测试程序下载到芯片内,连接好各灯通电检测。

检测各个工作方式下的灯亮情况。

2.数码管的测试将串口的和电路板上的接口连接,将写好的测试程下载到芯片内,用万用表监测下,再测试。

3.整体电路测试系统上电,下载好程序即可开始测试,观测一个周期灯的显示状态是否正常,同时观察倒计的计数是否正常。

5.2 实验小结首先感谢宋伟老师和翟丽芳老师为期两个星期对我们的辅导、帮助与支持。

本次课程设计软件都是我们自己编的,经过这个过程之后我觉得我学了不少的东西,硬件易出问题,尤其是开关的连接。

连线复杂,问题难以检查。

软件应根据具体硬件设计,如数码管动态扫描电路:共阴极和共阳极其程序有所区别。

此外,设计和调试的过程中,也发现了一些问题,譬如灯和数码管不同步,还有就是没有做过市场调查,设置不是很合理,下次做的时候应先做市场调查。

这需要在实践中进一步完善。

分频程序在实际应用时也须根据具体情况设计。

参考文献[1]邹彦,庄严,邹宁,王宇鸿.EDA技术与数字系统设计[M].北京:电子工业出版社,2007.[2]谭会生.VHdl硬件描述语言与数字逻辑电路设计[M].长沙:湖南大学出版社,2004.[3]雷伏生.电路设计.北京:清华大学出版社[M],2006.[4]杨晓慧.EDA技术与数字电路设计.北京:国防工业出版社[M],2004.[5]许丽娅.VHDL语言设计.泉州:北京理工大学出版社[M].2005.附录源程序清单1.分频模块源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity clk_10 isport( clk : in std_logic;rst:in std_logic;clk_div10 : out std_logic);end clk_10;architecture one of clk_10 issignal clk_temp : std_logic;beginprocess(clk,rst)variable counter : std_logic_vector(2 downto 0); constant md : std_logic_vector(2 downto 0) := "101"; beginif(rst='0') thenif(clk'event and clk='1') thenif(counter = md)thencounter := (others =>'0');clk_temp <= not clk_temp;end if;counter := counter + 1 ;end if;else clk_temp<='0';end if;end process;clk_div10 <= clk_temp;end one;2.灯显示模块源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity js isport (clk:in std_logic;con:in std_logic;al,ag,ay,ar,ap:out std_logic;bl,bg,by,br,bp:out std_logic;apr,bpr:out std_logic); end entity js;architecture one of js issignal b:std_logic_vector(6 downto 0); signal apg,bpg:std_logic;beginprocess(clk,con)variable co,bo:std_logic:='0';beginif(con='0') thenif(clk'event and clk='1') then b<=b+1;if(b<=14) then al<='0';ag<='1';ay<='0';ar<='0';apg<='0';bl<='1';bg<='0';by<='0';br<='1';bpg<='0';elsif(b<=38 and b>14) then al<='0';ag<='1';ay<='0';ar<='0';apg<='0';bl<='0';bg<='0';by<='0';br<='1';bpg<='1';elsif(b<=44 and b>38) then co:=not co; al<='0';ag<='0';ay<=co;ar<='0';apg<='0';bl<='0';bg<='0';by<='0';br<='1';bpg<='1';elsif(b<=59 and b>44) then al<='1';ag<='0';ay<='0';ar<='1';apg<='0';bl<='0';bg<='1';by<='0';br<='0';bpg<='0';elsif(b<=83 and b>59) then al<='0';ag<='0';ay<='0';ar<='1';apg<='1';bl<='0';bg<='1';by<='0';br<='0';bpg<='0';elsif(b<=89 and b>83) then bo:=not bo;al<='0';ag<='0';ay<='0';ar<='1';apg<='1';bl<='0';bg<='0';by<=bo;br<='0';bpg<='0';elsif(b>88) then b<="0000001";al<='0';ag<='1';ay<='0';ar<='0';apg<='0';bl<='1';bg<='0';by<='0';br<='1';bpg<= '0';end if;end if;else al<='0';ag<='0';ay<='0';ar<='1';apg<='0';bl<='0';bg<='0';by<='0';br<='1';bpg<='0';end if;apr<=not apg;bpr<=not bpg;end process ;ap<=apg;bp<=bpg;end architecture;3、数码显示模块源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sm isport (clk:in std_logic;a1:out std_logic_vector(3 downto 0);a2:out std_logic_vector(3 downto 0);b1:out std_logic_vector(3 downto 0);b2:out std_logic_vector(3 downto 0));end entity sm;architecture one of sm issignal t1,t2,p1,p2:std_logic_vector(3 downto 0);signal j:std_logic_vector(6 downto 0):="0000000";beginprocess(clk)beginif(clk'event and clk='1') thenif (j=0) then t1<="0011";t2<="1000";p1<="0100";p2<="0100";end if;if(j>0 and j<39) thenif(t2>"0000") then t1<=t1;t2<=t2-1;elsif(t2="0000") then t1<=t1-1;t2<="1001";end if;end if;if(j>0 and j<45) thenif(p2>"0000") then p1<=p1;p2<=p2-1;elsif(p2="0000") then p1<=p1-1;p2<="1001";end if;end if;if (j=39) then t1<="1011";t2<="1011";end if;if (j=45) then t1<="0100";t2<="0100";p1<="0011";p2<="1000";end if;if(j>45 and j<85) thenif(p2>"0000") then p1<=p1;p2<=p2-1;elsif(p2="0000") then p1<=p1-1;p2<="1001";end if;end if;if(j>45 and j<91) thenif(t2>"0000") then t1<=t1;t2<=t2-1;elsif(t2="0000") then t1<=t1-1;t2<="1001";end if;end if;if (j=84) then p1<="1011";p2<="1011";end if;j<=j+1;if (j=89) then j<="0000000";end if;end if;end process;a1<=t1;a2<=t2;b1<=p1;b2<=p2;end architecture;4.译码驱动模块源程序library ieee;use ieee.std_logic_1164.all;entity dec47 isport (a:in std_logic_vector(3 downto 0);y1,y2,y3,y4,y5,y6,y7:out std_logic);end dec47;architecture one of dec47 isbeginprocess(a)begincase a iswhen "0000" => y1<='0';y2<='0';y3<='0';y4<='0';y5<='0';y6<='0';y7<='1'; when "0001" => y1<='1';y2<='1';y3<='1';y4<='1';y5<='0';y6<='0';y7<='1'; when "0010" => y1<='0';y2<='0';y3<='1';y4<='0';y5<='0';y6<='1';y7<='0'; when "0011" => y1<='0';y2<='0';y3<='0';y4<='0';y5<='1';y6<='1';y7<='0'; when "0100" => y1<='1';y2<='0';y3<='0';y4<='1';y5<='1';y6<='0';y7<='0'; when "0101" => y1<='0';y2<='1';y3<='0';y4<='0';y5<='1';y6<='0';y7<='0'; when "0110" => y1<='0';y2<='1';y3<='0';y4<='0';y5<='0';y6<='0';y7<='0'; when "0111" => y1<='0';y2<='0';y3<='0';y4<='1';y5<='1';y6<='1';y7<='1'; when "1000" => y1<='0';y2<='0';y3<='0';y4<='0';y5<='0';y6<='0';y7<='0'; when "1001" => y1<='0';y2<='0';y3<='0';y4<='1';y5<='1';y6<='0';y7<='0'; when "1011" => y1<='1';y2<='1';y3<='1';y4<='1';y5<='1';y6<='1';y7<='1'; when others => y1<='Z';y2<='Z';y3<='Z';y4<='Z';y5<='Z';y6<='Z';y7<='Z'; end case;end process;end one;。