第六章原理图输入方法

- 格式:ppt

- 大小:3.82 MB

- 文档页数:80

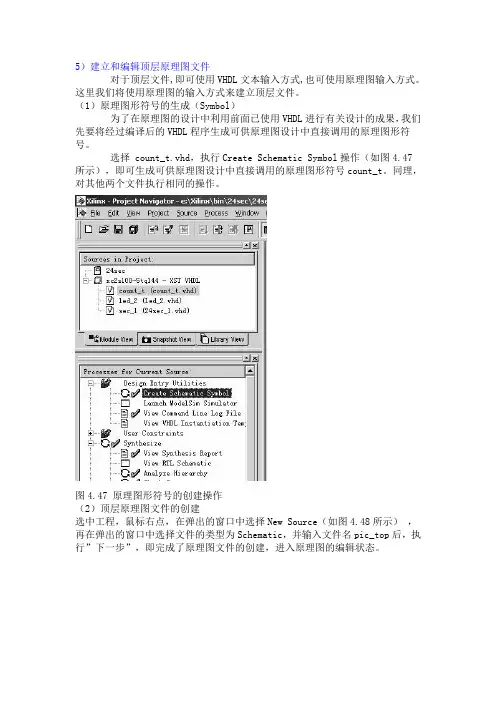

5)建立和编辑顶层原理图文件对于顶层文件,即可使用VHDL文本输入方式,也可使用原理图输入方式。

这里我们将使用原理图的输入方式来建立顶层文件。

(1)原理图形符号的生成(Symbol)为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。

选择 count_t.vhd,执行Create Schematic Symbol操作(如图4.47所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。

同理,对其他两个文件执行相同的操作。

图4.47 原理图形符号的创建操作(2)顶层原理图文件的创建选中工程,鼠标右点,在弹出的窗口中选择New Source(如图4.48所示),再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。

图4.48 原理图的创建操作(3)原理图的编辑① 放置元件(Symbols):在Symbols 的e:/xilinx/bin/24sec中选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如图4.49所示。

若位置不合适,可进行移动调整。

图4.49 在原理图中放置元件的操作② 元件间的连线:点,进行连线操作。

③ 放置I/O端口并编辑端口名:点,放置I/O端口。

选中端口,点右键,在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。

或者双击端口,在弹出的对话框中输入系统设定的端口名。

④ 原理图的保存:原理图编辑好后(如图4.50所示),应执行存盘操作,将原理图进行保存。

图4.50 编辑好的顶层原理图⑤ 原理图错误的检查:为了检查原理图是否有错,可执行原理图的检错操作。

若有错,则改正,直到完全正确为止。

⑥ 原理图的逻辑综合:若原理图经过检查没有错误,可进行逻辑综合。

实验二:原理图输入设计方法与混合输入设计方法一、实验目的1、熟悉QuartusII 软件的使用,学习QuartusⅡ的原理图输入设计方法与混合输入设计方法;2、通过1位全加器的设计与仿真过程进行训练。

2、实验内容及步骤1、原理图输入设计A、先设计半加器:按照实验一的步骤新建工程"file"\new project wizard",设置保存路径,以及顶层设计名“EXAND”\OK;新建原理图编辑文件,“file”\"new"\"block diagram/schematic file"\"OK".。

在原理图编辑窗口中绘制半加器原理图(点“"sympol tool ,找到相应元件添加,连线,更改相应输入与输出端口名,保存为"exand1"),绘制的原理图如图示,截图保存("file"\"export");要使在全加器的顶层设计中能够调用半加器,必须将半加器设置成可调用的元件,即编译半加器原理图,直至"0 error",后,执行"file"\"create/update"\"create sympol files for current file",即可在工程项目保存目录下生成可条用的原理图,调用时在原理图编辑窗口的空白处双击鼠标左键调用此前创建的半加器元件符号,或者点击Symbol Tool按钮,在弹出的对话框“project”文件中进行选择。

生成的半加器元件符号如图所示:半加器元件符号B 、调用半加器,设计全加器原理图文件:与设计半加器原理图文件相似,调用半加器元件符号,绘制的全加器原理图如图示。

保存名为“ EXAND ” .2.编译原理图文件,并进行仿真实验:执行"processing"\"start compilation",若出现错误,则根据message的提示修改程序,继续编译,直至"inf0:QuartueII Full compilation was successful .0 error".编译完成后,仿真。

本章在第2章的基础上,对QuartusⅡ的原理图输入法作进一步的讨论。

本章主要讨论原理图输入法中的MAX+plusⅡ老式宏函数的应用、LPM函数的应用和原理图输入法的层次化设计。

3畅1 原理图输入法中MAX+plusⅡ老式宏函数的应用 在QuartusⅡ原理图输入法中,可供使用的元件库除了基本逻辑元件库以外,还有MAX+plusⅡ库和LPM函数元件库,如图3-1所示。

MAX+plusⅡ库中收有MAX+plusⅡ老式宏函数包括加法器、编码器、译码器、计数器和移位寄存器等74系列器件,用户可自由地调用。

QuartusⅡ编译器会自动将不用的门和触发器删除,并且所有输入端口都有默认值,不用的输入端允许不进行任何连接。

综合使用基本逻辑元件库和MAX+plusⅡ库的元件,可设计出大多数传统的方法所能设计的数字电路。

对于用户已有的用74系列器件设计的数字电路,用户可根据原有的电路图很方便地用QuartusⅡ设计出适用于CPLD/FPGA的电路来。

例3畅1 用74151设计一个三人表决电路。

三人表决电路的真值表如表3-1所示。

图3-1 QuartusⅡ原理图输入法可供使用的库表3-1 三人表决电路真值表a b c y00000010010001111000101111011111 其最小项表达式是y=abc+abc+abc+abc 根据y的最小项表达式,就可知道使用74151设计的三人表决电路的原理图。

三人表决电路设计过程如下:在QuartusⅡ中执行File→New...命令,在弹出的编辑文件类型对话框(如图3-2所示)中,选择BlockDiagram/SchematicFile后单击OK按钮,进入QuartusⅡ图形编辑方式。

在原理图编辑区中双击鼠标的左键,在弹出的图3-3所示的元件选择对话框的Libraries栏内通过双击maxplus2选择MAX+plusⅡ库。

图3-3 选择MAX+plusⅡ库在图3-4所示的MAX+plusⅡ库中选择74151器件后单击OK按钮。