原理图输入设计方法

- 格式:ppt

- 大小:3.93 MB

- 文档页数:31

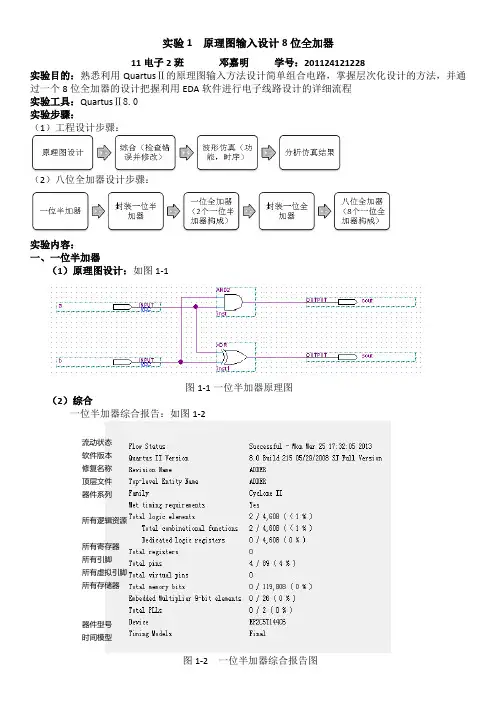

实验1 原理图输入设计8位全加器11电子2班 邓嘉明 学号:201124121228实验目的:熟悉利用Quartus Ⅱ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA 软件进行电子线路设计的详细流程 实验工具:Quartus Ⅱ8.0 实验步骤:(1)工程设计步骤:(2)八位全加器设计步骤:实验内容:一、一位半加器(1)原理图设计:如图1-1图1-1一位半加器原理图(2)综合一位半加器综合报告:如图1-2图1-2 一位半加器综合报告图流动状态 软件版本 修复名称 顶层文件 器件系列所有逻辑资源所有寄存器 所有引脚 所有虚拟引脚 所有存储器 器件型号 时间模型(3)功能仿真半加器功能仿真波形图:如图1-3图1-3半加器波形仿真图半加器理论的结果:如表1-1结论:图所以波形图仿真时成功的。

(4)时序仿真半加器时序仿真波形图:如图1-4图1-4 半加器时序仿真波形图结论:时序仿真没有出现毛刺,只能说明这次试验比较幸运。

延时情况:如图1-5注:tsu(建立时间),th(保持时间),tco(时钟至输出延时),tpd(引脚至引脚延时)图1-5 半加器时序仿真延时情况(5)封装一位半加器的封装:如图1-6图1-6 一位半加器封装二、一位全加器(1)一位全加器原理图设计:如图2-1图2-1 一位全加器原理图(2)综合一位全加器综合报告:如图2-2图2-2 一位全加器综合报告(3)功能仿真一位全加器功能仿真波形图:如图2-3果,所以波形图仿真时成功的。

(4)时序仿真一位全加器时序仿真波形图:如图2-4图2-4 一位全加器时序仿真波形图结论:一位全加器时序仿真结果没有出现毛刺,只能说明这次试验比较幸运。

延时情况:如图2-5图2-5 一位全加器时序仿真延时情况(5)封装一位全加器封装:如图2-6图2-6 一位全加器封装三、八位全加器(1)原理图设计一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现。

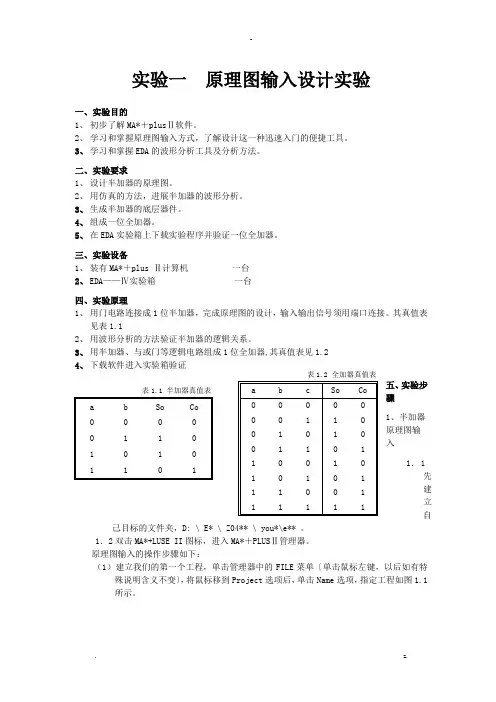

实验一 原理图输入设计实验一、实验目的1、 初步了解MA*+plus Ⅱ软件。

2、 学习和掌握原理图输入方式,了解设计这一种迅速入门的便捷工具。

3、 学习和掌握EDA 的波形分析工具及分析方法。

二、实验要求1、 设计半加器的原理图。

2、 用仿真的方法,进展半加器的波形分析。

3、 生成半加器的底层器件。

4、 组成一位全加器。

5、 在EDA 实验箱上下载实验程序并验证一位全加器。

三、实验设备1、 装有MA*+plus Ⅱ计算机 一台2、 EDA ——Ⅳ实验箱 一台四、实验原理1、 用门电路连接成1位半加器,完成原理图的设计,输入输出信号须用端口连接。

其真值表见表1.12、 用波形分析的方法验证半加器的逻辑关系。

3、 用半加器、与或门等逻辑电路组成1位全加器,其真值表见1.24、 下载软件进入实验箱验证五、实验步骤 1、半加器原理图输入1. 1先建立自己目标的文件夹,D: \ E* \ Z04** \ you*\e** 。

1.2双击MA*+LUSE II 图标,进入MA*+PLUS Ⅱ管理器。

原理图输入的操作步骤如下: (1) 建立我们的第一个工程,单击管理器中的FILE 菜单〔单击鼠标左键,以后如有特殊说明含义不变〕,将鼠标移到Project 选项后,单击Name 选项,指定工程如图1.1所示。

表1.2 全加器真值表表1.1 半加器真值表图1.1 指定工程名的屏幕在Project Name的输入编辑框中,键入设计半加器工程名称"hadder〞,屏幕如图1.1所示:(注意工程所存放的目录):(2)再在管理器中单击File \ New选项,设定图形文件。

选择Graphic Editor file,单击OK按钮后,便进入到MA*+PLUSE II 的图形编辑器。

(3)归属工程文件 File \ Project \ Set Project to Current File;(4)保存半加器的文件名;屏幕如图1.2所示;图1.2 欲保存文件前的屏幕(5)如图1.3所示,选择图形编辑器的Symbol Name 输入编辑框中键入AND2后,单击ok按钮。

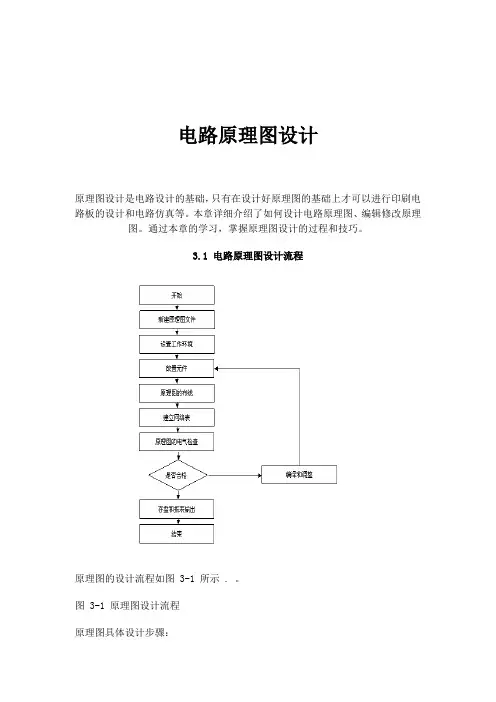

电路原理图设计原理图设计是电路设计的基础,只有在设计好原理图的基础上才可以进行印刷电路板的设计和电路仿真等。

本章详细介绍了如何设计电路原理图、编辑修改原理图。

通过本章的学习,掌握原理图设计的过程和技巧。

3.1 电路原理图设计流程原理图的设计流程如图 3-1 所示 . 。

图 3-1 原理图设计流程原理图具体设计步骤:( 1 )新建原理图文件。

在进人 SCH 设计系统之前,首先要构思好原理图,即必须知道所设计的项目需要哪些电路来完成,然后用 Protel DXP 来画出电路原理图。

( 2 )设置工作环境。

根据实际电路的复杂程度来设置图纸的大小。

在电路设计的整个过程中,图纸的大小都可以不断地调整,设置合适的图纸大小是完成原理图设计的第一步。

( 3 )放置元件。

从元件库中选取元件,布置到图纸的合适位置,并对元件的名称、封装进行定义和设定,根据元件之间的走线等联系对元件在工作平面上的位置进行调整和修改使得原理图美观而且易懂。

( 4 )原理图的布线。

根据实际电路的需要,利用 SCH 提供的各种工具、指令进行布线,将工作平面上的器件用具有电气意义的导线、符号连接起来,构成一幅完整的电路原理图。

( 5 )建立网络表。

完成上面的步骤以后,可以看到一张完整的电路原理图了,但是要完成电路板的设计,就需要生成一个网络表文件。

网络表是电路板和电路原理图之间的重要纽带。

( 6 )原理图的电气检查。

当完成原理图布线后,需要设置项目选项来编译当前项目,利用 Protel DXP 提供的错误检查报告修改原理图。

( 7 )编译和调整。

如果原理图已通过电气检查,那么原理图的设计就完成了。

这是对于一般电路设计而言,尤其是较大的项目,通常需要对电路的多次修改才能够通过电气检查。

( 8 )存盘和报表输出: Protel DXP 提供了利用各种报表工具生成的报表(如网络表、元件清单等),同时可以对设计好的原理图和各种报表进行存盘和输出打印,为印刷板电路的设计做好准备。

实验一 原理图输入设计一、实验目的1.熟悉QuartusII 9.1软件的使用。

2.通过半加器的设计,让学生掌握原理图输入的设计方法。

3.初步了解可编程器件设计的全过程。

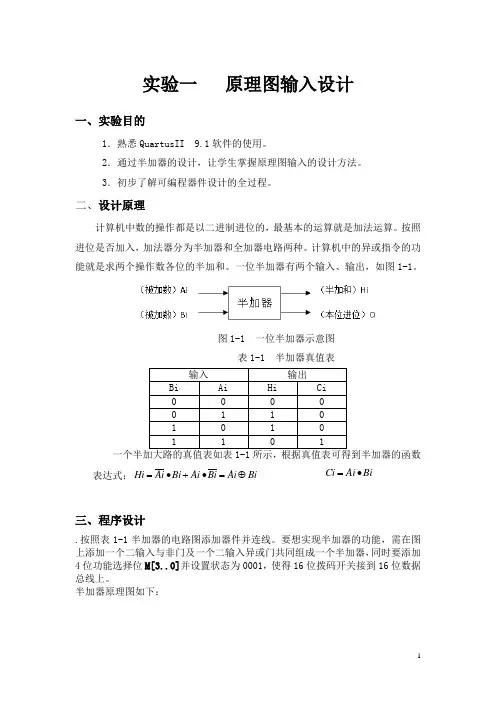

二、设计原理计算机中数的操作都是以二进制进位的,最基本的运算就是加法运算。

按照进位是否加入,加法器分为半加器和全加器电路两种。

计算机中的异或指令的功能就是求两个操作数各位的半加和。

一位半加器有两个输入、输出,如图1-1。

图1-1 一位半加器示意图表1-1 半加器真值表输入输出Bi Ai Hi Ci0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1一个半加大路的真值表如表1-1所示,根据真值表可得到半加器的函数表达式:Hi Ai Bi Ai Bi Ai Bi =∙+∙=⊕ Bi Ai Ci ∙=三、程序设计.按照表1-1半加器的电路图添加器件并连线。

要想实现半加器的功能,需在图上添加一个二输入与非门及一个二输入异或门共同组成一个半加器,同时要添加4位功能选择位M[3..0]并设置状态为0001,使得16位拨码开关接到16位数据总线上。

半加器原理图如下:四、程序分析输入输出Bi Ai Hi Ci0 0 0 00 1 1 01 0 1 01 1 0 1由表可知,Hi与Ai,Bi的关系满足异或关系,Ci与Ai,Bi的关系是与的关系。

五程序调试1.编译过程中出现Error: The core supply voltage value of '1.0V' is illegal for the currently,需要简单修改一下*.qsf文件,找到“set_global_assignment - name NOMINAL_CORE_SUPPLY_VOLTAGE”这一行代码,把里面的1.0V改成1.2V。

并保存*.qsf文件。

再次编译,程序无错误。

2添加管脚信息,综合完成后,网表信息会生成。

选择Assignments/Pin Planner进行管脚锁定,锁定所有的输入输出管脚。

实验一 用原理图输入法设计门电路

一、实验目的

1、通过一个简单的反相器的现实,初步了解CPLD 开发的全过程。

2、学会利用软件仿真和硬件实现对数字电路的逻辑功能进行验证和分析。

3、能够通过CPLD 开发实现具有反相器功能的数字电路。

二、实验内容

用原理图输入法设计一个一位二进制全加器门电路。

三、实验逻辑功能分析及预习情况

一个一位二进制全加器:加数为A ,B ,低位进位CI ,向高位进位FC ,本位和F 。

FC= CI AB+CI A B+ CIA B +CIAB=AB+CI(A ⊕B )=)(B A CI AB ⊕∙ F=B A CI B A CI B A CI CIAB B A CI B A CI B A CI ⊕⊕=⊕+⊕=+++)()(

四、实验过程

(1)启动MAX+plusII 软件;

(2)创建一个新工程;

(3)原理图编辑;

按照上面的公式编辑原理图,如下

(4)保存、编译原理图;

(5)启动波形图编译器;

设计End time为1.0us,Grid Size为50.0ns。

结果如下:

(6)时间分析图

(7)利用真值表验证所设电路的逻辑功能;

(8)经过验证保存仿真原理图。

五、实验感受

通过本次实验我学会了利用软件仿真和硬件实现对数字电路的逻辑功能进行验证和分析。

使我对MAX+plusII有了初步的了解,通过本次实验我学会了此软件的基本操作方法。

同时让我了解到硬件可以用软件来完成,此软件的模拟仿真给我们学习数字电路有很大的帮助,形象的表达了信号的输出。