基于FPGA的数字频率及设计与实现

- 格式:doc

- 大小:342.50 KB

- 文档页数:32

基于FPGA平台的数字频率合成器的设计和实现数字频率合成技术是一种实现高精度频率合成的方法,具有广泛应用价值。

在数字频率合成中,FPGA是一种非常重要的平台,能够实现高速、高精度、可编程的数字频率合成。

本文将介绍基于FPGA平台的数字频率合成器的设计和实现。

一、FPGA简介FPGA是一种可以编程的数字集成电路,具有非常灵活的可编程性。

FPGA中包含了大量的逻辑单元、存储单元和输入输出接口,可以通过编程实现各种数字电路功能。

FPGA具有高速、高度集成、低功耗等优点,在数字电路的设计和实现中得到了广泛应用。

二、数字频率合成的基本原理数字频率合成是通过一组特定的频率合成器和相位加法器来合成所需要的频率。

首先,将参考频率和相位加法器连接起来,形成一个频率合成器。

然后,将输出频率与参考频率的比例进行数字控制,并将输出频率的相位与参考频率相位进行加法计算,最终输出要求的频率。

三、数字频率合成器的设计1. 参考频率生成模块参考频率生成模块是数字频率合成器的核心模块。

参考频率一般使用晶振作为输入信号,并通过频率除和锁相环等技术来产生高精度的参考频率。

在FPGA中,可以使用PLL、DCM等IP核来实现参考频率的生成。

2. 分频器分频器是将参考频率转化为所需的输出频率的模块,一般使用计数器实现。

在FPGA中,可以使用计数器IP核或使用Verilog等HDL语言来实现。

3. 相位加法器相位加法器用于将输出频率的相位和参考频率的相位相加。

在FPGA中,可以使用LUT(查找表)实现相位加法器。

4. 控制单元控制单元用于控制数字频率合成器的各个模块,并实现与外部设备的接口。

在FPGA中,可以使用微处理器或FPGA内部逻辑来实现控制单元。

四、数字频率合成器的实现数字频率合成器的实现需要进行数字电路设计和FPGA编程。

一般来说,可以采用Verilog或VHDL等硬件描述语言进行FPGA编程,实现各个模块的功能。

数字电路设计过程中,需要考虑到功耗、面积和时序等问题,同时需要进行仿真和验证。

目录前言...............................................................1 第一章 FPGA及Verilog HDL..........................................2 1.1 FPGA简介.....................................................2 1.2 Verilog HDL 概述.............................................2 第二章数字频率计的设计原理........................................3 2.1 设计要求.....................................................3 2.2 频率测量.....................................................3 2.3.系统的硬件框架设计..............................................4 2.4系统设计与方案论证............................................5 第三章数字频率计的设计............................................8 3.1系统设计顶层电路原理图........................................8 3.2频率计的VHDL设计.............................................9 第四章软件的测试...............................................15 4.1测试的环境——MAX+plusII.....................................15 4.2调试和器件编程...............................................15 4.3频率测试.....................................................16基于FPGA的等精度频率计的设计与实现摘要:本文详细介绍了一种基于FPGA的高精度频率计。

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=NT进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX 的个数,则有公式可得Fx=1ГX=NTR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1T(频率=1周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГXTR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

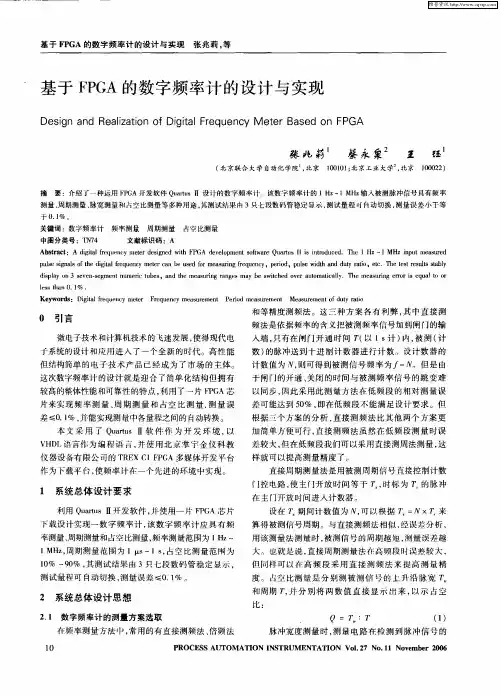

方案三:等精度测频,按定义式F=NT进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1ГX=NTR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

本科生毕业论文题目:基于fpga的等精度数字频率计的设计摘要在电子工程,资源勘探,仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。

频率测量也是电子测量技术中最基本最常见的测量之一。

不少物理量的测量,如转速、振动频率等的测量都涉及到或可以转化为频率的测量。

基于传统测频原理的频率计的测量精度会随被测信号频率的下降而降低。

本文介绍了一种基于FPGA的等精度数字频率计,它不但具有较高的测量精度,而且在整个测量区域能保持恒定的测量精度。

文章首先介绍了硬件描述语言(HDL)的发展,以VHDL为核心,说明了利用VHDL语言进行设计的步骤。

然后介绍FPGA器件的基本结构和开发流程,接着阐述等精度数字频率计的工作原理以及利用VHDL语言实现数字频率计的具体做法,重点是利用BCD码减法实现的BCD码除法器的设计,最后还利用modelsim软件对其进行了仿真,具体分析验证了此设计的正确性。

关键词:FPGA VHDL 等精度BCD码除法AbstractCymometer is a necessary measure tool for technical engineers in electronic engineering , resource exploration and apparatus using . frequency mesure is one of the most essential and the most common mesure of electronic mesure technology . many physical quantities’ mesure , such as rotate speed , vibration frequency’s mesure , is related with or can be transformed into frequency mesure.The precision of cymometer based on traditional frequency-testing theory will decrese when the measured frequency becomes lower. this article introduces a cymometer of same-precision based on FPGA. The cymometer not only has high precision, but also its precision doesn’t decrese when the measured frequency becomes lower.This article first introduces the development of HDL , focusing on VHDL , present the step of design of VHDL . then it introduces the basic structure and the develop flow of FPGA device . in the end , it introduces the theory of cymometer and the specific implement of cymometer based on VHDL , emphasizing the theory of implementing BCD division. the function simulation and logic synthesis also come out, showing the correction of the design .Keywords: FPGA VHDL same-precision BCD division目录第一章前言............................................................................................................... 错误!未定义书签。

基于FPGA的并行处理实现数字中频的设计什么是数字中频?数字中频(Digital Intermediate Frequency,DIF)是现代通信设备中的一个重要概念。

通信系统的本质是传输信息,而信息通常是通过变化的信号进行表示的。

在数字通信中,采用的是数字信号。

信号需要传输到接收端,但是在传输过程中受到了噪声和失真等干扰,因此需要进行滤波和整形处理,将原始信号转换为合适的数字信号。

数字中频处理就是在信号传输过程中将原始信号转换成一个中频信号进行处理,然后再将中频信号转换成数字信号。

中频信号具有一定的宽带性和抗干扰能力,因此可以更好地保留原始信号的特性。

FPGA处理器基础FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以通过编程来实现不同的逻辑电路功能。

FPGA的特点是可重构性强、功耗低、时钟频率高、内部存储容量大、接口丰富等。

由于这些特点,FPGA通常被用于高性能计算、数字信号处理、高速数字系统通信等领域。

FPGA内部主要由可编程逻辑单元(Programmable Logic Blocks,PLB)和专用硬件模块构成,可以通过编程实现不同逻辑电路的功能,并且可以通过接口与外围设备进行通信。

因为FPGA的可编程性,所以一个硬件设备可以在不改变硬件电路结构的情况下改变其功能,这是传统基于硬件设计的电路无法实现的。

FPGA内部分为两种资源,一种资源为可编程逻辑资源,主要用于实现自定义的逻辑电路,另一种资源为系统资源,主要包括许多硬件模块,如乘法器、高速存储器、DMA控制器、时钟管理单元等。

这两种资源结合起来,可以构建出具有高性能和高可靠性的系统。

基于FPGA的数字中频处理器FPGA的高度可编程性和实时性特点,使得其成为数字中频处理器的理想实现平台。

由于数字中频处理器涉及到复杂的数字信号处理算法,因此需要使用高效的算法和数据结构来实现。

同时,数字中频处理器需要进行大规模的并行计算,以保证处理速度。

基于 FPGA 的数字频率计的设计与实现随着现代科技的不断发展,我们对数字信号处理的需求也越来越高。

数字频率计作为一种用来测量信号频率的仪器,在许多领域有着广泛的应用,包括无线通信、雷达系统、声音处理等。

在这些应用中,精确、高速的频率测量常常是至关重要的。

而基于 FPGA 的数字频率计正是利用了 FPGA 高速并行处理的特点,能够实现高速、精确的频率计算,因此受到了广泛关注。

本文将从设计思路、硬件实现和软件调试三个方面,对基于 FPGA 的数字频率计的设计与实现进行详细讲解。

一、设计思路1.1 频率计原理数字频率计的基本原理是通过对信号进行数字化,然后用计数器来记录单位时间内信号的周期数,最后根据计数器的数值和单位时间来计算信号的频率。

在 FPGA 中,可以通过硬件逻辑来实现这一过程,从而实现高速的频率计算。

1.2 FPGA 的优势FPGA 作为一种可编程逻辑器件,具有并行处理能力强、时钟频率高、资源丰富等优点。

这些特点使得 FPGA 在数字频率计的实现中具有天然的优势,能够实现高速、精确的频率测量。

1.3 设计方案在设计数字频率计时,可以采用过采样的方法,即对输入信号进行过取样,得到更高精度的测量结果。

还可以结合 PLL 锁相环等技术,对输入信号进行同步、滤波处理,提高频率测量的准确性和稳定性。

二、硬件实现2.1 信号采集在 FPGA 中,通常采用外部 ADC 转换芯片来对输入信号进行模数转换。

通过合理的采样率和分辨率设置,可以保证对输入信号进行精确的数字化处理。

2.2 计数器设计频率计最关键的部分就是计数器的设计。

在 FPGA 中,可以利用计数器模块对输入信号进行计数,并将计数结果送入逻辑单元进行进一步的处理。

2.3 频率计算通过对计数结果进行适当的处理和归一化,可以得到最终的信号频率。

在这一过程中,需要注意处理溢出、误差校正等问题,以保证频率测量的准确性和稳定性。

三、软件调试3.1 FPGA 开发环境在进行基于 FPGA 的数字频率计设计时,可以选择常见的开发工具,例如 Xilinx Vivado 或 Quartus II 等。

基于FPGA的高精度频率计设计实验一.实验目的1.熟悉数字存储示波器基本工作原理。

2.掌握硬件测频和测周的基本原理。

3.掌握在现有综合实践平台上开发DSO硬件频率计模块的方案及流程。

二.实验内容1.结合数据采集、存储和触发模块的FPGA代码,理解DSO的基本工作原理。

2.编写FPGA代码完善DSO的频率计模块,实现高精度测频和测周功能。

三.预备知识1.了解综合实践平台硬件结构。

2.熟悉Xilinx ISE Design Suite 13.2开发环境使用方法。

3.熟悉Verilog HDL硬件描述语言的语法及运用。

四.实验设备与工具硬件:测试技术与嵌入式系统综合实践平台,PC机Pentium100 以上,XILINX USB调试下载器。

软件:PC机Win XP操作系统,Xilinx ISE Design Suite 13.2开发环境五.实验步骤1. 打开工程文件SYPT_FPGA.xise2. 打开freq_measure.v和period_measure.v文件,先根据定义好的模块端口输入输出信号,结合测频和测周的原理,在提示添加代码处补充代码:a. 测频模块(freq_measure.v)测频模块的基本功能是测量闸门时间内被测信号的脉冲个数。

实现过程如下:(1)由标准时钟计数产生一个预设闸门信号,然后用被测信号同步预设闸门信号产生实际闸门信号;要求:预设闸门时间可根据用户选择信号(select_parameter)在50ms、100ms、1s、10s 中切换。

具体代码如下图。

(2)标准时钟和被测信号在实际闸门内计数。

标准时钟的计数结果N s放到mea_cnt_fs 中,被测信号的计数结果为N x放到mea_cnt_fx中,输出以上计数结果,并同时输出测频完成标志mea_flag,具体代码如下图。

b. 测周模块(period_measure.v)测周模块的基本功能是把被测信号作为闸门信号,在它的一个周期的时间内,对标准时钟信号计数。

基于FPGA的高精度频率计设计摘要频率计是一种应用非常广泛的电子仪器,也是电子测量领域中的一项重要内容,而高精度的频率计的应用尤为广泛。

目前宽范围、高精度数字式频率计的设计方法大都采用单片机加高速、专用计数器芯片来实现。

传统的频率测量利用分立器件比较麻烦,精度又比较低,输入信号要求过高,很不利于高性能场合应用。

本论文完成了高精度数字频率计硬件设计和软件设计。

该数字频率计主要包括FPGA和单片机两大部分。

其中FPGA部分又可分为数据测量模块、FPGA和单片机接口模块、FPGA和数码管动态扫描部分。

FPGA部分采用verilog语言编写了电路的各模块电路,选用了当前比较流行的EDA开发软件Quartus II作为开发平台,所有模块程序均通过了编译和功能仿真验证。

对测频系统的设计流程、模型的建立和仿真做出了具体详细的研究,验证了该系统的正确性。

单片机部分采用C51编写了控制软件。

本设计中以FPGA器件作为系统控制的核心,其灵活的现场可更改性,可再配置能力,对系统的各种改进非常方便,在不更改硬件电路的基础上还可以进一步提高系统的性能。

关键词:频率计,单片机,FPGA,电子设计自动化Design of High-accuracy Digital Frequency MeterBased on FPGAABSTRACTFrequency meter is a kind of electronic instrument applied widely. A kind of high-accuracy digital frequency meter is designed based on FPGA in this paper.At present extends the scope,the high accuracy digital frequency meter's design method to use the monolithic integrated circuit to add, the special-purpose counter chip mostly to realize high speed.The design of system hardware and system software is accomplished in the paper. System consists of FGPA and MCU. The circuit based on FPGA includes following some parts: data acquisition module, interface between FPGA and MCU, module scanning number tube. Every circuit module is realized by verilog.The platform of development is Quartus II and all modules procedure is demonstrated by compiling and simulation. Detailed research of design flow, model establishment and system simulation is done. The correctness of the system is demonstrated. The software based on MCU is programmed by C51.In this design takes the systems control by the FPGA component the core, its nimble scene alterability, may dispose ability again, is convenient to system's each kind of improvement, in does not change in hardware circuit's foundation also to be possible to further enhance system's performance.The system has the advantage of high-accuracy and convenience. It’s practicability of frequency meter is well.KEY WORDS: Frequency meter, MCU, FPGA, electronic design automation目录摘要........................................................................................................................................ I ABSTRACT .............................................................................................................................. I I 第1章绪论 (1)1.1研究背景及意义 (1)1.2国内外研究现状 (1)1.2.1 频率计的测量方法 (1)1.3EDA技术简介 (3)1.4本论文内容及安排 (4)第2章频率测量方法与原理 (6)2.1直接测频法 (6)2.2利用电路的频率特性进行测量 (7)2.2.1 电桥法测频 (8)2.2.2 谐振法测频 (8)2.2.3 频率—电压转换法测频 (8)2.3等精度测量法 (8)2.4本章小结 (10)第3章系统总体设计方案 (11)3.1频率计系统设计任务与分析 (11)3.1.1 频率计系统设计任务要求 (11)3.1.2 频率计系统设计任务分析 (11)3.2系统总体设计方案 (11)3.3FPGA内部功能模块设计 (12)3.4本章小结 (14)第4章系统的硬件电路设计 (15)4.1FPGA部分的硬件设计 (15)4.1.1 FPGA简介 (15)4.1.2 FPGA芯片的选型 (15)4.2单片机部分的硬件电路设计 (17)4.2.1 单片机的选型原则 (17)4.2.2 单片机控制电路的设计 (18)4.3外围电路设计 (19)4.3.1 键盘接口电路 (19)4.3.2 显示电路 (19)4.3.3 电源电路 (20)4.3.4 信号放大整形电路 (20)4.3.4 其它电路 (21)4.4本章小结 (22)第5章系统的软件设计 (23)5.1VERILOG HDL语言简介 (23)5.2QUARTUS II软件简介 (24)5.3基于EDA技术的设计方法 (25)5.3.1 自底向上的设计方法 (25)5.3.2 自顶向下的设计方法 (26)5.4FPGA内部功能模块设计 (26)5.4.1 D触发器模块 (27)5.4.2 32位高速计数器模块 (28)5.4.3 二选一选择器模块 (29)5.4.4 并—串转换接口模块 (31)5.4.5 串—并转换接口模块 (31)5.4.6 二进制数到8421BCD码转换模块 (32)5.4.7 LED动态扫描显示控制模块 (33)5.5单片机部分的软件设计 (35)5.6本章小结 (36)第6章结论 (37)致谢 (39)参考文献 (40)附录I 顶层原理图 (42)附录II VERILOG程序源代码 (43)基于FPGA的高精度频率计设计 1第1章绪论1.1 研究背景及意义在电子测量技术领域内,频率是一个最基本的参数。

基于FPGA的数字频率计设计随着科学技术的不断进步,数字电子技术在各个领域都得到了广泛的应用。

其中,FPGA(现场可编程门阵列)作为一种灵活、可编程、可重构的数字电路设备,具有较高的性能和灵活性,被广泛应用于数字信号处理、通信、图像处理等各个领域。

本篇文章将介绍基于FPGA的数字频率计设计。

一、概述数字频率计是一种用于测量信号频率的设备,可以方便快速地获取信号的频率信息。

传统的数字频率计通常采用微处理器或专用集成电路来实现,但是这些方案在某些应用场景下存在着局限性。

使用FPGA来设计数字频率计,既可以充分利用FPGA的灵活性和并行性,又可以实现高性能和低功耗的设计。

二、基于FPGA的数字频率计设计原理基于FPGA的数字频率计主要通过计数器和时钟信号来实现。

其设计原理可以分为以下几个步骤:1. 时钟信号同步:通过FPGA内部的PLL(锁相环)模块,可以实现时钟信号的同步和稳定。

2. 信号输入:将待测信号输入FPGA,可以通过外部接口或模拟输入模块实现。

3. 计数器设计:利用FPGA内部的计数器模块,对输入信号进行计数,从而获取信号的频率信息。

4. 频率计算:根据计数器的计数值和时钟信号的周期,可以计算出输入信号的频率信息。

三、基于FPGA的数字频率计设计实现基于上述原理,可以利用FPGA内部的逻辑资源,设计出一个高性能的数字频率计。

具体实现步骤如下:1. 确定输入信号的接口:选择适合的输入接口,可以是数字信号接口、模拟信号接口或者通用IO口。

2. 设计计数器模块:根据待测信号的频率范围和精度要求,设计合适的计数器模块,可以结合FPGA的时钟管理模块实现高精度计数。

3. 编写频率计算算法:根据计数器得到的计数值和时钟信号的周期,设计频率计算算法,可以采用移位运算、累加运算等实现高效的频率计算。

4. 实现显示与输出:设计合适的显示模块和输出接口,将测得的频率信息在显示屏或者外部设备上进行输出。

四、基于FPGA的数字频率计设计应用基于FPGA的数字频率计设计可以广泛应用于各种领域,如通信、测控、仪器仪表等。

电子科技大学(基于FPGA的频率计设计)题目:简易频率计的设计指导教师:********学号:**********专业:光电学院一专业摘要本文主要介绍了基于FPGA 的简易多量程频率计的设计,使用硬件描述语言verilog来实现对硬件的控制,在软件ISE上实现编程的编译综合,在系统时钟48Mhz下可正常工作。

该数字频率计采用测频的方法,能准确的测量频率在10Hz到100MHz之间的信号。

使用ModelSim仿真软件对Verilog程序做了仿真,并完成了综合布局布线,通过ISE下载到Spartan3A开发板上完成测试。

关键词:FPGA ,verilog,ISE,测频方法AbstractThis paper mainly introduces the simple more range based on FPGA design of frequency meter,Use hardware description language verilog to realize the control of hardware,In the software realize the compilation of the programming ISE on comprehensive,In the system clock can work normally under 48 Mhz。

The digital frequency meter frequency measurement method used, can accurate measurement frequency in 10 Hz to 100 MHz of signals between。

Use ModelSim simulation software Verilog program to do the simulation, and completed the overall layout wiring,Through the ISE downloaded to Spartan3A development board complete test。

哈尔滨工业大学华德应用技术学院毕业设计(论文)第1章绪论1.1 课题背景与意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,频率的测量就显得尤为重要,而频率计的研究工作更具有重大的科研意义。

由于大规模和超大规模数字集成电路技术、数据通信技术与单片机技术的结合,数字频率计发展进入了智能化和微型化的新阶段。

近年来,随着电子设计技术的飞速发展,数字电路的研究及应用出现了广阔的空间。

利用FPGA(Field Programmable Gate Array)的设计软件可以将设计好的程序“烧写”到FPGA器件中,如同自行设计集成电路一样,可以节省电路开发的费用与时间。

Altera公司提供的Quartus II软件进行FPGA设计开发流程,根据设计需要可以进行原理图、硬件描述语言进行设计,并进行编译仿真,配合Modelsim仿真软件测试设计功能的实现。

1.2 本课题主要研究内容传统频率计设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着可编程逻辑器件(CPLD/FPGA)的广泛应用,以EDA工具作为开发手段,运用硬件描述语言(VHDL/Verilog),将使整个系统大大简化,提高整体的性能和可靠性。

而本课题正是采用硬件描述语言对数字频率计进行设计,整个系统非常精简,而且具有灵活的现场可更改性,在不更改硬件电路的基础上,可以对系统进行各种改进来进一步提高系统的性能,因此该数字频率计具有精确、可靠、和现场可编程等优点。

本设计所能达到的技术指标如下:1.能测量输入信号的频率范围为1hz~99Mhz;2.波形可以是方波等任何有固定频率的信号;3.运用硬件描述语言和原理图法进行设计;4.运用Quartus II软件进行设计和Modelsim软件仿真。

-1-哈尔滨工业大学华德应用技术学院毕业设计(论文)第2章FPGA开发相关知识简介2.1 FPGA的介绍FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称。

FPGA器件及其开发系统是开发大规模数字集成电路的新技术。

它利用计算机辅助设计,绘制出实现用户逻辑的原理图、编辑布尔方程或用硬件描述语言等方式作为设计输入;然后经一系列转换程序、自动布局布线、模拟仿真的过程;最后生成配置FPGA器件的数据文件,对FPGA器件初始化。

这样就实现了满足用户要求的专用集成电路,真正打到了用户自行设计、自行研制和自行生产集成电路的目的。

总的来说,FPGA器件具有下列优点:高密度、高速度、系列化、标准化、小型化、多功能、低功耗、低成本、,设计灵活方便,可无限次反复编程,并可现场模拟调试验证。

使用FPGA器件,一般可在几天到几周内完成一个电子系统的设计和制作,可以缩短研制周期,达到快速上市和进一步降低成本的要求。

FP GA的基本特点主要有:1.采用FP GA设计AS IC电路,用户不需要投片生产就能得到合用的芯片;2.FP GA可做其它全定制或半定制AS IC电路的中试样片。

3.FP GA内部有丰富的触发器和/I O引脚;4.FP GA是AS IC电路中设计周期最短、开发费用最低、风险最小的器件之一;5.FP GA采用高速C MOS工艺,功耗低,可以与C MOS、TTL电平兼容。

FP GA是由存放在片内R AM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPR OM中数据读入片内编程R AM中,配置完成后,FP GA进入工作状态。

掉电后,FP GA恢复成白片,-2-哈尔滨工业大学华德应用技术学院毕业设计(论文)内部逻辑关系消失,因此,FP GA能够反复使用。

FP GA的编程无须专用的FPGA编程器,只须用通用的EP ROM、PR OM编程器即可。

当需要修改FP GA功能时,只需换一片EP ROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FP GA的使用非常灵活。

2.2 FPGA开发环境2.2.1软件开发环境——Quartus II的介绍Quart us II是Alt era提供的FP GA/CP LD开发集成环境,Altera 是世界最大可编程逻辑器件供应商之一。

Quartus II是Alt era前一代FP GA/CP LD集成环境MAX+plus II的更新换代产品,其界面友好、使用便捷。

Quart us II 是Alt era公司的综合性P LD开发软件,支持原理图、VHD L、Veril ogHD L以及AHDL(Alt era Hardware Descript i on Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整P LD设计流程。

Quartus II提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

Quart us II包含许多十分有用的LP M(Librar y ofParam et eriz ed Modul es)模块,它们是复杂或高级系统建构的重要组成成分。

本设计在实现原理图输入多层次设计的同时,大量运用了QuartusII 的元件库,LMP是参数可设置模块库(Library of Parameterized Modules)的缩写,Altera提供的可参数化宏功能模块和LMP函数均基于Altera器件的结构做了优化设计。

LMP功能模块内容非常丰富,每一个模块的功能。

参数含义,使用方法,硬件描述语言模块参数设置以及调用方法都可以在QuartusII中的HELP中查阅到。

设计者可以根据实际电路的设计需要,选择LMP库中的适当模块,并为其设定适当的参数,就能够满足自己的设计需要。

Altera提供的宏功能模块与LMP函数有以下几个方面:1.算术组件:包括累加器,加法器,乘法器和LMP算术函数;2.门电路:包括多路复用器和LMP门函数;3.I/O组件:包括时钟数据恢复(CDR),锁相环(PLL),双数据速率(DDR),千兆位收发器块(GXB),LVDS接收-3-哈尔滨工业大学华德应用技术学院毕业设计(论文)器和发送器,PLL重新配置和远程更新宏功能模块;4.存储器编译器:包括FIFO Partitioner,ROM和ROM宏功能模块;5.存储组件:包括存储器,移位寄存器宏模块和LMP存储器函数。

Quart us II允许来自第三方的ED IF文件输入,并提供了很多EDA软件的接口,Quart us II支持层次化设计,可以在一个新的编辑输入环境中对使用不同输入设计方式完成的模块进行调试,从而解决了原理图和VHD L混合输入设计的问题。

而且Quart us II 拥有性能良好的设计错误定位器,用于确定文本或图形设计中的错误。

Altera Quartus II 作为一种可编程逻辑的设计环境, 因其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

2.2.2软件仿真环境——Modelsim的介绍Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

它采用直接优化的编译技术和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP 核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

主要特点:1.RTL和门级优化,本地编译结构,编译仿真速度快,跨平台跨版本仿真;2.单内核VHDL和Verilog混合仿真;3.源代码模版和助手,项目管理;4.集成了性能分析、波形比较、代码覆盖、数据流ChaseX、SignalSpy、虚拟对象Virtual Object、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能;5.对SystemC的直接支持,和HDL任意混合;-4-哈尔滨工业大学华德应用技术学院毕业设计(论文)6.支持SystemVerilog的设计功能;7.对系统级描述语言的最全面支持,SystemVerilog, SystemC,PSL;ModelSim分几种不同的版本:SE、PE、LE和OEM,其中SE 是最高级的版本,而集成在Actel、Atmel、Altera、Xilinx以及Lattice 等FPGA厂商设计工具中的均是其OEM版本。

SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。

ModelSim SE支持PC、UNIX和LINUX混合平台;提供全面完善以及高性能的验证功能;全面支持业界广泛的标准;Mentor Graphics 公司提供业界最好的技术支持与服务。

ModelSim的使用方法:1. 在F盘建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset 输入,cnt作为输出;2. 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程;3. 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可);4. ModelSim有很多窗口,一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了;5. 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟;6.运行Run。

就有波形出来了。

2.3 硬件描述语言——Verilog HDL的介绍任何新生事物的产生都有它的历史沿革,早期的硬件描述语言-5-哈尔滨工业大学华德应用技术学院毕业设计(论文)是以一种高级语言为基础,加上一些特殊的约定而产生的,目的是为了实现RTL级仿真,用以验证设计的正确性,而不必像在传统的手工设计过程中那样,必须等到完成样机后才能进行实测和调试。