ZPW-2000A型无绝缘轨道电路原理说明书

- 格式:docx

- 大小:27.52 KB

- 文档页数:19

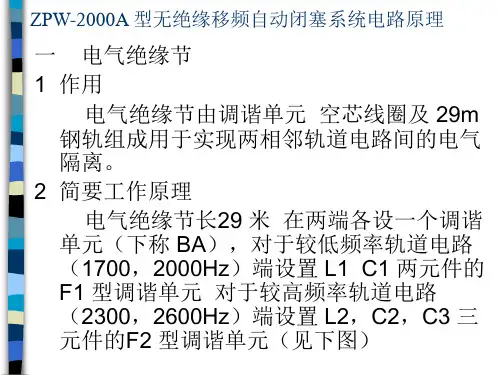

原理说明1.系统原理ZPW-2000A型无绝缘移频轨道电路系统,与UM71无绝缘轨道电路一样采用电气绝缘节来实现相邻轨道电路区段的隔离。

电气绝缘节长度改进为29m,由空心线圈、29m长钢轨和调谐单元构成。

调谐区对于本区段频率呈现极阻抗,利于本区段信号的传输及接收;对于相邻区段频率信号呈现零阻抗,可靠地短路相邻区段信号,防止了越区传输,这样便实现了相邻区段信号的电气绝缘。

同时为了解决全程断轨检查,在调谐区内增加了小轨道电路。

ZPW-2000A型无绝缘移频轨道电路将轨道电路分为主轨道电路和调谐区小轨道电路两个部分,并将短小轨道电路视为列车运行前方主轨道电路的所属“延续段”。

主轨道电路的发送器由编码条件控制产生表示不同含义的低频调制的移频信号,该信号经电缆通道(实际电缆和模拟电缆)传给匹配变压器及调谐单元,因为钢轨是无绝缘的,该信号既向主轨道传送,也向小轨道传送。

主轨道信号经钢轨送到轨道电路受电端,然后经调谐单元、匹配变压器、电缆通道,将信号传至本区段接收器。

调谐区小轨道信号由运行前方相邻轨道电路接收器处理,并将处理结果形成小轨道电路轨道继电器执行条件通过(XG、XGH)送至本轨道电路接收器,做为轨道继电器(GJ)励磁的必要检查条件之一。

本区段接收器同时接收到主轨道移频信号及小轨道电路继电器执行条件,判决无误后驱动轨道电路继电器吸起,并由此来判断区段的空闲与占用情况。

主轨道和调谐区小轨道检查原理示意图见图2-1。

该系统“电气—电气”和“电气—机械”两种绝缘节结构电气性能相同。

2.电路工作原理及冗余设计2.1 发送器2.1.1 用途ZPW-2000A型无绝缘移频轨道电路发送器在区间适用于非电码化和电码化区段18信息无绝缘移频自动闭塞,供自动闭塞、机车信号和超速防护使用。

在车站可适用于非电码化和电码化区段站内移频电码化发送,并可作站内移频轨道电路使用。

2.1.2 原理框图及电路原理简要说明同一载频编码条件,低频编码条件源,以反码形式分别送入两套微处理器CPU中,其中CPU1产生包括低频控制信号Fc的移频信号。

题目ZPW-2000A型轨道电路的原理和技术条件摘要ZPW-2000无绝缘轨道电路换装施工是全路第五次提速调图工程中最重要,最紧迫的信号工程,此次工程要求高、任务重、工期短,而且全路没有现成的开通测试项目集经验。

通过对ZPW-2000无绝缘轨道电路的开通,维护测试,我们认为该轨道电路技术指标的测试调整是开通过程中最关键的无绝缘轨道电路的开通,维护测试,我们认为该轨道电路技术指标的测试调整是开通过程中最关键的一个环节,也是日常维护工作中的最重要的一个环节。

本论文主要阐述了ZPW-2000A无绝缘轨道电路是通过仿真技术开发的,是我国目前最先进的无绝缘、对信息移频轨道电路,其传输安全性、传输长度、可靠性、可维修性能较好,对器材的安装标准和系统指标要求十分严格。

本论文主要阐述了ZPW-2000A无绝缘移频自动闭塞系统的特点、构成、原理说明、区间通过信号机的设置、补偿电容的设置、闭塞区分电路等。

通过本次设计,初步掌握了ZPW-2000A的工作原理、故障处理步骤、方法、内容。

关键词ZPW-2000A;无绝缘;轨道电路AbstractZPW-2000 jointless track circuit device construction is region fifth speed-increasing and rescheduling project the most important, the most urgent signal engineering, the engineering requirements, the task is heavy, short construction period, and the whole region without off-the-peg opening test project experience. Based on the ZPW-2000 jointless track circuit is opened, maintenance and test, we think that the track circuit testing adjustment is opened during the most critical of jointless track circuit opening, maintenance and test, we think that the track circuit testing adjustment is opened during the most crucial link, and daily maintenance in the work of one of the most important links. This paper mainly expounds the ZPW-2000A jointless track circuit is through the simulation technology development, is currently China's most advanced without insulation, on information frequency shift track circuit, the transmission security, the transmission length, reliability, good performance of equipment repair, installation standard and system of indicators are very strict.Through this design, the preliminary master ZPW-2000A's working principle, fault processing steps, methods, contentKey words ZPW-2000A; jointless track circuit;目录第1章绪论 (1)第2章ZPW-2000A无绝缘移频自动闭塞系统概述 (3)2.1ZPW-2000A概述 (3)2.2 ZPW-2000A型无绝缘移频自动闭塞系统特点 (3)2.3 ZPW-2000A型无绝缘轨道电路系统构成 (4)2.3.1 室外部分 ..................................... 错误!未定义书签。

南京铁道职业技术学院毕业论文题目:ZPW-2000无绝缘移频轨道电路原理分析及故障处理作者:卢志刚学号: 06306110132 二级学院:通信信号学院系:铁道信号专业:高铁信号班级: 1101班指导者:王文波助教评阅者:张国候副教授2014年 05 月ZPW-2000无绝缘移频轨道电路原理分析及故障处理摘要 ZPW-2000A系列自动闭塞是将法国的UM71系统国产化的产物。

它充分的吸收了UM71的优点,同时解决了UM71在传输安全性以及传输长度上的问题。

ZPW-2000A系列自动闭塞实现了轨道电路全路断轨检查、调谐单元断线检查,解决了调谐区死区长度,拍频干扰防护等问题。

系统采用了数字处理和单片微机技术,提高了系统的抗干扰能力。

ZPW-2000A无绝缘移频自动闭塞设备目前已经成为了我国电气化区段的主流设备。

本文主要阐述ZPW-2000A型无绝缘移频自动闭塞系统结构及其工作原理,介绍了一些ZPW-2000A无绝缘移频轨道电路的常见故障及处理方法。

关键词 ZPW-2000A、移频、轨道电路、自动闭塞目录1、绪论 (3)2 .ZPW-2000A无绝缘移频轨道电路的概况 (4)2.1 ZPW-2000A型无绝缘轨道电路的构成 (4)2.2 ZPW-2000A型无绝缘轨道电路的特点 (4)3.ZPW-2000A型无绝缘轨道电路的原理分析 (6)3.1发送器 (7)3.2接收器 (8)3.3衰耗器 (10)3.3.1衰耗器电路原理 (10)3.4电缆模拟网络和站防雷 (13)3.5电气绝缘节 (14)3.6匹配变压器 (15)3.7补偿电容 (16)3.8红灯转移原理 (16)4.2 ZPW-2000A无绝缘轨道电路红光带故障判断 (17)4.3常见故障分析 (18)4.4故障案例 (19)结论与展望 (21)致谢 (22)参考文献 (23)1、绪论照我国铁路行业标准《轨道电路通用技术条件》,轨道电路定义为:利用铁路线路的钢轨作为导体传递信息的电路系统。

原理说明1.系统原理ZPW-2000A型无绝缘移频轨道电路系统,与UM71无绝缘轨道电路一样采用电气绝缘节来实现相邻轨道电路区段的隔离。

电气绝缘节长度改进为29m,由空心线圈、29m长钢轨和调谐单元构成。

调谐区对于本区段频率呈现极阻抗,利于本区段信号的传输及接收;对于相邻区段频率信号呈现零阻抗,可靠地短路相邻区段信号,防止了越区传输,这样便实现了相邻区段信号的电气绝缘。

同时为了解决全程断轨检查,在调谐区内增加了小轨道电路。

ZPW-2000A型无绝缘移频轨道电路将轨道电路分为主轨道电路和调谐区小轨道电路两个部分,并将短小轨道电路视为列车运行前方主轨道电路的所属“延续段”。

主轨道电路的发送器由编码条件控制产生表示不同含义的低频调制的移频信号,该信号经电缆通道(实际电缆和模拟电缆)传给匹配变压器及调谐单元,因为钢轨是无绝缘的,该信号既向主轨道传送,也向小轨道传送。

主轨道信号经钢轨送到轨道电路受电端,然后经调谐单元、匹配变压器、电缆通道,将信号传至本区段接收器。

调谐区小轨道信号由运行前方相邻轨道电路接收器处理,并将处理结果形成小轨道电路轨道继电器执行条件通过(XG、XGH)送至本轨道电路接收器,做为轨道继电器(GJ)励磁的必要检查条件之一。

本区段接收器同时接收到主轨道移频信号及小轨道电路继电器执行条件,判决无误后驱动轨道电路继电器吸起,并由此来判断区段的空闲与占用情况。

主轨道和调谐区小轨道检查原理示意图见图2-1。

该系统“电气—电气”和“电气—机械”两种绝缘节结构电气性能相同。

2.电路工作原理及冗余设计2.1 发送器2.1.1 用途ZPW-2000A型无绝缘移频轨道电路发送器在区间适用于非电码化和电码化区段18信息无绝缘移频自动闭塞,供自动闭塞、机车信号和超速防护使用。

在车站可适用于非电码化和电码化区段站内移频电码化发送,并可作站内移频轨道电路使用。

2.1.2 原理框图及电路原理简要说明同一载频编码条件,低频编码条件源,以反码形式分别送入两套微处理器CPU中,其中CPU1产生包括低频控制信号Fc的移频信号。

原理说明1.系统原理ZPW-2000A型无绝缘移频轨道电路系统,与UM71无绝缘轨道电路一样采用电气绝缘节来实现相邻轨道电路区段的隔离。

电气绝缘节长度改进为29m,由空心线圈、29m长钢轨和调谐单元构成。

调谐区对于本区段频率呈现极阻抗,利于本区段信号的传输及接收;对于相邻区段频率信号呈现零阻抗,可靠地短路相邻区段信号,防止了越区传输,这样便实现了相邻区段信号的电气绝缘。

同时为了解决全程断轨检查,在调谐区内增加了小轨道电路。

ZPW-2000A型无绝缘移频轨道电路将轨道电路分为主轨道电路和调谐区小轨道电路两个部分,并将短小轨道电路视为列车运行前方主轨道电路的所属“延续段” 。

主轨道电路的发送器由编码条件控制产生表示不同含义的低频调制的移频信号,该信号经电缆通道(实际电缆和模拟电缆)传给匹配变压器及调谐单元,因为钢轨是无绝缘的,该信号既向主轨道传送,也向小轨道传送。

主轨道信号经钢轨送到轨道电路受电端,然后经调谐单元、匹配变压器、电缆通道,将信号传至本区段接收器。

调谐区小轨道信号由运行前方相邻轨道电路接收器处理,并将处理结果形成小轨道电路轨道继电器执行条件通过(XG、XGH)送至本轨道电路接收器,做为轨道继电器(GJ)励磁的必要检查条件之一。

本区段接收器同时接收到主轨道移频信号及小轨道电路继电器执行条件,判决无误后驱动轨道电路继电器吸起,并由此来判断区段的空闲与占用情况。

主轨道和调谐区小轨道检查原理示意图见图2-1 。

该系统“电气—电气”和“电气—机械”两种绝缘节结构电气性能相同。

2.电路工作原理及冗余设计2.1 发送器2.1.1 用途ZPW-2000A型无绝缘移频轨道电路发送器在区间适用于非电码化和电码化区段18 信息无绝缘移频自动闭塞,供自动闭塞、机车信号和超速防护使用。

在车站可适用于非电码化和电码化区段站内移频电码化发送,并可作站内移频轨道电路使用。

2.1.2 原理框图及电路原理简要说明同一载频编码条件,低频编码条件源,以反码形式分别送入两套微处理器CPU中,其中CPU1产生包括低频控制信号Fc 的移频信号。

移频键控信号FSK分别送至CPU1、CPU2进行频率检测。

检测结果符合规定后,即产生控制输出信号,经“控制与门”使“FSK”信号送至滤波环节,实现方波——正弦波变换。

功放输出的FSK信号送至两CPU进行功出电压检测。

两CPU对FSK信号的低频、载频和幅度特征检测符合要求后发送报警继电器励磁,并使经过功放的FSK信号输出。

当发送输出端短路时,经检测使“控制与门”有10S的关闭(装死或休眠保护)。

(2)微处理器、可编程逻辑器件及作用1、采用双CPU、双软件、双套检测电路、闭环检查。

2、CPU采用80C196,由它构成移频发生器,控制产生移频信号,它还担负着输出信号检测等功能。

3、FPGA可编程逻辑器件,由它构成移频发生器,并行I/O 扩展接口频率计数器等。

(3)低频和载频编码条件的读取1、低频编码条件读取采用24V 电源构成一个功率型、防干扰、有“故障—安全” 保证的电路。

为了实现动态检测,并用光电耦合器实现隔离。

如图所示为18 路低频编码条件读取电路的一路,当CPU 准备读取低频编码条件,先送一低电平到B,使光耦2 导通。

如果这时编码条件处于接通状态,光耦1 应导通。

A 处于低电平状态。

如果编码条件未接通,光耦1 截止,A 处于高电平状态。

根据A 端的电平,就可以判断出低频编码条件是否接通。

在低频编码条件读取电路中,光耦1 起到了关键作用。

如果光耦1 被击穿,接可能导致编码条件读取错误,影响安全。

因此,为了保证低频编码条件读取电路的故障安全,在电路设计中增加了光耦2 电路环节。

在读取CPU编码条件时,送一低电平到B,在检测光耦1 的好坏时,送一高电平到B,使光耦截止,切断编码条件读取电路,若此时光耦1 正常,A应为高电位,若光耦1 故障,A 处就为低电位。

这样,CPU就可以判断出编码条件读取电路是否故障。

如果光耦2 本身故障,CPU也会检测到并报警,这里不再分析。

2、载频编码条件读取载频编码条件读取,与低频编码条件的读取相类同。

(4)稳步信号产生低频、载频编码条件通过并行I/O 接口传到两个CPU 后,首先判断该条件是否有,且仅有一路。

满足条件后,CPU1通过查表得到该编码条件所对应的上下边频数值,控制移频发生器,产生相应FSK信号。

并由CPU1进行自检。

由CPU2进行互检,条件不满足,将由两个CPU构成故障报警。

1、经检测后,CPU各产生一个控制信号、经过“控制与门”,将FSK 信号送至方波正弦波变换器。

2、方波正弦波变换器:该变换器是由可编程低频滤波器260集成芯片构成。

(5)功率放大器1、简化电路从故障—安全及提高功出电压稳定性考虑,功率放大器采用射极输出器,其简化电路见下图3-3。

FSK信号经过B5 输出至共集电极乙类推挽放大器V12、V16分别对输入信号正负半波进行放大。

2.实际电路构成在电路设计中,考虑了以下情况:• 鉴于输出功率圈套,直接由B5通过功率管B6 有较大的功率输出,啬了前级电路负荷。

为此,在构成功率放大过程中,V3(0V18)选用达林顿大功率三极管。

并由V52、V29与V3(0 V20、V19 与V18)、构成多级复合放大。

这样,大大减轻了前级的负荷。

•二极管V27(V15)用于V26(V17)的eb 结温度补偿。

•二极管V24(V21)用于V25(V20)保护。

•V26(V17)也构成过电流防护。

当V25(V20)IC 过高,V26(V17)将导通,构成对后级的“钳位”控制。

• 为了解决eb 死区所构成的交越失真,由R55 和二极管V23、V22给定的的偏压,使得V25(V20)的eb 结处于放大区和死区的交界点处。

(6)安全与门电路对数字电路来讲,当发生故障时,一般表现出固定的高电平1 或固定的低电平0 ,为此,我们把动态方波信号作为正常工作信号,两路CPU正常工作时分别产生各自的方波信号,通过安全与门,产生一个直流信号,发送报警继电器FBJ,如果任何一路方波信号没有,应不会产生直流信号,发送报警继电器将落下,切断移频信号的输出。

当有方波1 时,光耦1 处于开关状态,回路中的电流处于交变状态,变压器隔离以及整流滤波,产生一个独立的直流电源电压信号,此外,如果方波2 存在,那么,光耦2 也处于开关状态,使三极管处于开关状态,通过三极管的放大、变压器的隔离及整流滤波,产生一个直流信号,驱动发送报警继电器。

通过分析可以看出,任何一路方波信号不存在时FBJ都将落下。

(7)软件设计1、设计要求• 软件设计进行精确的需求分析和正确的软件设计。

• 软件在投入正式运营之前,进行全面、系统的测试,和第三者审核,确保没有错误。

• 软件设计结构模块化。

2、软件故障安全的考虑• 采用双锁逻辑,程序进入死循环或停止运行后,保证WDT进行复位。

• 系统检测失效,严格导向安全侧。

• 通过读写测试,保证RAM的正确性。

• 通过校验码测试,保证ROM的正确性。

• 保证系统中断执行过程的完整性。

图2-6 发送器外连接示意图表2-1 区间发送器端子代号及用途表序号代号用途1 D 地线2+24-1+24V电源外引入线3+24-2载频编码用+24V电源(+1FS除外)4024-1024 电源外引入线5024-2备用617001700Hz载频选择720002000Hz载频选择823002300Hz载频选择926002600Hz载频选择10-11 型载频选择11-22 型载频选择12F1~F1810.3Hz~29Hz低频编码选择线131~5、9、11、12 功放输出电平调整端子14S1、S2功放输出端子15T1、T2测试端子16FBJ-1FBJ-2 外接FBJ(发送报警继电器端子)图2-7 发送器“ n+1”冗余系统原理接线图2.2 接收器2.2.1 用途用于对主轨道电路移频信号的解调,并配合与送电端相连接调谐区短小轨道电路的检查条件,动作轨道继电器。

另外,还实现对与受电端相连接调谐区短小轨道电路移频信号的解调,给出短小轨道电路执行条件,送至相邻轨道电路接收器。

接收器接收端及输出端均按双机并联运用设计,与另一台接收器构成相互热机并联运用系统,保证接收系统的高可靠运用。

2.2.2 电路原理介绍(1)接收器双机并联运用原理接收器由本接收“主机”及另一接收“主机”两部分构成。

ZPW-2000A系统中A、B 两台接收器构成成对双机并联运用,即:A 主机输入接至A主机,且并联接至B主机。

B 主机输入接至B主机,且并联接至A主机。

A 主机输出与B 并机输出并联,动作A 主机相应执行对象。

B 主机输出与A 并机输出并联,动作B 主机相应执行对象。

(2)接收器原理框图及说明主轨道A/D,小轨道A/D:模数转换器,将主机、并机输入的模拟信号转换成计算机能处理的数字信号。

CPU1、CPU2:是微机系统,完成主机、并机载频判决、信号采样、信息判决和输出驱动等功能。

安全与门1~4:将两路CPU输出的动态信号变成驱动继电器(或执行条件)的直流输出。

载频选择电路:根据要求,利用外部的接点,设定主机、并机载频信号,由CPU进行判决,确定接收盒的接收频率。

接收盒根据外部所确定载频条件,首先确定接收盒的中心频率。

外部送进来的信号,分别经过主机、并机两路模数转换器转换成数字信号。

两套CPU 对外部四路信号进行单独的运算,判决处理。

双CPU再把处理的结果通过串行通信,相互进行比较。

如果判决结果一致,就输出3KHz 的脉冲驱动安全与门。

安全与门接收到两路方波信号后,将其转换成直流电压带动继电器。

如果双CPU的结果不一致,就关掉给安全与门的脉冲,同时报警。

电路中增加了安全与门的反馈检查,如果CPU有动态输出,那么安全与门就应该有直流输出,否则就认为安全与门故障,接收器也报警。

如果接收盒收到的信号电压过低,就认为是列车分路。

(3)载频读取电路接收载频读取电路与发送低频载频读取电路类似,载频通过相应端子接通24V 电源确定,通过光电耦合器将静态的直流信号转换成动态的交流信号,由双CPU进行识别和处理,并实现外界电路与数字电路的隔离(详细分析略)。

(4)微处理器电路微处理器电路采用双CPU、双软件。

两套软件硬件对信号单独处理,把结果相互较核,实现故障—安全。

其原理框图见图。

CPU采用数字信号处理器TMS320C3。

21、CPU完成信号的采样、运算判决和控制能力。

该CPU每秒钟能完成1 千万次加法、减法或乘法运算。

2、数据存储器(RAM):用于存放采集的数据和运算的结果。

数据存储器供电后可以对其运算读写处理,断电后其内部数据就消失不保存。

3、程序存储器(EPRO)M:是程序的载体,CPU执行的指令和运算需要的常数储存在其中。