Verilog HDL入门基础之门级建模

- 格式:pdf

- 大小:602.58 KB

- 文档页数:9

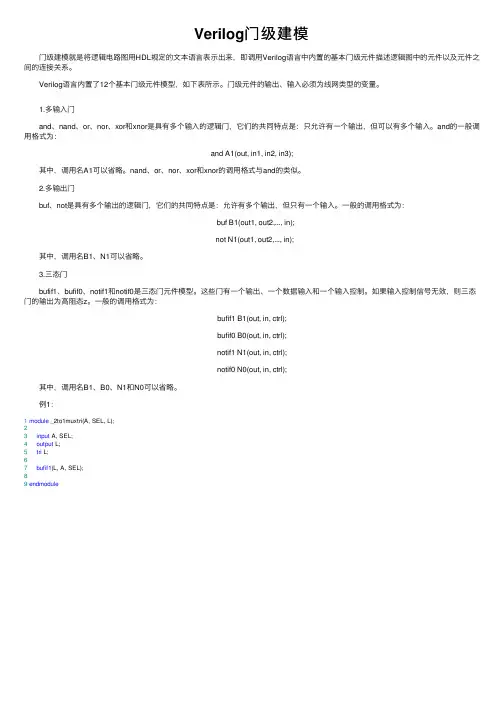

Verilog门级建模 门级建模就是将逻辑电路图⽤HDL规定的⽂本语⾔表⽰出来,即调⽤Verilog语⾔中内置的基本门级元件描述逻辑图中的元件以及元件之间的连接关系。

Verilog语⾔内置了12个基本门级元件模型,如下表所⽰。

门级元件的输出、输⼊必须为线⽹类型的变量。

1.多输⼊门 and、nand、or、nor、xor和xnor是具有多个输⼊的逻辑门,它们的共同特点是:只允许有⼀个输出,但可以有多个输⼊。

and的⼀般调⽤格式为:and A1(out, in1, in2, in3); 其中,调⽤名A1可以省略。

nand、or、nor、xor和xnor的调⽤格式与and的类似。

2.多输出门 buf、not是具有多个输出的逻辑门,它们的共同特点是:允许有多个输出,但只有⼀个输⼊。

⼀般的调⽤格式为: buf B1(out1, out2,..., in);not N1(out1, out2,..., in); 其中,调⽤名B1、N1可以省略。

3.三态门 bufif1、bufif0、notif1和notif0是三态门元件模型。

这些门有⼀个输出、⼀个数据输⼊和⼀个输⼊控制。

如果输⼊控制信号⽆效,则三态门的输出为⾼阻态z。

⼀般的调⽤格式为:bufif1 B1(out, in, ctrl);bufif0 B0(out, in, ctrl);notif1 N1(out, in, ctrl);notif0 N0(out, in, ctrl); 其中,调⽤名B1、B0、N1和N0可以省略。

例1:1module _2to1muxtri(A, SEL, L);23input A, SEL;4output L;5tri L;67bufif1(L, A, SEL);89endmodule。

第四章 Verilog-HDL的建模1.内容回顾通常认为,给硬件建模的模型可以分为5个层次:▪系统级和算法级建模通常是软件工程师用C语言开发的软件模型,目的在于验证设计思想是否正确。

HDL也能做一些算法级建模的工作,但是有很多算法描述不被综合工具支持。

▪行为级建模主要考虑一个模块的抽象功能描述,而不考虑其具体以实现(具体电路结构由综合工具得到)。

▪门级模型是对电路结构的具体描述,主要是描述与、或、非等基本门电路的连接方式。

▪开关级模型是把最基本的MOS晶体管连接起来实现电路功能。

注:这5个层次从高到低越来越接近硬件。

Verilog HDL有两种建模方法:结构建模方法和行为建模方法。

结构建模方法是对电路具体结构的描述:1.调用Verilog内置门元件(门级结构描述)2.调用开关级元件(晶体管级结构描述)3.用户自定义元件UDP(也在门级)4.子模块调用行为建模方法是对电路功能的描述1.数据流行为建模2.顺序行为建模2.结构建模结构建模是对电路具体结构的描述,是一种比较底层的方法。

简单说,就是把所需要的基本电路单元(逻辑门、MOS开关等)调出来,再用连线把这些基本单元连接起来。

(调用、连线)。

2.1 内置的基本单元Verilog HDL为门级电路建模提供了26个内置基本单元,分类如下:多输入门:and, nand, or, nor, xor, xnor多输出门:buf, not三态门: bufif0, bufif1, notif0, notif1上拉、下拉电阻:pullup, pulldownMOS开关:cmos, nmos, pmos, rcmos, rnmos, rpmos双向开关:tran,tranif0, tranif1, rtran, rtranif0, rtranif1注:多输入门、多输出门和三态门构成Verilog-HDL的内置基本门。

2.1.1多输入门1.内置的多输入门包括: and nand nor or xor xnor2.这些逻辑门只有单个输出, 1个或多个输入。

西安郵電學院verilog设计基础课内实验报告书系部名称:计算机系学生姓名:常成娟专业名称:电子信息科学与技术班级:电科0603学号:22号时间: 2006-9-11 至 2006-9-22实验题目门级建模一、实验内容1、使用bufif0和bufif1设计一个二选一多路选择器;2、在设计完成后,写出激励模块对其进行仿真。

二、详细设计多路选择器,如下图所示:门b1和b2的延迟如下所示:最小值典型值最大值上升延迟 1 2 3下降延迟 3 4 5关断延迟 5 6 7用三个输入端in1,in2,s,一个输出端out,其功能是实现一个二选一多路选择器。

用s来控制输出。

用下面的输入——输出关系表对其功能进行验证:In0 In1 s Out0 1 1 10 1 0 01 0 1 01 0 0 11 0 1 0三、仿真结果四、调试情况,设计技巧及体会通过本次实验我学会了从门级抽象的角度来设计电路,同时练习了所学的词法约定和语法结构、模块以及端口。

学会自己独立使用verilog语言对实际硬件建模。

并学会了如何设计激励,尽可能把在容易出现的错误找出来地方改变激励信号,在五、源程序清单module mux2(out, in1, in0,s);output out;input in0,in1,s;bufif0 #(1:2:3,3:4:5,5:6:7) b1(out,in0,s);bufif1 #(1:2:3,3:4:5,5:6:7) b2(out,in1,s);endmodulemodule t_mux2;reg IN1,IN0,S;wire OUT;mux2 s1(OUT,IN1,IN0,S);initialbeginIN0= 0;IN1= 1;S= 1;#10 S= 0;#10 S= 1;IN0= 1;IN1= 0;S= 1;#10 S= 0;#10 S= 1;endinitial$monitor($time,"IN0= %b,IN1= %b,S= %b,OUT= %b\n",IN0,IN1,S,OUT); endmodule。

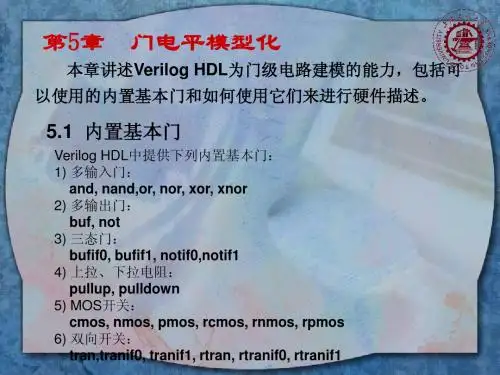

中文版Verilog HDL简明教程:第5章门电平模型本章讲述Verilog HDL为门级电路建模的能力,包括可以使用的内置基本门和如何使用它们来进行硬件描述。

5.1 内置基本门Verilog HDL中提供下列内置基本门:1) 多输入门:and, nand,or, nor,xor,xnor2) 多输出门:buf, not3) 三态门:bufif0, bufif1, notif0,notif14) 上拉、下拉电阻:pullup, pulldown5) MOS开关:cmos, nmos, pmos, rcmos, rnmos, rpmos6) 双向开关:tran,tranif0, tranif1, rtran, rtranif0, rtranif1门级逻辑设计描述中可使用具体的门实例语句。

下面是简单的门实例语句的格式。

gate_type[instance_name] (term1, term2, . . . ,termN);注意,instance_name是可选的;gate_type为前面列出的某种门类型。

各term用于表示与门的输入/输出端口相连的线网或寄存器。

同一门类型的多个实例能够在一个结构形式中定义。

语法如下:gate_type[instance_name1] (term11, term12, . . .,term1N),[instance_name2] (term21, term22, . . .,term2N),. . .[instance_nameM] (termM1, termM2, . . .,termMN);5.2 多输入门内置的多输入门如下:and nand nor or xor xnor这些逻辑门只有单个输出,1个或多个输入。

多输入门实例语句的语法如下:multiple_input_gate_type[instance_name] (OutputA, Input1, Input2, . . .,InputN);第一个端口是输出,其它端口是输入。

门级建模门级建模是指调用Verilog内部自定义的基本门元件(或者用户自定义基本元件)来对硬件电路进行结构描述门级建模方式采用的是一种特殊的模块调用方式。

此时所调用的模块式Verilog内部预先定义好的基本门级元件或者用户自定义的基本元件,在这种建模方式下硬件电路将被描述成由一组基本门级元件的实例组成。

内置基本门级元件Verilog HDL内含的基本门级元件有14中,包括and(与门)、nand(与非门)、or(或门)、nor(或非门)、xor(异或门)、xnor(异或非门)、buf(缓冲器)、not(非门)、bufif1(高电平使能缓冲器)、bufif0(低电平使能缓冲器)、notif1(高电平使能非门)、notif0(低电平使能非门)、pullup(上拉电阻)、pulldown(下拉电阻)基本门级元件的调用其语法格式为:<门级元件名><驱动强度说明>#(<门级延时量>)<实例名>(端口连接表);对上述格式做如下说明:•<门级元件名>:就是前面列出的Verilog HDL内含的14种基本门级元件类型中的任意一种,它用于指明被当前模块调用的是哪一种门级基本元件。

•<驱动强度说明>:这一项是可选项,它的格式为:(<对高电平的驱动强度>,<对低电平的驱动强度>)<驱动强度说明>用来对本次基本门级元件调用所引用的门级元件实例的输出端驱动能力加以说明。

这是因为:在结构建模方式下,一条连线可能会由多个前级输出端同时驱动,该连线最终的逻辑状态将取决于各个驱动端的不同驱动能力,因此有必要对元件实例的输出驱动能力进行说明。

对于门级元件,驱动强度分为对高电平(逻辑1)的驱动强度和对低电平(逻辑0)的驱动强度,因此<驱动强度说明>部分由<对高电平的驱动强度>和<对低电平的驱动强度>这两种成分组成。

第五章门级建模本章学习目标学习Verilog 提供的门级原语提供的门级原语。

理解门的实例引用理解门的实例引用、、门的符号以及and/or ,buf/not 类型的门的真值表类型的门的真值表。

学习如何根据电路的逻辑图来生成Verilog 描述描述。

讲述门级设计中的上升讲述门级设计中的上升、、下降和关断延迟下降和关断延迟。

解释门级设计中的最小解释门级设计中的最小、、最大和典型延迟最大和典型延迟。

5.1 门的类型——与门/或门):以二输出为例):语言中常用的门包括如下几种((以二输出为例Verilog语言中常用的门包括如下几种与门函数与门函数““and”and gate_name ( output, input1, .., inputn);gate_type gatename (A1, … , An, F);与非门函数与非门函数““nand”nand gate_name ( output, input1, .., inputn); 门级模型或门函数或门函数““or”or gate_name ( output, input1, .., inputn);或非门函数或非门函数““nor”nor gate_name ( output, input1, .., inputn); 非门函数非门函数““not”not gate_name ( output, input);5.1 门的类型——与门/或门的引用在Verilog 语言中语言中,,我们可以调用我们可以调用((实例引用实例引用))这些逻辑门来构造逻辑电路构造逻辑电路。

在门的实例引用中在门的实例引用中,,输入端口的数目可以超过两个两个,,这时只需将输入端口全部排列在端口列表中即可这时只需将输入端口全部排列在端口列表中即可,,Verilog 会根据输入端口的数目自动选择引用合适的逻辑门会根据输入端口的数目自动选择引用合适的逻辑门。

注意注意,,在门级原语实例引用的时候在门级原语实例引用的时候,,我们可以不指定具体实例的名字的名字,,这一点为设计师编写需要实例引用几百个门的模块提供了方便供了方便。

门级建模门级建模是指调用Verilog内部自定义的基本门元件(或者用户自定义基本元件)来对硬件电路进行结构描述门级建模方式采用的是一种特殊的模块调用方式。

此时所调用的模块式Verilog内部预先定义好的基本门级元件或者用户自定义的基本元件,在这种建模方式下硬件电路将被描述成由一组基本门级元件的实例组成。

内置基本门级元件Verilog HDL内含的基本门级元件有14中,包括and(与门)、nand(与非门)、or(或门)、nor(或非门)、xor(异或门)、xnor(异或非门)、buf(缓冲器)、not(非门)、bufif1(高电平使能缓冲器)、bufif0(低电平使能缓冲器)、notif1(高电平使能非门)、notif0(低电平使能非门)、pullup(上拉电阻)、pulldown(下拉电阻)基本门级元件的调用其语法格式为:<门级元件名><驱动强度说明>#(<门级延时量>)<实例名>(端口连接表);对上述格式做如下说明:•<门级元件名>:就是前面列出的Verilog HDL内含的14种基本门级元件类型中的任意一种,它用于指明被当前模块调用的是哪一种门级基本元件。

•<驱动强度说明>:这一项是可选项,它的格式为:(<对高电平的驱动强度>,<对低电平的驱动强度>)<驱动强度说明>用来对本次基本门级元件调用所引用的门级元件实例的输出端驱动能力加以说明。

这是因为:在结构建模方式下,一条连线可能会由多个前级输出端同时驱动,该连线最终的逻辑状态将取决于各个驱动端的不同驱动能力,因此有必要对元件实例的输出驱动能力进行说明。

对于门级元件,驱动强度分为对高电平(逻辑1)的驱动强度和对低电平(逻辑0)的驱动强度,因此<驱动强度说明>部分由<对高电平的驱动强度>和<对低电平的驱动强度>这两种成分组成。

其中的每一种驱动强度成分可以是supply、strong、pull、weak和highz中的某一个等级。

因此有如下关键字出现在<驱动强度说明>中:Supply1 strong1 pull1 weak1 highz1Supply0 strong0 pull0 weak0 highz0上面第一行中表示<对高电平的驱动强度>的五个等级,第二行中表示<对低电平的驱动强度>的五个等级。

在基本门级元件实例语句的<驱动强度说明>中,<对高电平的驱动强度>和<对低电平的驱动强度>这两个成分在括号内的前后位置可以互换,比如:and(strong0,weak1) AND_1(out,in1,in2);and(weak1,strong0) AND_2(out,in1,in2);其中引入了两个与门实例AND_1和AND_2。

这两个实例拥有相同的输出端驱动强度,高电平输出强度为weak,低电平输出强度为strong。

如果基本门级元件实例语句中的<驱动强度说明>部分被省略,则默认的驱动强度为(strong0,strong1)。

•#(<门级延时量>):这一项也可以是默认的,它说明了信号从门级元件实例的输入端流动到输出端时所经历的延迟时间长度。

其中<门级延时量>是由若干个延时值组成的,当它只包含一个延时值时,其外部的圆括号可以省略。

请读者注意:上述门级元件实例的门级延时量进行指定的方式与前面讲述的对模块参数值进行修改的第一种方式(使用带有参数值的模块实例语句)是相似的。

这两种情况下,对应的实例语句中都出现了“#<数量值>”部分。

该部分内容在模块实例语句中代表模块参数的新参数值;而在门级实例语句中则代表了门级元件实例输入输出端口间的门级延时量。

在进行模块调用时不能采用像门级元件调用那样的方式指定延时量(只能利用specify块结构来指定延时量);而在进行基本门级元件调用时又不能像模块调用那样对参数值进行修改(只有用户自定义元件才能有参数值)•<实例名>:是为本次元件调用后生成的门级元件实例所取的第一个名称。

与进行模块调用的情况不同,在进行基本门级元件调用时,<实例名>可以省略。

在默认<实例名>的情况下,Verilog编译系统将自动以“<元件名><实例序号>”的形式为门级元件实例取名•(端口连接表):与模块实例语句中的端口连接表类似,但是在进行基本门级元件调用时只能采用端口位置关联方式。

而且与基本门级元件实例各个端口相连的信号端子只能是宽度为一位的表达式或变量标识符多输入门内置多输入门包括6种门级元件:and、nand、or、nor、xor、xnor。

其格式为:<门级元件名>(<输出端口>,<输入端口1>,<输入端口2>,……,<输入端口n>)其中的<门级元件名>就是上面给出的六种多输入门名称之一,在端口列表中出现的第一个端口是输出端口,其后是多个输入端口。

这六种门的真值表为:AND 0 1 X Z0 0 0 0 01 0 1 x ZX 0 x x zZ 0 x x xNAND 0 1 X Z0 1 1 1 11 1 0 x XX 1 X x xZ 1 X x xOR 0 1 X Z0 0 1 x X1 1 1 1 1X X 1 X XZ X 1 X XNOR 0 1 X Z0 1 0 X X1 0 0 0 0X X 0 X XZ X 0 X XXOR 0 1 X Z0 0 1 X X1 1 0 X XX X X X XZ X X X XXOR 0 1 X Z0 1 0 X X1 0 1 X XX X X X XZ X X X X对多输入门进行调用的元件实例语句将采用如下形式:<多输入门元件名><驱动强度说明>#(<门级延时量>)<延时量>(<输出信号端子>,<输入信号端子1>,<输入信号端子2>,…….,<输入信号端子n>);在上述元件实例语句格式中,与多输入门元件输出端相连的外部信号端子(即<输出信号端子>)必须出现在端口连接表的第一项中,与多输入门的各个输入端相连的外部信号端子则只能出现在端口连接表的后面几项内。

这些输入信号端子将以此与多输入门的各个输入端相连。

信号端子和元件端口之间的连接关系是采用“端口位置关联方式“来确定。

多输出门内置多输出门包括两种门级元件:buf和not。

这两种逻辑门的共同特点是:允许有多个输出,但只能有一个输入。

这两种多输出门的元件模型可以表示为:<门级元件名>(<输出端口1>,<输出端口2>,……,<输出端口n>,……,<输入端口>)其中,<门级元件名>是元件名称buf和not之一;端口列表中的最后一项是输入端口,前面的其余端口为输出端口。

它们的真值表如下:<多输出门元件名><驱动强度说明>#(<门级延时量>)<实例名>(<输出信号端子1>,<输出信号端子2>,……,<输出信号端子n>,<输入信号端子>);上述格式中,端口连接表中出现的最后一个信号端子将被连接到多输出门的输入端,而排在前面的其余信号端子将与多输出门的各个输出端依次相连。

信号端子和元件端口之间的连接关系是采用“端口位置关联方式”来确定的。

三态门内置三态门包括四种元件:bufif0、bufif1、notif0和notif1。

这四种逻辑门用来对三态驱动器建模,它们都有一个数据输出端。

一个数据输入端和一个控制输入端。

这几种三态门的特点是:它们的数据输出可以实现三态输出。

其元件模型可以表示为:<门级元件名>(<数据输出端口>,<数据输入端口>,<控制输入端口>)其中,<门级元件名>是前面给出的四种元件名称bufif0、bufif1、notif0和notif1之一;端口列表中的第一项是<数据输出端口>,第二项是<数据输入端口>,最后一项是<控制输入端口>。

它们的真值表为:真值表中有些项是不确定的,比如“0/z”表示输出状态既可以是0也可以是高阻态。

调用三态门的元件实例语句如下:<元件名><驱动强度说明>#(<门级延时量>)<实例名>(<输出信号端子>,<输入信号端子>,<控制信号端子>);上拉、下拉电阻上拉、下拉电阻包括两种元件:pullup和pulldown。

上拉电阻和下拉电阻这两种门级元件都只有一个输出端口而没有输入端口。

上拉电阻将置为1,下拉电阻将输出置为0.。

其调用的语法格式如下:<元件名><驱动强度说明><实例名>(<输出信号端子>);上述格式中,端口连接表内只能出现一个信号端子(输出信号端子),该信号端子将被连接到元件实例的输出端口。

由于上拉电阻只能输出逻辑状态1,下拉电阻只能输出逻辑状态0,所以在进行驱动强度说明时(在需要进行说明的情况下),对pullup元件只需指出对高电平的驱动强度,而对pulldown元件则只需指出对低电平的驱动强度。

下面两条语句就分别对上拉电阻和下拉电阻进行了调用。

Pullup (supply1) U1(power);Pulldown (pull0) U2(gnd);其中,第一条语句引入了上拉电阻的一个实例U1,该实例的输出端被连接到信号端子power;该输出端的驱动高强度为supply1。

第二句,仿照可以分析,此处不再赘述。

门级延时的说明门级延时反映的是信号变化从门级元件的任一输入端口流动到任一输出端口所经历的传输延时。

门级延时可以分为如下几类。

•上升延时:表示信号从“0”、“x”或“z”状态变化到“1”状态时受到的门传输延时。

•下降延时:表示信号从“1”、“x”或“z”状态变化到“0”状态时受到的门传输延时。

•截止延时:表示信号从“0”、“x”或“1”状态变化到“z”状态时受到的门传输延时。

•到不定态的延时:表示信号从“0”、“1”或“z”状态变化到“x”状态时受到的门传输延时。

由于多输入门(and、nand、or、nor、xor、xnor)以及多输入门(buf、not)的输出不可能是高阻态“z”,所以多输入门和多输出门这两类元件没有“截止延时”这类门级延时;对于三态门(bufif0、bufif1、notif0、notif1),这类元件具有全部的四种门级延时;对于上拉电阻和下拉电阻,这类元件不存在任何形式的门级延时。