第十章_卷积码

- 格式:ppt

- 大小:2.02 MB

- 文档页数:34

信息论与编码--卷积码(掌握利用编码电路求生成矩阵和监督矩阵)差错控制编码系统中除了使用分组码之外,另一类广泛应用的称为卷积码,在分组码的编码和译码过程中,每个码字的监督元只与本码字的信息元有关,而与其它码字的信息元无关,即分组码的编码器是一个无记忆的逻辑电路。

但是,卷积码的编码过程中,本码字的监督元不仅与本码字的信息元有关,而且与前m 个码字的信息元有关,因此卷积码的编码器是一个有记忆的时序电路。

卷积码由于更充分地利用码字之间的相关性,可以减少码字长度,简化编译码电路,并得到较好的差错控制性能,因此卷积码在通信领域,特别是卫星通信,空间通信领域得到广泛的应用。

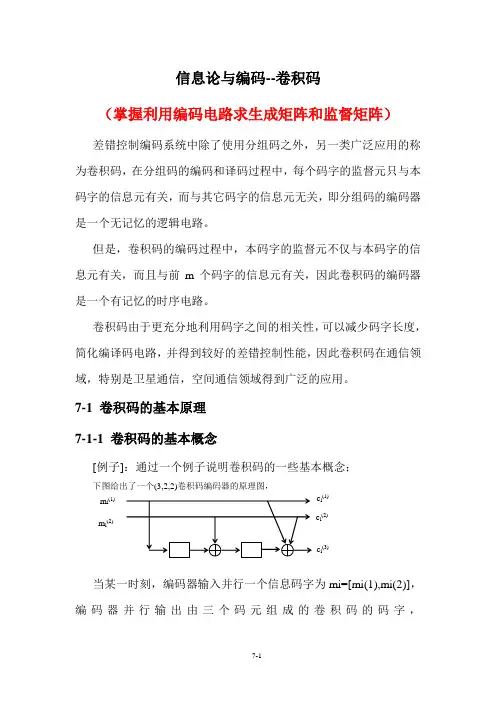

7-1 卷积码的基本原理 7-1-1 卷积码的基本概念[例子]:通过一个例子说明卷积码的一些基本概念;下图给出了一个(3,2,2)卷积码编码器的原理图,当某一时刻,编码器输入并行一个信息码字为mi=[mi(1),mi(2)],编码器并行输出由三个码元组成的卷积码的码字,c i (1)c (1)c i (2) c i (3)m i (1) m i (2)[ci]=[ci(1),ci(2),ci(3)]=[mi(1),mi(2),pi]。

[ci]称为一个码字。

mi 为信息元,pi 为监督元。

可以看出卷积码的输入输出关系为:ci(1)=mi(1) ci(2)=mi(2)ci(3)=mi(1)+mi(2)+mi-1(2)+mi-2(1)可见,卷积码当前输出的码字的监督元不仅与当前输入的信息元有关而且还与前2个码元有关。

这时编码器由2级移位寄存器构成。

定义:卷积码字中码元的个数为n0,码字中信息元个数为k0,由m 级移位寄存器构成的编码器称m 为编码码字约束长度。

有的教材称m’=m+1为约束长度,(m+1)n0为编码码元约束长度。

卷积码记为(n0,k0,m)。

定义:R=k0/n0为码率(Code rate)。

它是表示卷积码的编码效率。

卷积码的编码器的一般形式为:看以下卷积码的约束关系图:在译码时,译码在ci 时要利用到ci-1,ci-2,同时译码字ci+1,ci+2时还要利用到ci 。

引言卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。

在编码过程中,卷积码充分利用了各码字间的相关性。

在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。

而且卷积码在实现最佳译码方面也较分组码容易。

因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。

对其进行研究有很大的现实意义。

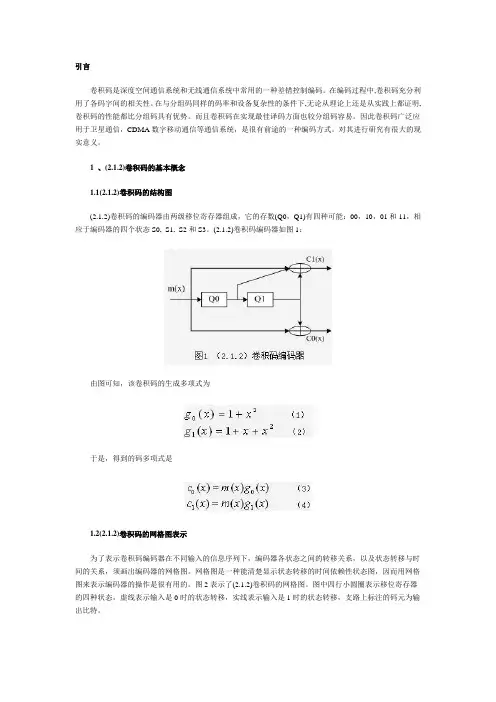

1 、(2.1.2)卷积码的基本概念1.1(2.1.2)卷积码的结构图(2.1.2)卷积码的编码器由两级移位寄存器组成,它的存数(Q0,Q1)有四种可能:00,10,01和11,相应于编码器的四个状态S0, S1, S2和S3。

(2.1.2)卷积码编码器如图1:由图可知,该卷积码的生成多项式为于是,得到的码多项式是1.2(2.1.2)卷积码的网格图表示为了表示卷积码编码器在不同输入的信息序列下,编码器各状态之间的转移关系,以及状态转移与时间的关系,须画出编码器的网格图。

网格图是一种能清楚显示状态转移的时间依赖性状态图,因而用网格图来表示编码器的操作是很有用的。

图2表示了(2.1.2)卷积码的网格图。

图中四行小圆圈表示移位寄存器的四种状态,虚线表示输入是0时的状态转移,实线表示输入是1时的状态转移,支路上标注的码元为输出比特。

2 、(2.1.2)卷积码编码器的编程实现与仿真波形由以上分析可以发现,(2.1.2)编码器由两个模二加法器组成,分别生成、。

而此时输出的是并行数据,须经过并串转换才能输出,在用VHDL编程时,用LOAD和CLK来控制信息的输入与卷积码的产生,当LOAD为底电平时,在每个CLK的上升沿输入一位信息,并进行异或运算;当LOAD为高电平时,在CLK 的上升沿时刻,把生成的卷积码经过并串转换之后输出。

经过编译调试之后,仿真波形如图3:图中,D-IN为输入的信息位,D-OUT为输出的串行卷积码,Q为移位寄存器的内容。

卷积码的基本原理卷积码的基本原理1. 引言•卷积码是一种常用于通信系统中的纠错编码技术。

•它通过引入冗余信息,可以在信道传输过程中检测出并纠正部分错误。

2. 卷积码的定义•卷积码是一种线性的、时间变化的编码方式。

•它可以将输入比特序列转换为输出比特序列,并满足一定的性质。

3. 编码过程•卷积码的编码过程可以用一个状态图表示。

•输入比特依次通过编码器的不同路径,生成输出比特序列。

4. 编码器结构•卷积码的编码器由若干个寄存器和逻辑门组成。

•每个寄存器存储一个状态,逻辑门用于生成输出比特。

5. 纠错能力•卷积码的纠错能力通过其约束长度和码距来衡量。

•约束长度表示编码器中寄存器的数量。

•码距表示卷积码能够检测和纠正的最大错误比特数量。

6. Viterbi解码算法•Viterbi解码算法是一种常用于卷积码解码的算法。

•它通过动态规划的方式寻找最可能的输入比特序列。

7. 进一步研究•卷积码是一个广泛研究的领域,有很多相关的扩展和改进算法。

•感兴趣的读者可以深入研究卷积码的不同应用和改进算法。

以上是针对“卷积码的基本原理”的简要介绍和解释。

卷积码作为一种常用的纠错编码技术,可以在信道传输过程中提高系统的可靠性。

同时,关于卷积码的编码结构、纠错能力和解码算法等方面也有很多相关的研究和应用。

对卷积码感兴趣的读者可以继续深入学习和了解。

8. 卷积码的应用•卷积码在通信领域中有着广泛的应用。

•它可以用于数字电视的信号传输,提高传输质量和可靠性。

•在无线通信系统中,卷积码可以提高信号的抗干扰能力。

•在存储系统中,卷积码也可以用于数据的纠错和恢复。

9. 卷积码的性质•卷积码具有良好的线性性质。

•通过矩阵表示可以更形象地描述卷积码的性质和特点。

•矩阵形式的表示方便进行编码和解码运算。

10. 卷积码的误码性能•误码性能是衡量卷积码性能的重要指标之一。

•通过误码率曲线可以评估卷积码在不同信噪比条件下的性能。

•在设计卷积码时,可以根据需要选择适当的编码率和约束长度,以达到所需的误码性能。

卷积码的基本原理引言卷积码是一种线性纠错码,广泛应用于数字通信和存储系统中。

它通过对数据进行编码,增加冗余信息,以提高数据传输的可靠性。

在接收端,卷积码通过解码算法可以检测和纠正传输过程中引入的错误。

1. 编码过程卷积码的编码过程可以看作是一个滑动窗口对输入数据进行运算的过程。

设输入序列为x[n],输出序列为y[n],编码器有K个输入(信息)比特和N个输出(编码)比特。

首先,将输入序列x[n]按照一个固定的时间窗口长度分组,并将分组后的每一组与一个固定的生成多项式进行卷积运算。

生成多项式由编码器的结构决定。

例如,对于一个3输入2输出(记作(3,2))的卷积编码器,生成多项式可以表示为:G(D)=1+D2+D3。

接下来,将每一组运算结果连接起来得到输出序列y[n]。

2. 状态机在理解卷积编码原理时,需要引入状态机的概念。

状态机描述了编码器内部状态之间的转移关系。

对于一个(K,N)的卷积编码器,其状态机包含2K个状态,每个状态对应一个输出比特的编码过程。

以(3,2)卷积编码器为例,其状态机如下图所示:stateDiagram-v2[*] --> 00/0000/00 --> 01/01: 000/00 --> 10/10: 101/01 --> 11/11: 001/01 --> 00/10: 110/10 --> 00/11: 010/10 --> 11/01: 111/11 --> 10/00: 011/11 --> 01/00: 1上图中,每个状态用两个比特表示,例如00表示当前状态为0。

箭头上的数字表示输入比特,例如从00到01的箭头上标注的数字为0。

状态转移矩阵和输出矩阵根据生成多项式和状态机的关系,可以得到一个状态转移矩阵和一个输出矩阵。

这两个矩阵是描述卷积编码器行为的重要工具。

对于一个(K,N)卷积编码器,其状态转移矩阵是一个2K×K的二进制矩阵,用来描述状态之间的转移关系。