74LS138详解

- 格式:doc

- 大小:245.00 KB

- 文档页数:4

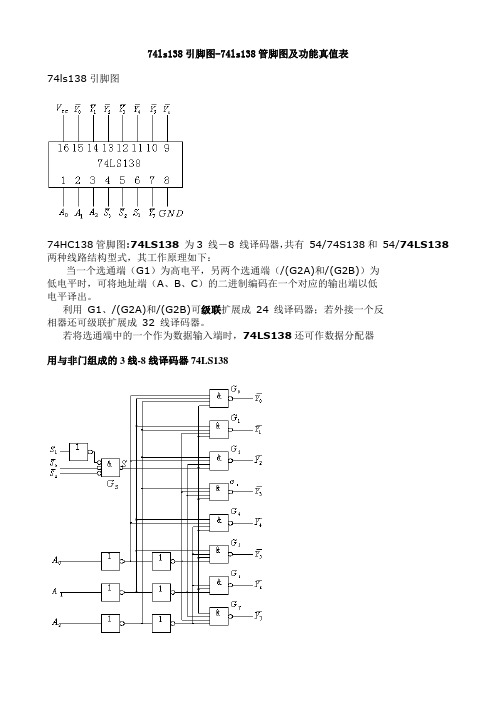

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

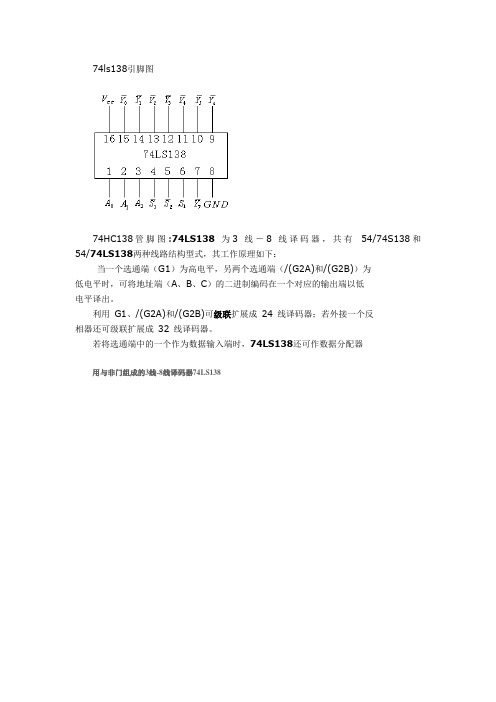

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

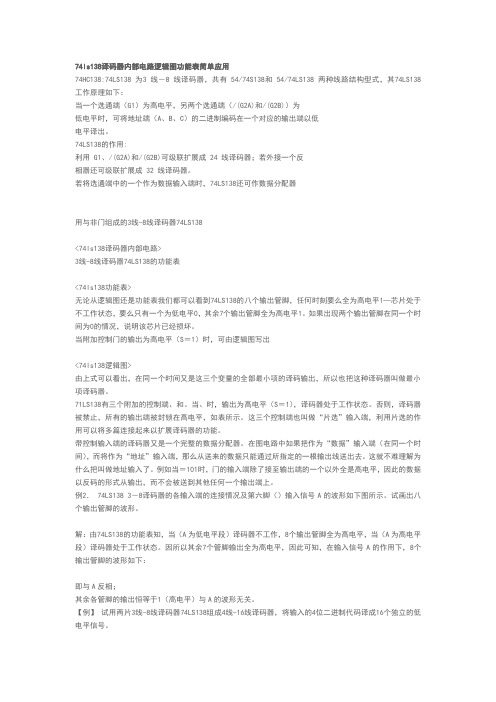

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

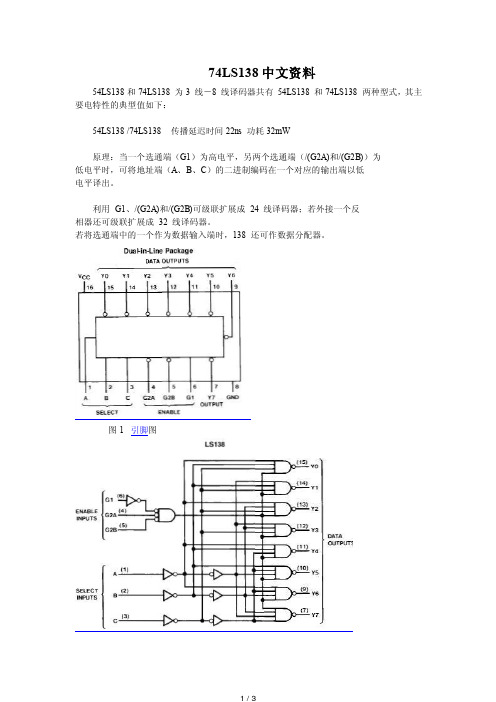

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

74LS138中文资料时间:2009-03-29 11:44:29 来源:资料室作者:编号:4081 更新日期20110604 144057 54LS138和74LS138 为3 线-8 线译码器Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号54LS138 /74LS138 传播延迟时间22ns 功耗32mWDwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号电平译出。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号相器还可级联扩展成32 线译码器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图1 引脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图2 内部逻辑管脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号引脚功能:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号A、B、C 译码地址输入端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号G1 选通端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号/(G2A)、/(G2B) 选通端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Y0~Y7 译码输出端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号真值表:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html。

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74L S1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74LS138的使用实验

一、实验目的及原理

(一)实验目的:

1.加深理解用门电路组成的译码器器的工作原理。

2.学习利用给定的器件设计、调试组合逻辑电路的方法掌握译码器的功能测试方法及应用

(二)实验原理:

1、74LS138译码器简介

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。

变量译码一般是一种较少输入变为较多输出的器件,一般分为2n译码和8421BCD码译码两类。

显示译码主要解决二进制数显示成对应的十、或十六进制数的转换功能,一般其可分为驱动LED和驱动LCD两类。

译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。

把代码状态的特定含义“翻译”出来的过程叫做译码,实现译码操作的电路称为译码器。

或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

根据需要,输出信号可以是脉冲,也可以是高电平或者低电平。

本实验中所用的译码器为变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线—4线、3线—8线和4线—16线译码器。

以3线—译码器74LS138为例进行分析。

74LS138逻辑图及引脚排列

74LS138有3个附加的控制端G1、G2B、G2A。

当G1=1、G2B+G2A=0时,译码器处于工作状态。

否则译码器被禁止,所有的输出端被锁在高

电平。

它的逻辑图如下图所示:

2、常用的显示器件工作原理

在数字系统中常见的数码显示器通常有:发光二极管数码管(LED数码管)和液晶显示数码管(LCD数码管)两种。

发光二极管数码管是用发光二极管构成显示数码的笔划来显示数字,由于发二极管会发光,故LED数码管适用于各种场合。

液晶显示数码管是利用液晶材料在交变电压的作用下晶体材料会吸收光线,而没有交变电场作用下有笔划不会听吸光,这样就可以来显示数码,但由于液晶材料须有光时才能使用,故不能用于无外界光的场合(现在便携式电脑的液晶显示器是用背光灯的作用下可以在夜间使用),但液晶显示器有一个最大的优点就是耗电相当节省,所以广泛使用于小型计算器等小型设备的数码显示。

本实验中使用发光二级管作为输出显示器件,以检测74LS138芯片的输出信号,通过观察发光二级管的亮暗来判断输出信号电平的高低。

二、实验步骤

1.阅读教材中有关译码器的内容。

了解译码器74LS138的工作原理和逻辑关系。

2.画好译码器的原理图,登陆服务器,选择数电实验,在左侧可选器件栏里

选择所需的器件(74LS138芯片、布尔常数输出信号

、led灯、双通道示波器)鼠标双击期间放大或缩小调整合适,选择正确的端口,鼠标单击自动布线,同时画好安装所需的元器件布置及布线图,参考下图。

实验原理图

实验场景图

3、参考原理图接线并保存场景,输出端接发光二级管指示灯和双通道示波器,运行场景,电路连通,输入不同的逻辑信号,通过观察二极管发光情况及示波器信号输出电平的高低,判断74LS138芯片的逻辑原理,记录表格。

4. 用3-8线译码器74LS138和最少的门电路设计一个奇偶校验电路,要求当输入的四个变量中有偶数个1时输出1,否则为0,输出端接LED指示灯,及

双通道示波器,以便检查输出结果。

4 结果返回与波形显示

三、注意事项:

1.试验中输出由led灯判断

2.输入信号由布尔常数信号代替

3.按照实验原理图搭建完成,经检验无误后才可运行,否则内存溢出无法正常得到结果

4.示波器输出参考:

示波器高电平输出

示波器低电平输出。