EDA技术及应用—Verilog HDL版(第三版) (6)

- 格式:ppt

- 大小:899.00 KB

- 文档页数:52

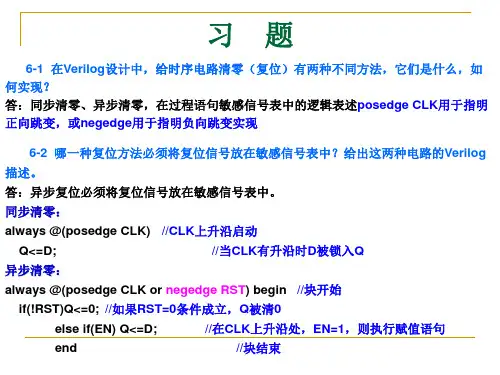

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

第3章硬件描述语言Verilog HDL EDA应用技术EDA应用技术3.1 引言3.1 引言内容概要3.1 引言 3.1 引言3.1 引言形式化地表示电路的行为和结构;3.2 Verilog HDL基本结构内容概要3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构[例3.2.5¾Verilog HDLendmodule声明语句中。

模块是可以进行层次嵌套的。

3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构Verilog3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构Verilog3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构HDL语言描述的“东西”都通过其名字来识别,3.2 Verilog HDL基本结构六、编写Verilog3.2 Verilog HDL基本结构1语汇代码的编写标准3.2 Verilog HDL基本结构1语汇代码的编写标准(续)3.2 Verilog HDL基本结构2综合代码的编写标准3.2 Verilog HDL基本结构(6)描述组合逻辑的always块,一定不能有不完全赋值,即所有输出变2综合代码的编写标准(续1)3.2 Verilog HDL基本结构(10)避免生成不想要的触发器。

2综合代码的编写标准(续2)3.2 Verilog HDL基本结构2综合代码的编写标准(续3)3.2 Verilog HDL基本结构2综合代码的编写标准(续4)3.3 数据类型及常量、变量内容概要3.3 数据类型及常量、变量一、数据类型3.3 数据类型及常量、变量(1)3.3 数据类型及常量、变量8’b1001xxxx8’b1010zzzz3.3 数据类型及常量、变量(3)3.3 数据类型及常量、变量3.3 数据类型及常量、变量(4)parameter常量(符号常量)3.3 数据类型及常量、变量 3.3 数据类型及常量、变量:利用特殊符号“#”3.3 数据类型及常量、变量3.3 数据类型及常量、变量三、变量1. nets型变量定义——输出始终随输入的变化而变化的变量。

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

EDA技术及应用第三版教学设计简介在目前快速发展的电子领域中,EDA(Electronic Design Automation,电子设计自动化)技术早已成为不可或缺的一环。

EDA技术主要包括从原理图设计开始一直到制卡和封装的全过程,是电子设计领域中近年来发展最快的技术之一。

通过本教学设计,旨在使学生掌握EDA基本原理,熟悉其常用工具与软件,了解EDA的应用领域及其趋势,为培养电子设计人才提供帮助。

教学内容第一章 EDA简介1.1 EDA的概述1.2 EDA的发展历程1.3 EDA在电子技术中的作用第二章 EDA基础原理2.1 EDA工具体系结构2.2 EDA中的计算机辅助设计2.3 EDA中的电路仿真与分析第三章 EDA工具与软件3.1 EDA工具介绍3.2 常用EDA软件及其应用第四章 EDA的应用领域4.1 EDA在电子产品设计中的应用4.2 EDA在通信设备中的应用4.3 EDA在汽车电子领域中的应用4.4 EDA在医疗器械中的应用第五章 EDA的未来趋势5.1 EDA的趋势与发展5.2 EDA技术的未来发展方向教学方法本教学设计采用优先使用案例、实验和练习的方式,将概念和理论知识应用于实际问题中。

同时,将以小组案例研究、课堂交流和讨论的方式,促进学生之间和教师之间的交流和互动。

评估方式本课程采用察看作业进展情况、小组案例分析和课堂讨论的方式对学生进行评估。

其中,作业每占总成绩的20%、案例分析与讨论每占30%。

参考文献•Alvin R. Lebeck. (2020), EDA技术及应用第三版, 人民邮电出版社, ISBN:978-7-115-55493-2•Stephen A. Thomas. (2017), EDA技术: 从基础入门到应用, 电子工业出版社, ISBN:978-7-121-32143-2结语EDA技术的发展已经推动了现代电子技术的进步,对于学习EDA的学生来说,了解基础原理和应用领域是至关重要的。

数字电路(第3版)Verilog HDL代码【P21】module com1(a,b,c,f);input a,b,c;output f;assign f = (~a & ~b & c)|(~a & b & c)|(a & b & ~c)|(a & b & c); endmodule【P42】举重裁判电路module JZ(Y,A,B,C);output Y;input A,B,C;assign Y =(A&&B)||(A&&C);endmodule【P102】8线-3线优先编码器module encoder(din,dout);input [7:0] din;output reg[2:0] dout;always @(din)beginif (!din[7]) dout = 3'b000;else if (!din[6]) dout = 3'b001;else if (!din[5]) dout = 3'b010;else if (!din[4]) dout = 3'b011;else if (!din[3]) dout = 3'b100;else if (!din[2]) dout = 3'b101;else if (!din[1]) dout = 3'b110;else dout = 3'b111;endendmodule【P109】3线-8线译码器module decoder3_8(A2,A1,A0,Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0);input A2,A1,A0;output Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0; //低电平有效assign Y0 = !(!A2 && !A1 && !A0);assign Y1 = !(!A2 && !A1 && A0);assign Y2 = !(!A2 && A1 && !A0);assign Y3 = !(!A2 && A1 && A0);assign Y4 = !(A2 && !A1 && !A0);assign Y5 = !(A2 && !A1 && A0);assign Y6 = !(A2 && A1 && !A0);assign Y7 = !(A2 && A1 && A0); Endmodulemodule encoder(din,dout);input [7:0] din;output reg[2:0] dout;always @(din)beginif (!din[7]) dout = 3'b000;else if (!din[6]) dout = 3'b001;else if (!din[5]) dout = 3'b010;else if (!din[4]) dout = 3'b011;else if (!din[3]) dout = 3'b100;else if (!din[2]) dout = 3'b101;else if (!din[1]) dout = 3'b110;else dout = 3'b111; endendmodule【P110】7段显示译码器ModuleLED7S(DIN,Y);input[3:0] DIN;output[6:0] Y;reg[6:0] Y;always @(DIN)begincase(DIN)4'b0000: Y= 7'b0111111;4'b0001: Y = 7'b0000110;4'b0010: Y = 7'b1011011;4'b0011: Y = 7'b1001111;4'b0100: Y = 7'b1100110;4'b0101: Y = 7'b1101101;4'b0110: Y = 7'b1111101;4'b0111: Y = 7'b0000111;4'b1000: Y = 7'b1111111;4'b1001: Y = 7'b1101111;4'b1010: Y = 7'b1110111;4'b1011: Y = 7'b1111100;4'b1100: Y = 7'b0111001;4'b1101: Y = 7'b1011110;4'b1110: Y = 7'b1111001;4'b1111: Y = 7'b1110001;default: Y = 7'b0000000;endcaseendendmodule【P114】4选1数据选择器(1)利用case语句module MUX41(d0,d1,d2,d3,SEL,Y);output Y;input d0,d1,d2,d3;input [1:0] SEL;reg Y;always@(A,B,C,D,SEL)case (SEL)2'b00:Y=d0;2'b01:Y=d1;2'b10:Y=d2;2'b11:Y=d3;default:Y=2'bx;endcaseendmodule(2)利用if语句module MUX41B(d0,d1,d2,d3,SEL,Y); output Y;input d0,d1,d2,d3;input [1:0] SEL;reg Y;always@(d0,d1,d2,d3,SEL)beginif (SEL==2'b00)Y=d0;else if(SEL==2'b01)Y=d1;else if(SEL==2'b10)Y=d2;elseY=d3;endendmodule【P116】4位数值比较器module compare4bit(A,B,AEQB,AGTB,ALTB); input[3:0] A,B;output AEQB,AGTB,ALTB;assign AEQB = (A==B);assign AGTB = (A>B);assign ALTB = (A<B);endmodule【P120】4位加法器module add4b(A,B,CIN,S,COUT);input[3:0] A;input[3:0] B;input CIN;output[3:0] S;output COUT;wire[4:0] CRLT;assign CRLT = {1'b0,A} + {1'b0,B} + {4'b0000,CIN};assign S = CRLT[3:0];assign COUT = CRLT[4];endmodule【P136】高有效的rs触发器module rs ( R, S, Q, QN );input R, S;output Q, QN;reg Q;//寄存器定义assign QN = ~Q;//assign语句,QB=/Q?always @( R,S )//在CLK的上跳沿,执行以下语句。