成本,减小系统的体积等,从而对系统的集成度不断提出更高

的要求。

➢ 高性能的EDA工具得到长足的发展,其自动化和智能化程度

不断提高,为嵌入式系统设计提供了功能强大的开发环境。

➢ 计算机硬件平台性能大幅度提高,为复杂的SoC设计提供了

物理基础。

ppt课件

10

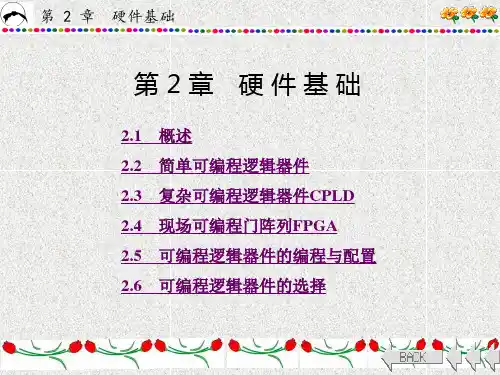

ASIC及其设计流程

ASIC(Application Specific Integrated Circuits,专用集成电路) 是相对于通用集成电路而 言的,ASIC主要指用于某 一专门用途的集成电路器 件。ASIC分类大致可分为 数字ASIC、模拟ASIC和数 模混合ASIC。

ppt课件

8

2.科研方面主要利用电路仿真工具(EWB或PSPICE)进行电 路设计与仿真;利用虚拟仪器进行产品测试;将CPLD/FPGA器 件实际应用到仪器设备中;从事PCB设计和ASIC设计等。

在产品设计与制造方面,包括前期的计算机仿真,产品开发 中的EDA工具应用、系统级模拟及测试环境的仿真,生产流水线 的EDA技术应用、产品测试等各个环节。如PCB的制作、电子设 备的研制与生产、电路板的焊接、ASIC的流片过程等。

ppt课件

3

1.2 EDA技术发展

●EDA(Electronic Design Automation) ●EDA:是指以计算机为工作平台,融合应用

电子技术、计算机技术、智能化技而研制成 的电子CAD(Computer Aided Design)通用软 件包。

●功能:辅助IC(integrated circuit)设计,电子电 路设计,PCB(Printed Circuit Board)设计

ASIC设计方法

全定制法

半定制法