硬件信号质量SI测试规范

- 格式:docx

- 大小:1.11 MB

- 文档页数:51

硬件测试规范硬件测试规范目录1. 目的 (3)2. 适用范围 (3)3. 定义 (3)4. 测试工作职责 (4)5. 测试流程 (5)6. 测试阶段 (6)6.1 单元测试 (7)6.1.1测试对象 (7)6.1.2具体要求 (8)6.1.3进入准则 (9)6.1.4主要内容 (9)6.1.5退出准则 (10)6.1.6应提交的文档 (10)6.2 集成测试 (10)6.2.1测试对象 (10)6.2.2具体要求 (11)6.2.3进入准则 (11)6.2.4主要内容 (11)6.2.5退出准则 (12)6.2.6应提交的文档 (13)6.3 确认测试........... 错误!未定义书签。

6.3.1测试对象 ......... 错误!未定义书签。

6.3.2具体要求 ......... 错误!未定义书签。

6.3.3进入准则 ......... 错误!未定义书签。

6.3.4主要内容 ......... 错误!未定义书签。

6.3.5退出准则 ......... 错误!未定义书签。

6.3.6确认测试应提交的文档.. 错误!未定义书签。

6.4 系统测试 (13)6.4.1测试对象 (13)6.4.2具体要求 (14)6.4.3进入准则 (14)6.4.4主要内容 (14)6.4.5退出准则 (15)6.4.6应提交的文档 (15)7. 测试用例的选择...... 错误!未定义书签。

7.1设计测试用例的基本原则.. 错误!未定义书签。

7.2设计测试用例的方法.. 错误!未定义书签。

7.3测试用例的说明 ..... 错误!未定义书签。

8. 对缺陷的管理........ 错误!未定义书签。

8.1对缺陷(BUG)的定义 .. 错误!未定义书签。

8.2对缺陷(BUG)的管理 .. 错误!未定义书签。

1. 目的在策略和方法上说明计划、管理测试活动,指导测试进行,以发现硬件的错误,验证硬件是否满足系统需求说明书和硬件设计说明书。

硬件测试规范This model paper was revised by the Standardization Office on December 10, 2020硬件测试规范目录1. 目的在策略和方法上说明计划、管理测试活动,指导测试进行,以发现硬件的错误,验证硬件是否满足系统需求说明书和硬件设计说明书。

2. 适用范围适用于所有硬件产品的各个测试阶段。

读者是所有的硬件测试人员及与测试相关的人员。

3. 定义4. 测试工作职责测试的目标是:发现问题、改进问题,总结经验,起到保证硬件设计达到设计要求的作用。

单板开发组负责单板测试过程的组织和实施,同时为硬件系统测试提供配合和支持,具体包括实施完成单板测试计划和测试方法文档、进行单板测试、完成单板测试报告,交付单板硬件,配合硬件系统测试。

硬件系统开发组负责硬件系统测试过程的组织和实施,同时为硬件平台系统测试提供配合和支持,具体包括实施完成硬件测试计划和测试方法文档、进行硬件系统测试、完成硬件测试报告,交付硬件系统。

测试组负责整个硬件平台系统测试过程的组织和实施,实施完成硬件平台系统测试和交付测试,单板软件组配合硬件平台测试工作。

具体包括完成硬件平台测试计划和测试方法文档、进行硬件平台系统测试、完成硬件平台测试报告。

5. 测试流程测试需求在项目启动时给予说明。

测试开始时,应该完成测试计划。

测试开始后,由于测试情况有变化,可能导致测试计划文档内容的变化。

如果文档内容有明显变化,必须在文档中添加变更历史来记载这些变化。

单板测试、硬件系统测试、硬件平台系统测试以及测试的其它阶段,均涉及如下活动:a.测试计划:对测试方法和资源的分配进行计划,参见《测试计划》模板;b.测试设计和开发:详细描述各个测试阶段的测试方法,特别是测试信号的设计,参见《测试方法说明》,搭建测试环境;c.测试执行:按照测试计划执行测试过程,决定测试项目是通过/失败;d.测试报告:记录测试结果和测试问题,参见《测试报告》模板;e.测试评估:按照测试标准评价测试系统。

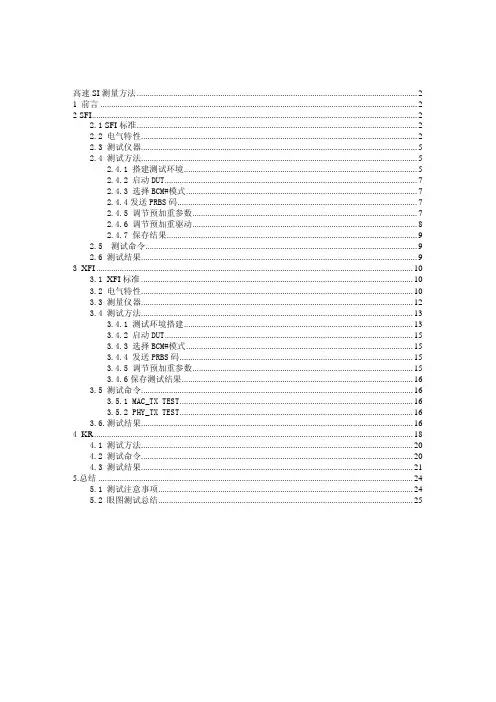

高速SI测量方法 (2)1 前言 (2)2 SFI (2)2.1 SFI标准 (2)2.2 电气特性 (2)2.3 测试仪器 (5)2.4 测试方法 (5)2.4.1 搭建测试环境 (5)2.4.2 启动DUT (7)2.4.3 选择BCM#模式 (7)2.4.4发送PRBS码 (7)2.4.5 调节预加重参数 (7)2.4.6 调节预加重驱动 (8)2.4.7 保存结果 (9)2.5 测试命令 (9)2.6 测试结果 (9)3 XFI (10)3.1 XFI标准 (10)3.2 电气特性 (10)3.3 测量仪器 (12)3.4 测试方法 (13)3.4.1 测试环境搭建 (13)3.4.2 启动DUT (15)3.4.3 选择BCM#模式 (15)3.4.4 发送PRBS码 (15)3.4.5 调节预加重参数 (15)3.4.6保存测试结果 (16)3.5 测试命令 (16)3.5.1 MAC_TX TEST (16)3.5.2 PHY_TX TEST (16)3.6.测试结果 (16)4 KR (18)4.1 测试方法 (20)4.2 测试命令 (20)4.3 测试结果 (21)5.总结 (24)5.1 测试注意事项 (24)5.2 眼图测试总结 (25)高速SI测量方法1 前言在速率达到10Gbps 高速设计中,尽管我们在电路设计上按照标准设计,但在信号的传输过程仍不可避免会受到串扰等的影响,由此我们需要去做信号完整性分析,以验证我们设计的正确性,而眼图是一种可对数字信号传输作定性分析的有效手段。

以下所介绍就是关于10G信号接口SFI、XFI、KR的SI测量方法。

2 SFI2.1 SFI标准SFF-8431定义了SFI的电气特性及测试方法。

2.2 电气特性在SFF-8431中SFI被定义了以下三种模型:①Host SystemFigure1---Host Compliance Board②ASIC/SerDesFigure 2---ASIC/SerDes Test Board③ModuleFigure 3---Module Compliance Board以上三种模型对应的定义了如下测试点:Figure 4---SFI Reference Points而在我们的设计应用中,我们需要验证IC的transmitter和receiver 的信号经过SFP+ Module connector后的信号质量.而ASIC/SerDes和Module模型分别定义对ASIC和Module本身的电气特性,并未考虑信号经过connector的情况,与我们的实际应用不符。

信号完整性测试规范和工作流程一、信号完整性测试规范1.测试范围:信号完整性测试应涵盖全部重要信号线,包括时钟信号、数据信号、控制信号、电源供应线等。

2.测试参数:测试参数包括但不限于信号功率、上升时间、下降时间、峰值电压、峰峰值电压、幅度稳定性、时序稳定性等。

3.测试方法:根据具体测试需求和设备条件,选择合适的信号完整性测试方法,如步进响应测试、脉冲响应测试、频率响应测试、时钟提前测试等。

4.测试设备:测试设备需要具备高精度、高速度、高带宽等特点,如示波器、信号发生器、信号注入器、信号线探针、信号整形器等。

5.测试环境:测试环境应符合实际应用场景,包括温度、湿度、电磁干扰等因素的考虑。

6.数据分析:对测试数据进行详细的分析和处理,包括波形展示、数据比对、波形参数提取、异常识别等。

7.测试标准:根据不同行业和应用领域,制定相应的信号完整性测试标准,如IEEE、IPC、JEDEC等,以确保测试结果的准确性和可靠性。

8.测试报告:根据测试结果生成详细的测试报告,包括测试方法、测试步骤、测试数据、异常情况分析、改进建议等。

二、信号完整性测试工作流程1.确定测试目标:根据设计需求和系统规格,确定需要测试的信号线和测试参数。

2.设计测试方案:根据测试目标和测试需求,设计相应的测试方案,包括测试方法、测试设备、测试环境等。

3.准备测试设备:根据测试方案,准备好所需的测试设备,确保其良好状态和准确性能。

4.连接测试回路:将被测试的电路板、电线、接插件等与测试设备连接起来,确保信号传输通畅。

5.设置测试参数:根据测试目标和测试方案,设置测试设备的相应参数,如示波器的触发电平、采样率、带宽等。

6.执行信号完整性测试:根据测试方案,执行信号完整性测试,记录测试数据和波形。

7.数据分析和处理:对测试数据进行详细分析和处理,包括波形展示、参数提取、异常识别等。

8.测试结果评估:根据测试数据和标准要求,对测试结果进行评估,确定是否合格。

信号质量测试规范本规范修改记录:目录1引言 (6)2适用范围 (6)3信号质量测试概述 (6)3.1信号完整性 (6)3.2信号质量 (7)4信号质量测试条件 (12)4.1单板/系统工作条件: (12)4.2信号质量测试人员要求: (12)4.3示波器选择与使用要求: (12)4.4探头选择与使用要求 (13)4.5测试点的选择 (14)5信号质量测试通用标准 (14)5.1信号电平简述: (14)5.2合格标准 (15)5.3信号质量测试结果分析注意事项 (17)6信号质量测试方法 (19)6.1电源信号质量测试 (19)6.1.1简述 (19)6.1.2测试项目 (19)6.1.3测试方法 (19)6.2时钟信号质量测试 (26)6.2.1简述 (26)6.2.2测试方法 (26)6.2.3测试指标与合格标准 (26)6.2.4注意事项 (28)6.3复位信号质量测试 (29)6.3.1简述 (29)6.3.2测试方法 (29)6.3.3测试项目与合格标准 (29)6.3.4注意事项 (31)6.3.5测试示例 (31)6.4数据、地址信号质量测试 (33)6.4.1简述 (33)6.4.2测试方法 (33)6.4.3测试项目 (34)6.4.4测试示例: (34)6.5差分信号质量测试 (36)6.5.1简述 (36)6.5.2测试项目 (36)6.5.3测试方法 (36)6.5.4合格标准 (38)6.5.5注意事项 (41)6.5.6测试示例 (41)6.6串行信号质量测试 (43)6.6.1概述 (43)6.6.2测试项目 (44)6.6.3测试方法 (45)6.6.4合格标准 (46)7信号质量测试CHECKLIST (49)8测试系统接地说明 (51)9引用标准和参考资料 (54)信号质量测试规范关键词:信号完整性、测试摘要:本规范详细说明了单板信号质量测试的方法。

其中包括各类信号波形参数的定义,进行信号质量测试的条件,覆盖范围,合格标准,信号分类,各类信号波形参数的指标,测试点的选择以及测试结果分析重点。

icpms si指标

ICP-MS(电感耦合等离子体质谱)中的Si 指标通常指的是硅元素的检测性能。

以下是一些可能与ICP-MS 中Si 指标相关的方面:1. 检测限:ICP-MS 可以测量硅元素的最低浓度,通常以ng/L 或ppb 表示。

2. 线性动态范围:ICP-MS 能够准确测量硅元素的浓度范围,通常以几个数量级表示。

3. 干扰:ICP-MS 可能会受到来自其他元素的干扰,特别是在测量硅元素时。

因此,评估Si 指标时需要考虑干扰的影响,并采取适当的校正措施。

4. 精度和准确度:ICP-MS 测量硅元素的精度和准确度也是重要的指标,可以通过分析标准物质或与其他可靠方法进行比较来评估。

需要注意的是,具体的Si 指标可能会因ICP-MS 仪器的型号、操作条件和分析方法而有所不同。

在实际应用中,应根据具体需求和实验条件选择合适的ICP-MS 仪器和分析方法,并参考仪器制造商提供的规格和性能指标。

硬件信号质量SI测试规范初识SI测试SI信号完整性(Signal Integrity)测试是在设计过程中使用的方法,用于测量信号在电路板或器件上的运行状况。

硬件信号质量SI测试是关于硬件电路的信号质量、时钟频率等性能指标的测试。

直观来说,SI测试是用来测试硬件信号的质量好坏,它可以检验硬件产品在复杂环境下所产生的电磁干扰、衰减、相位偏移等信号问题。

SI测试可以应用于多类硬件设备,包括计算机服务器、路由器、交换机、移动终端设备、自动驾驶汽车和其他高速信号传输的硬件设备。

SI测试内容SI测试的内容可以包括以下方面:信号完整性测量通过SI测试,可以测量信号的质量,例如电压、阻抗、反射系数、传输延迟、噪声等因素。

协议分析在不同的硬件设备中,采用的协议类型不同,例如高速串口协议(USB、SATA、PCIe)协议、以太网协议等。

通过协议分析,可以更好地评估硬件设备的通信质量。

EMI/EMC测试电磁干扰(EMI)测试和电磁兼容性(EMC)测试,是一些硬件设备必须通过的测试,通过这个测试可以评估设备的电磁性能,例如电磁干扰抗性、放射性等。

SI测试过程SI测试包含以下步骤:硬件设计要求和规格说明在进行硬件设计时,其中最重要的一个环节就是设计要求和规格说明。

这个环节主要是考虑设计需求和目标,例如每个信号的最大传输速率、延迟、阻抗控制等。

SI测试建模建立数学模型,以预测电路板或器件中的信号完整性。

在这个过程中,包括建立传输线模型、建立布局模型、计算电磁丢失和干扰等。

硬件SI测试硬件SI测试是采用测试仪器进行的。

测试仪器需要支持各种测量方法和协议类型。

常用的测试方法有:同步时钟测试同步时钟测试一般用于高速传输的硬件设备,例如PCIe、DDR、PCI、SDRAM等。

测试流程要求如下:1.选择测试仪器和信号源。

2.设置测试参数,例如时钟频率、电平、电流和电压等。

3.通过测试仪器读取信号。

4.评估结果并记录数据。

非同步时钟测试非同步时钟测试一般用于串行通信硬件设备,例如以太网、USB、PCIe等。

SI---Signal Integrity 信号完整性PI---Power Integrity 电源完整性emc---electromagnetic compatibility 电磁兼容rf --radio frequency 射频emc=emi+emsEMI(电磁辐射)=传导干扰(conduction)+辐射干扰(emission)SI: 由傅立叶变换可看出,信号上升越快, 高次谐波的幅度越大, MAXWELL方程组看知,这些交流高次谐波会在临近的线上产生交变电流. 甚至通过空间寄生电容直接辐射到另外的导体,所以这些高次谐波就是造成辐射干扰(emission)的主要因素; (说的简单点,就是信号上升越快,信号越完整,信号品质越好,但是对于emi不好)PI: PCB上存在数字\\模拟区域, 高频\\低频区域等不同的区域和平面, 如果分割不当则很容易相互干扰, 即传导干扰(conduction).电源完整性之APSIM-SPI 篇在PCB设计中,高速电路的布局布线和质量分析无疑是工程师们讨论的焦点。

尤其是如今的电路工作频率越来越高,例如一般的数字信号处理(DSP)电路板应用频率在150-200MHz是很常见的,CPU板在实际应用中达到500MHz以上已经不足为奇,在通信行业中Ghz 电路的设计已经十分普及。

所有这些PCB板的设计,往往是采用多层板技术来实现。

在多层板设计中不可避免地为采用电源层的设计技术。

而在电源层设计中,往往由于多种类的电源混合应用而使得设计变为十分复杂。

那么萦绕在PCB工程师中的难题有哪些?PCB的层数如何定义?包括采用多少层?各个层的内容如何安排最合理?如应该有几层地,信号层和地层如何交替排列等等。

如何设计多种类的电源分块系统?如3.3V, 2.5V, 5V, 12V 等等。

电源层的合理分割和共地问题是PCB是否稳定的一个十分重要的因素。

如何设计去耦电容?利用去耦电容来消除开关噪声是常用的手段,但如何确定其电容量?电容放置在什么位置?什么时候采用什么类型的电容等等。

目录1. 目的......................................................... - 3 -2. 适用范围..................................................... - 3 -3. 定义......................................................... - 3 -4. 测试工作职责................................................. - 3 -5. 测试流程..................................................... - 3 -6. 测试阶段..................................................... - 4 -6.1 单板测试.................................................... - 4 -6.1.1测试对象.................................................. - 4 -6.1.2具体要求.................................................. - 4 -6.1.3进入准则.................................................. - 5 -6.1.4主要内容.................................................. - 5 -6.1.5退出准则.................................................. - 5 -6.1.6应提交的文档.............................................. - 5 -6.2 硬件系统测试................................................ - 5 -6.2.1测试对象.................................................. - 5 -6.2.2具体要求.................................................. - 5 -6.2.3进入准则.................................................. - 6 -6.2.4主要内容.................................................. - 6 -6.2.5退出准则.................................................. - 6 -6.2.6应提交的文档.............................................. - 6 -6.3硬件平台系统测试............................................ - 6 -6.3.1测试对象.................................................. - 6 -6.3.2具体要求.................................................. - 7 -6.3.3进入准则.................................................. - 7 -6.3.4主要内容.................................................. - 7 -6.3.5退出准则.................................................. - 7 -6.3.6应提交的文档.............................................. - 7 -1. 目的在策略和方法上说明计划、管理测试活动,指导测试进行,以发现产品的错误,验证是否满足系统需求说明书和设计说明书。

信号质量测试规范本规范修改记录:目录1引言 (6)2适用范围 (6)3信号质量测试概述 (6)3.1信号完整性 (6)3.2信号质量 (7)4信号质量测试条件 (12)4.1单板/系统工作条件: (12)4.2信号质量测试人员要求: (12)4.3示波器选择与使用要求: (12)4.4探头选择与使用要求 (13)4.5测试点的选择 (14)5信号质量测试通用标准 (14)5.1信号电平简述: (14)5.2合格标准 (15)5.3信号质量测试结果分析注意事项 (17)6信号质量测试方法 (19)6.1电源信号质量测试 (19)6.1.1简述 (19)6.1.2测试项目 (19)6.1.3测试方法 (19)6.2时钟信号质量测试 (26)6.2.1简述 (26)6.2.2测试方法 (26)6.2.3测试指标与合格标准 (26)6.2.4注意事项 (28)6.3复位信号质量测试 (29)6.3.1简述 (29)6.3.2测试方法 (29)6.3.3测试项目与合格标准 (29)6.3.4注意事项 (31)6.3.5测试示例 (31)6.4数据、地址信号质量测试 (33)6.4.1简述 (33)6.4.2测试方法 (33)6.4.3测试项目 (34)6.4.4测试示例: (34)6.5差分信号质量测试 (36)6.5.1简述 (36)6.5.2测试项目 (36)6.5.3测试方法 (36)6.5.4合格标准 (38)6.5.5注意事项 (41)6.5.6测试示例 (41)6.6串行信号质量测试 (43)6.6.1概述 (43)6.6.2测试项目 (44)6.6.3测试方法 (45)6.6.4合格标准 (46)7信号质量测试CHECKLIST (49)8测试系统接地说明 (51)9引用标准和参考资料 (54)信号质量测试规范关键词:信号完整性、测试摘要:本规范详细说明了单板信号质量测试的方法。

其中包括各类信号波形参数的定义,进行信号质量测试的条件,覆盖范围,合格标准,信号分类,各类信号波形参数的指标,测试点的选择以及测试结果分析重点。

信号完整性测试介绍目录CONTENTS 1•信号完整性SI2•信号完整性测试内容3•信号完整性测试条件•信号完整性测试标准45•信号完整性问题总结一、信号完整性SI信号完整性SI(Signal Integrity):是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。

如果电路系统中信号能够以要求的时序,持续时间和电压幅度到达IC,则该电路系统具有较好的信号完整性。

反之,当传输的信号不能被IC正常响应时,就出现了信号完整性问题。

SI解决的是信号传输过程中的质量问题,尤其是在高速领域,数字信号的传输不能只考虑逻辑上的实现,物理实现中数字器件开关行为的模拟效果往往成为设计成败的关键。

理想数字信号波形实际数字信号波形(模拟量)SI 解决的问题 反射串扰过冲振铃地弹 时序 EMC在数字电路系统中,信号以逻辑“0”或“1”的方式从一个器件传输到另外一个器件,信号到底是“0”还是“1”,一般来说它们都是有一个参考电平。

在接收端的输入门里面,如果信号的电压超过高电平参考电压Vih,则该信号被识别为高逻辑;如果信号的电压低于低电平的参考电压Vil,则该信号就被识别为低逻辑。

如下图所示为一个理想信号经传输线后的接收端实际接收的信号理想数字信号接收端实际数字信号问题图形原因分析备注电平没有到达逻辑电平负载过重传输线过长电平不匹配驱动速度慢上冲/下冲高速、大电流驱动阻抗未匹配电感量过大其它相邻信号串扰典型的信号完整性问题及其产生的原因分析问题图形原因分析备注振铃(不单调)电感量过大阻抗不匹配延时错误负载过重传输线过长驱动速度慢二、信号完整性测试内容1 信号(SI)测试内容2 电源(SI)测试内容三、信号完整性测试条件1 单板/系统工作条件单板/系统工作在室温条件(20℃~27℃)单板/系统要可靠接地单板/系统上电正常工作,各模块工作均正常,30分钟后再开始测试单板/系统在轻载及满载情况下均应测试单板/系统电源稳定在额定电压±3%范围内2 测试人员要求<1>.熟悉逻辑电平及信号时序的基本知识,熟练掌握示波器及万用表的使用方法;<2>对单板/系统电路原理有深刻的认识,对信号分类及信号的流向有清楚认识,了解单板/系统上器件的工作原理、工作速度及工作电平;<3>.测试人员在测试操作仪器时必须穿戴防静电服、静电鞋和防静电帽;<4>.在用手持握被测电路板时必须戴防静电手套;<5>.测试人员在不同仪器时必须要按照仪器的具体要求来操作。

硬件测试规范目录1. 目的 ........................................................ - 3 -2. 适用范围 .................................................... - 3 -3. 定义 ........................................................ - 3 -4. 测试工作职责 ................................................ - 4 -5. 测试流程 .................................................... - 4 -6. 测试阶段 .................................................... - 5 - 6.1 单元测试 ................................................... - 5 - 6.1.1测试对象.................................................. - 5 - 6.1.2具体要求.................................................. - 6 - 6.1.3进入准则.................................................. - 6 - 6.1.4主要内容.................................................. - 6 - 6.1.5退出准则.................................................. - 6 - 6.1.6应提交的文档.............................................. - 7 - 6.2 集成测试 ................................................... - 7 - 6.2.1测试对象.................................................. - 7 - 6.2.2具体要求.................................................. - 7 - 6.2.3进入准则.................................................. - 7 - 6.2.4主要内容.................................................. - 7 - 6.2.5退出准则.................................................. - 8 - 6.2.6应提交的文档.............................................. - 8 - 6.3 确认测试 ....................................... 错误!未定义书签。

硬件信号质量SI测试规范目录1引言 (4)2适用范围 (4)3信号质量测试概述 (4)3.1信号完整性 (4)3.2信号质量 (5)4信号质量测试条件 (10)4.1单板/系统工作条件: (10)4.2信号质量测试人员要求: (10)4.3示波器选择与使用要求: (10)4.4探头选择与使用要求 (11)4.5测试点的选择 (12)5信号质量测试通用标准 (12)5.1信号电平简述: (12)5.2合格标准 (13)5.3信号质量测试结果分析注意事项 (15)6信号质量测试方法 (17)6.1电源信号质量测试 (17)6.1.1简述 (17)6.1.2测试项目 (17)6.1.3测试方法 (17)6.2时钟信号质量测试 (24)6.2.1简述 (24)6.2.2测试方法 (24)6.2.3测试指标与合格标准 (24)6.2.4注意事项 (26)6.3复位信号质量测试 (27)6.3.1简述 (27)6.3.2测试方法 (27)6.3.3测试项目与合格标准 (27)6.3.4注意事项 (29)6.3.5测试示例 (29)6.4数据、地址信号质量测试 (31)6.4.1简述 (31)6.4.2测试方法 (31)6.4.3测试项目 (32)6.4.4测试示例: (32)6.5差分信号质量测试 (34)6.5.1简述 (34)6.5.2测试项目 (34)6.5.3测试方法 (34)6.5.4合格标准 (36)6.5.5注意事项 (40)6.5.6测试示例 (40)6.6串行信号质量测试 (41)6.6.1概述 (41)6.6.2测试项目 (42)6.6.3测试方法 (43)6.6.4合格标准 (44)7信号质量测试CHECKLIST (47)8测试系统接地说明 (49)9引用标准和参考资料................................. 错误!未定义书签。

信号质量测试规范关键词:信号完整性、测试摘要:本规范详细说明了单板信号质量测试的方法。

硬件测试规范之五兆芳芳创作目录1. 目的12. 适用规模13. 定义14. 测试任务职责25. 测试流程26. 测试阶段36.1 单元测试36.2 集成测试56.3 确认测试66.4 系统测试87. 测试用例的选择98. 对缺陷的办理98.1对缺陷(BUG)的定义98.2对缺陷(BUG)的办理101. 目的在战略和办法上说明筹划、办理测试勾当,指导测试进行,以发明硬件的错误,验证硬件是否满足系统需求说明书和硬件设计说明书.2. 适用规模适用于所有硬件产品的各个测试阶段.读者是所有的硬件测试人员及与测试相关的人员.3. 定义4. 测试任务职责测试的目标是:发明问题、改良问题,总结经验,起到包管硬件设计达到设计要求的作用.单板开发组担任单板测试进程的组织和实施,同时为硬件系统测试提供配合和支持,具体包含实施完成单板测试筹划和测试办法文档、进行单板测试、完成单板测试陈述,交付单板硬件,配合硬件系统测试.硬件系统开发组担任硬件系统测试进程的组织和实施,同时为硬件平台系统测试提供配合和支持,具体包含实施完成硬件测试筹划和测试办法文档、进行硬件系统测试、完成硬件测试陈述,交付硬件系统.测试组担任整个硬件平台系统测试进程的组织和实施,实施完成硬件平台系统测试和交付测试,单板软件组配合硬件平台测试任务.具体包含完成硬件平台测试筹划和测试办法文档、进行硬件平台系统测试、完成硬件平台测试陈述.5. 测试流程测试需求在项目启动时赐与说明.测试开始时,应该完成测试筹划.测试开始后,由于测试情况有变更,可能导致测试筹划文档内容的变更.如果文档内容有明显变更,必须在文档中添加变动历史来记录这些变更.单板测试、硬件系统测试、硬件平台系统测试以及测试的其它阶段,均涉及如下勾当:a.测试筹划:对测试办法和资源的分派进行筹划,拜见《测试筹划》模板;b.测试设计和开发:详细描述各个测试阶段的测试办法,特别是测试信号的设计,拜见《测试办法说明》,搭建测试情况;c.测试执行:依照测试筹划执行测试进程,决定测试项目是通过/失败;d.测试陈述:记实测试结果和测试问题,拜见《测试陈述》模板;e.测试评估:依照测试尺度评价测试系统.6. 测试阶段测试阶段和硬件开产生命周期的对应关系:6.1单板测试6.每一个板卡的设计和实现.6.(1)测试筹划, 由开发组担任人和开发人员在详细设计阶段进行制定,明确测试规模、测试办法和对测试进度的安插.单板测试筹划中应该明确所有测试项.(2)测试的设计和开发由开发人员进行.(3)如果使用测试东西应在测试筹划中给出,并在测试设计中给出详细说明.(4)测试办法主要采取白盒测试,辅以黑盒测试.(5)测试信号应该按照被测单元的性质而设计.(6)测试项要含盖所有的功效和性能要求.(7)测试出现问题时,开发人员应该协商筹划下一轮测试如何展开.6.(1)已生成《单板测试筹划》、《单板测试办法说明》(2)单板硬件已完成调试.(3)测试设备已准备就绪.6.单板测试在下面几个方面进行查抄:(1)单板结构测试-----检测被测单板的物理尺寸:形状,厚度,器件高度,器件位置,定位孔等.(2)上电,掉电测试-----检测被测单板的上电,掉电时序,冲击电流峰值,电流泻放速率等.(3)时钟信号----检测时钟信号的精度和波形质量.(4)芯片间的接口信号-----检测接口信号时序及波形质量.(5)芯片功效测试----检测芯片功效是否正常.(6)接口信号测试----检测接口信号是否正确.(7)功耗测试----检测最大功耗战争均功耗.(8)性能测试-----检测设计性能.6.(1)单板功效与设计需求一致.(2)单板接口与设计需求一致.(3)单板结构与设计要求一致.(4)功耗与设计要求一致.(5)完成《单板元测试陈述》.6.测试开始时,需要提交的文档:《单板测试筹划》、《单元测试办法说明》.测试结束时,需要生成的文档:《单板测试陈述》,完整的《单板测试办法说明》.6.2硬件系统测试6.由单板组成的模块或子系统.6.(1)测试筹划由项目担任人和主要设计人员在概要设计阶段进行制定.(2)测试的设计和开发由开发人员进行.(3)确认各单板无错误的连接.(4)测试出现问题时,开发人员应该协商筹划下一轮测试如何展开.6.(1)已完成单板测试.(2)已经生成《硬件系统测试筹划》、《硬件系统测试办法说明》.(3)测试模块或子系统已装配完毕.(4)测试设备已就绪.6.(1)结构测试-----检测被测系统的物理尺寸,形状.(2)上电,掉电测试-----检测被测系统各单板的上电,掉电次序,冲击电流峰值,电流泻放速率等.(3)时钟信号----检测板间时钟信号的精度和波形质量.(4)接口信号-----检测板直接口信号时序及波形质量.(5)系统功效测试----检测系统功效是否正常.(6)接口功效测试----检测接口功效是否正确.(7)功耗测试----检测最大功耗战争均功耗.(8)性能测试-----检测设计性能.(9)配置变动测试-----检测系统的各类配置下的功效及性能.(10)稳定性测试-----检测系统的稳定任务能力.6.(1)系统功效及性能与设计需求一致.(2)内,外接口与设计需求一致.(3)结构与设计要求一致.(4)功耗与设计要求一致.(5)配置能力与设计要求一致.(6)完成《单板系统测试陈述》.6.测试开始时,需要提交的文档:《硬件系统测试筹划》、《硬件系统测试办法说明》.测试结束时,需要生成的文档:《硬件系统测试陈述》、完整的《硬件系统测试办法说明》.6.4硬件平台系统测试6.经过集成单板软件的硬件平台系统.6.(1)系统测试筹划由项目担任人在需求阐发阶段进行制定,决定具体哪些方面的测试.(3)系统测试由测试组担任开展,项目开发组赐与配合.6.(1)已完成硬件系统测试.(2)已集成单板软件系统.(2)已经生成《硬件平台系统测试筹划》、《硬件平台系统测试办法说明》(3)测试设备已就绪.(4)测试代码已通过编译..6.硬件平台系统测试是要验证系统是否具备了交付给高层软件使用,是否满足系统需求和功效规格说明书中的要求,一般需要以下几方面的测试:(1)功效测试(2)性能测试(3)强度测试(4)可靠性测试6.(1)完全执行了硬件平台系统测试筹划中的每个测试用例(2)平台系统测试中发明的错误已经得到修改并且通过了测试.(3)完成了《平台系统测试陈述》及相应的《BUG报表》. 6.测试开始时,需要提交的文档:《硬件平台系统测试筹划》、《硬件平台系统测试用例说明》.测试结束时,需要生成的文档:《硬件平台系统测试陈述》、完整的《硬件平台系统测试用例说明》及相应的《BUG报表》.。

目录1引言 (4)2适用范围 (4)3信号质量测试概述 (4)3.1信号完整性 (4)3.2信号质量 (5)4信号质量测试条件 (10)4.1单板/系统工作条件: (10)4.2信号质量测试人员要求: (10)4.3示波器选择与使用要求: (10)4.4探头选择与使用要求 (11)4.5测试点的选择 (12)5信号质量测试通用标准 (12)5.1信号电平简述: (12)5.2合格标准 (13)5.3信号质量测试结果分析注意事项 (15)6信号质量测试方法 (17)6.1电源信号质量测试 (17)6.1.1简述 (17)6.1.2测试项目 (17)6.1.3测试方法 (17)6.2时钟信号质量测试 (24)6.2.1简述 (24)6.2.2测试方法 (24)6.2.3测试指标与合格标准 (24)6.2.4注意事项 (26)6.3复位信号质量测试 (27)6.3.1简述 (27)6.3.2测试方法 (27)6.3.3测试项目与合格标准 (27)6.3.4注意事项 (29)6.3.5测试示例 (29)6.4数据、地址信号质量测试 (31)6.4.1简述 (31)6.4.2测试方法 (31)6.4.3测试项目 (32)6.4.4测试示例: (32)6.5差分信号质量测试 (34)6.5.1简述 (34)6.5.2测试项目 (34)6.5.3测试方法 (34)6.5.4合格标准 (36)6.5.5注意事项 (40)6.5.6测试示例 (40)6.6串行信号质量测试 (41)6.6.1概述 (41)6.6.2测试项目 (42)6.6.3测试方法 (43)6.6.4合格标准 (44)7信号质量测试CHECKLIST (47)8测试系统接地说明 (49)9引用标准和参考资料................................. 错误!未定义书签。

信号质量测试规范关键词:信号完整性、测试摘要:本规范详细说明了单板信号质量测试的方法。

其中包括各类信号波形参数的定义,进行信号质量测试的条件,覆盖范围,合格标准,信号分类,各类信号波形参数的指标,测试点的选择以及测试结果分析重点。

缩略语清单:SI Signal Integrity 信号完整性TTL Transistor-Transistor Logic 晶体管-晶体管逻辑CMOS Complementary Metal Oxide Semicondutor 互补金属氧化物半导体LVTTL Low Voltage TTL 低电压TTLLVCMOS Low Voltage CMOS 低电压CMOSECL Emitter Coupled Logic 发射极耦合逻辑PECL Pseudo/Positive Emitter Coupled Logic 伪发射极耦合逻辑LVDS Low Voltage Differential Signaling 低电压差分信号GTL Gunning Transceiver Logic 射电收发逻辑HSTL High-Speed Transceiver Logic 高速收发器逻辑eHSTL Enhanced High-Speed Transceiver Logic 增强高速收发器逻辑dHSTL Differential HSTL 差分HSTLSSTL Stub Series-terminated Logic 线脚系列终端逻辑SPI Serial Peripheral Interface 串行外围接口I2C Inter Integrated Circuit Bus 内部集成电路总线USB Universal Serial Bus 通用串行总线1引言《信号质量测试规范》是为了规范和指导硬件调试、硬件测试以及生产测试时信号质量测试方法及手段,在总结长期实际工作经验的基础上制定的。

由于某些原因的限制,本规范难免会存在着一些纰漏。

我们实际使用、遵循规范的过程,也是一个检验和完善规范的过程。

希望大家能积极的提出宝贵意见及见解,以保持该规范的的可操作性,推动我司规范性文档的建设进程。

2适用范围本规范作为研发、中试进行信号质量测试的共同标准。

本规范适用所有数字信号的调试、测试过程。

测试时应覆盖各个功能模块,包括电源、时钟、复位电路、CPU最小系统、外部接口(E1、网口、串口等等)、逻辑芯片(CPLD/FPGA)、专用电路等等。

模拟电路由于其信号的连续变化性,不能直接应用本规范,可择情参考。

本文档不包括的内容:非信号质量测试内容。

例如不适用于部分硬件接口指标测试,系统硬件规格测试、环境测试、EMC测试、安规测试、防护测试、振动测试等。

3信号质量测试概述3.1 信号完整性现在的高速数字系统的时钟频率可能高达数百兆Hz,其快斜率瞬变和极高的工作频率,以及很大的电路密集度,必将使得系统表现出与低速设计截然不同的行为,出现了信号完整性问题。

破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而造成系统误工作甚至导致系统崩溃。

因此,信号完整性问题已经越来越引起高速数字电路设计人员的关注。

如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。

反之,当信号不能正常响应时,就出现了信号完整性问题。

SI(Signal Integrity)解决的是信号传输过程中的质量问题,尤其是在高速领域,数字信号的传输不能只考虑逻辑上的实现,物理实现中数字器件开关行为的模拟效果往往成为设计成败的关键。

3.2 信号质量常见的信号质量问题表现在下面几个方面:1)过冲类型正过冲负过冲图例危害1、闩锁损伤器件(>V CC/V DD),对器件冲击造成器件损坏;2、形成干扰源,对其它器件造成串扰。

1、闩锁损伤器件(< V EE/GND),对器件冲击造成器件损坏;2、管脚上的负电压可能使器件PN衬底(寄生二极管)前向偏置,流过的大电流大于1安时,熔断键丝产生开路。

产生原因1、其它相邻信号串扰;2、器件驱动能力太强;3、没有匹配或者匹配不当。

解决建议1、PCB布线避开干扰源和耦合路径;2、增加电阻匹配,参考做法是始端串电阻或者末端并阻抗(电阻),减少过冲。

备注闩锁:关于闩锁的概念可以参考《数字电路》这一类教材。

现在由于厂家工艺改进,闩锁问题基本上可以得到规避。

但是长时间的信号过冲会使得器件失效率增加(尤其是负过冲)。

2)毛刺(噪声)类型正向毛刺负向毛刺图例容易造成控制信号控制错误或时钟信号相位发生错误:危害1)数据线上的毛刺如果被采样到,可能造成判断结果错误;2)边沿触发的器件中,时钟线上的毛刺可能会使得采样到多余的数据(相当于多了一拍时钟)。

产生原因1)PCB走线串扰(例如数据线和时钟线并行走线较长,信号线放置在晶振等干扰源附近);2)外界干扰,如地线噪声等;3)逻辑出现竞争、冒险;解决建议1)控制器件布局和PCB走线,信号远离干扰源;2)添加去耦电容或输出滤波等。

滤波器件尽量靠近信号管脚;3)逻辑设计中添加冗余项,或者采用同步逻辑设计,避免竞争冒险;备注1)毛刺脉冲带来的问题多发生在器件替代后出现问题;2)如果负向毛刺时始终落在高电平判决门限以上,那么没有什么影响(因为始终会被判断为高电平);如果正向毛刺始终落在低电平判决门限以下,那么没有什么影响(因为始终会被判断为低电平)。

3)回勾(台阶)类型上升沿回勾下降沿回勾图例危害1)主要是时钟类信号上的回勾有危害,可能会使得采样到多余的数据(相当于多了一拍时钟),影响了时钟信号上升沿和下降沿的单调性;2)对于电源信号,上电边沿的回勾可能导致系统死机,需要结合复位信号判断是否可以接受;3)数据信号由于一般是在数据的中间采样,回勾的影响不是很大(除非速率很高,建立保持时间1~2ns,这时需要考虑回勾对数据的影响)。

产生原因匹配不当,信号放射回来形成回勾解决建议增加合适的匹配。

一般来讲,对于单端信号,单板内信号可以加33欧电阻始端匹配,板间信号加200欧电阻匹配较合适。

备注如上面毛刺项的说明,如果回勾始终落在高电平判决门限以上(或者始终落在低电平判决门限以下),那么没有什么影响,因为会被判断为高电平(或低电平)3)信号边沿缓慢类型上升沿缓慢下降沿缓慢图例危害上升、下降沿缓慢发生在数据信号线上(串口信号线,HW信号线等)时,会造成数据采样错误。

产生原因驱动能力不够,或者负载过大(例如链路阻抗太大)解决建议1)提高驱动能力;2)减小负载。

备注由于驱动不足或者负载过大,信号边沿缓慢常常伴随着信号幅度较低现象4)振荡(回冲/振铃)类型回冲振铃图例表现:多次跨越电平临界值。

又称为回冲。

处于V H附近的回冲称为正向回冲,处于V L附近的回冲称为负向回冲表现:经过多次反复才回归正常电平。

又称为振铃。

缺点(危害)类似于多次过冲。

且跨越电平临界值后,在高低电平之间是一种不确定的状态。

在高低电平之间是一种不确定的状态(有可能被判断为0,也可能被判断为1)。

产生原因匹配不当(例如匹配阻抗过大、过小)。

解决建议更改为合适的匹配电阻/阻抗。

备注5)建立、保持时间(Setup time & Hold time)建立保持时间是一个时序的概念。

通常把单板的数字信号分为控制信号、时钟信号、地址信号、数据信号等,时序关系就是这些信号间的相互关系。

判断时序关系主要有两个指标:建立时间和保持时间。

如下图,建立时间就是指在触发器的采样信号(这个采样信号通常是指时钟)有效之前,数据已经稳定不变的时间;而保持时间是指采样信号有效之后数据保持稳定不变的时间。

类型建立时间保持时间图例缺点(危害)建立时间不够,读到的数据会是一个不稳定的数据,可能会采样错误保持时间不够,读写数据处理过程中同样可能读写到错误数据产生原因设计时没有考虑清楚,设计出错。

或者没有考虑到设计容限范围,在某4)产生信号质量问题的其它原因:➢串扰串扰表现为在一根信号线上有信号通过时,在PCB板上与之相邻的信号线上就会感应出相关的信号,我们称之为串扰。

窜扰的表现形式通常是毛刺。

信号线距离地线越近,线间距越大,产生的串扰信号越小。

异步信号和时钟信号更容易产生串扰。

因此解串扰的方法是移开发生串扰的信号或屏蔽被严重干扰的信号。

➢电磁辐射EMI(Electro-Magnetic Interference)即电磁干扰,产生的问题包含过量的电磁辐射及对电磁辐射的敏感性两方面。

EMI表现为当数字系统加电运行时,会对周围环境辐射电磁波,从而干扰周围环境中电子设备的正常工作。

它产生的主要原因是电路工作频率太高以及布局布线不合理。

目前已有进行 EMI仿真的软件工具,但EMI仿真器都很昂贵,仿真参数和边界条件设置又很困难,这将直接影响仿真结果的准确性和实用性。