时钟信号质量测试用例5.6

- 格式:doc

- 大小:50.00 KB

- 文档页数:3

SDH时钟指标时钟功能的测试方法SDH(Synchronous Digital Hierarchy)是一种用于光纤通信的传输技术和协议。

SDH网络中的时钟是非常关键的一个指标,它决定了整个网络系统的正常运行和性能。

一、SDH时钟指标1. 主时钟(Primary Reference Clock,PRC):主时钟是整个SDH网络中的最高级时钟,它通过全球卫星导航系统(GNSS)或其他高精度设备提供。

PRC信号的频率稳定性要求非常高,通常要在正常运行条件下保持一定时间(例如,每24小时的最大误差在1微秒以内)。

2. 一级时钟(Level 1 Clock,LT):一级时钟的频率是由PRC提供的,它必须能够在整个SDH网络中分发同步时钟,并且保持精确的频率稳定性。

3. 二级时钟(Level 2 Clock,LL):二级时钟是从一级时钟派生而来的时钟,它在SDH网络中的传输链路上分发时钟。

二级时钟的频率误差要求比一级时钟高,但要求低于特定的阈值。

4. 三级时钟(Level 3 Clock,L3):三级时钟是在SDH网络中的最低一级时钟,它从二级时钟派生而来,并在SDH网络中的不同设备之间同步时钟。

1.频率稳定性测试:该测试目的是检查时钟的频率稳定性是否满足要求。

可以通过比较时钟信号和基准时钟信号的频率差异来判断频率稳定性。

测试方法包括直接测量频率偏差、频率档差、频率跟踪和频率回损等。

2.相位稳定性测试:该测试目的是检查时钟的相位稳定性是否满足要求。

可以通过比较时钟信号和基准时钟信号的相位差异来判断相位稳定性。

测试方法包括直接测量相位偏差、相位档差和相位跟踪等。

3.时钟分布测试:该测试目的是检查时钟在SDH网络中的传输链路上是否能够正确分发和同步。

可以通过在不同设备之间进行时钟分发和同步测试来判断时钟分布是否正常。

4.脱锁恢复测试:该测试目的是检查时钟在遇到故障情况时是否能够迅速恢复同步状态。

可以通过模拟故障情况,如断开时钟链路、断电等,在故障恢复后检查时钟是否能够迅速恢复同步。

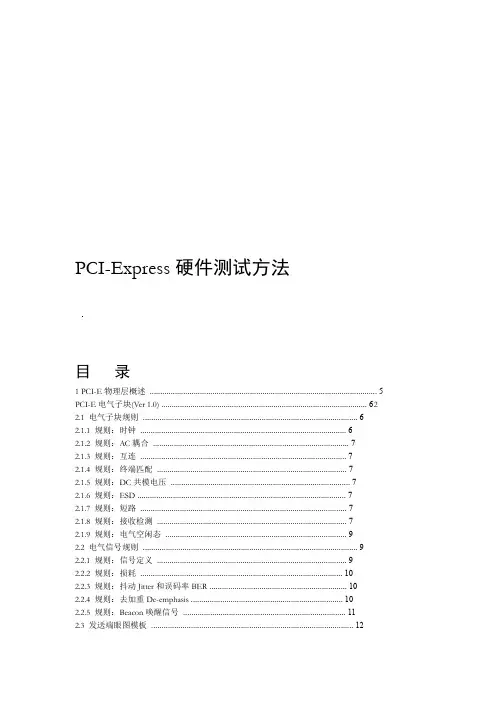

PCI-Express硬件测试方法目录1PCI-E物理层概述 (5)PCI-E电气子块(Ver 1.0) (62)2.1电气子块规则 (6)2.1.1规则:时钟 (6)2.1.2规则:AC耦合 (7)2.1.3规则:互连 (7)2.1.4规则:终端匹配 (7)2.1.5规则:DC共模电压 (7)2.1.6规则:ESD (7)2.1.7规则:短路 (7)2.1.8规则:接收检测 (7)2.1.9规则:电气空闲态 (9)2.2电气信号规则 (9)2.2.1规则:信号定义 (9)2.2.2规则:损耗 (10)2.2.3规则:抖动Jitter和误码率BER (10)2.2.4规则:去加重De-emphasis (10)2.2.5规则:Beacon唤醒信号 (11)2.3发送端眼图模板 (12)接收端眼图模板.2.4 (12)一致性测试负载................................................................................................. 2.5 13 PHY电气测试项目......................................................................................................... 3 13 3.1通用测试项目.. (14)发送端测试项目 3.2 (14)接收端测试项目. 3.3 (16)共页第2, 27页3.4母板测试项目 (17)插卡测试项目..................................................................................................... 13.5 7TEK测试方案简介.4 (18)4.1两个SMA通道连接 (18)一个带4.2SMA输入差分探头P7350SMA测试 (18)两个单端有源探头P72604.3测试 (19)一个差分探头P73xx测试................................................................................... 4.4 195PHY电气测试用例 (20)5.1符合性_PCI-E时钟精度测试 (20)符合性_SSC扩频时钟测试................................................................................ 25.2 0符合性_PCI-E一致性测试 5.3 (21)符合性_PCI-E5.4眼图测试 (23)符合性_PCI-E抖动测试 5.5 (25)符合性_PCI-E通道间偏斜测试......................................................................... 2 5.66符合性_PCI-E插卡功耗测试 5.7 (26)6参考文档......................................................................................... 错误!未定义书签。

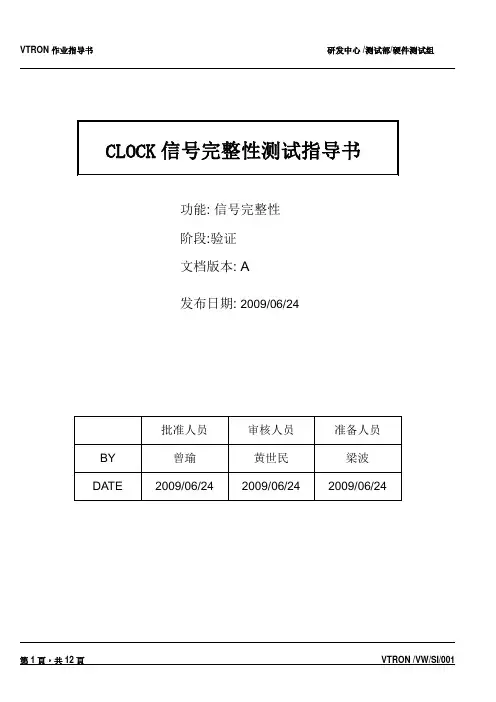

功能: 信号完整性阶段:验证文档版本: A发布日期: 2009/06/24目录1. 目的 (4)2. 适用范围 (4)3. 测量设备 (4)4. 参考文件 (4)5. 注意事项 (4)6.测试项目 (5)7. 操作步骤 (6)※※修订履历※※1. 目的依照规格手册,介绍和规范在测量CLOCK信号时的操作。

2. 适用范围用于VTRON拼墙和IDB产品在做信号完整性量测时的应用。

3. 测量设备Tektronix TDS 3034 Qty=1 Tektronix P6139A Probe Qty=2 4. 参考文件4.1《TDS3034操作手册》4.2 相关测试点位组件的DATASHEET,线路图等。

5. 注意事项5.1 确认测试人员静电环接触良好5.2 在测量时应检查示波器是否运行正常5.3 检查信号连接是否正确,接地是否合理5.4 确定待测系统SUT 是否工作在预定的模式6.测试项目测试参数图示:图一 CLOCK7. 操作步骤6.1 操作前准备6.1.1 执行探头的校正或DSKEW(多通道),确认结果是PASS.6.2 测试流程6.2.1 按下电源开关,开始进入操作接口对于示波器操作接口和基本操作,參考《TDS3034操作手册》。

6.2.2 当完全进入操作接口时,按照测试规范,选择不同的测试探头,将被测信号接到相应的探头上。

6.2.3 让被测试单板进入测试模式:让系统处于工作状态,进行时钟信号测试,完毕后关机退出.所有项目测试参数参考图一所示,此处采用AT91RM9200举例说明,具体测试时依据对应CLOCK芯片规格参数测量。

6.3 信号分类测量6.3.1 CLOCK信号高电平。

在示波器触发菜单选中触发模式为下降沿触发,在AUTO 狀态下尽量向下调整触发电平,使之刚好能触发满足测试要求的相应的波形,调整好Scale,进行single 操作。

预先按下single 按钮,在信号输入端尽量靠近芯片管脚测试,量测结果如下图所示,通过在Measure 菜单选择最大值、最高值测量项对波形进行幅值测量。

时钟fs指标1.引言1.1 概述时钟fs指标是一种用于衡量时钟质量的指标,它是计算机系统中一个非常重要的参数。

正常情况下,我们希望时钟能够稳定地运行,准确地提供时间信息给系统的各个部件。

然而,由于硬件设备的不同、环境的变化以及其他一些因素的干扰,时钟的准确性和稳定性可能会受到影响。

为了评估时钟质量,人们引入了时钟fs指标。

时钟fs指标是一个用于度量时钟稳定性和准确性的综合指标,它考虑了时钟的频率误差和抖动两个方面。

首先,频率误差是指时钟的实际频率与标准频率之间的偏差。

一个好的时钟应该能够以接近标准频率的稳定速率运行。

频率误差越小,表示时钟的稳定性越好。

其次,时钟的抖动指时钟频率在短时间内的波动情况。

即使在时钟频率没有明显偏差的情况下,由于噪声等因素的影响,时钟频率仍然可能会有微小的波动。

抖动的大小可以反映时钟的准确性,抖动越小,表示时钟的准确性越高。

时钟fs指标通过综合考虑频率误差和抖动两个方面,可以全面评估时钟的质量。

一般来说,当时钟fs指标越接近0,表示时钟的质量越高。

时钟fs指标的应用非常广泛。

在计算机系统中,时钟fs指标可以用于评估时钟模块、芯片、以及整个计算机系统的时钟质量。

它对于保证计算机系统的正常运行,提高系统的可靠性和稳定性非常重要。

总之,时钟fs指标是一种用于衡量时钟质量的重要指标,它综合考虑了时钟的频率误差和抖动两个方面,可以评估时钟的稳定性和准确性。

1.2文章结构文章结构是指整篇文章的框架和组织方式,它有助于读者更好地理解和把握文章的内容。

本文的结构主要包括引言、正文和结论三部分。

在引言部分概述了时钟fs指标的背景和重要性,引起了读者的兴趣。

而在本节中,我们将详细说明文章的整体结构。

首先,我们将在正文部分分为两个要点来介绍时钟fs指标。

第一个要点将重点介绍时钟的基本概念和fs指标的定义。

我们将阐述时钟在人类社会中的重要性和应用领域,并对fs指标的计算方法进行详细的解析。

通过具体的例子和数据,我们将给读者清晰地展示时钟fs指标的计算过程和结果。

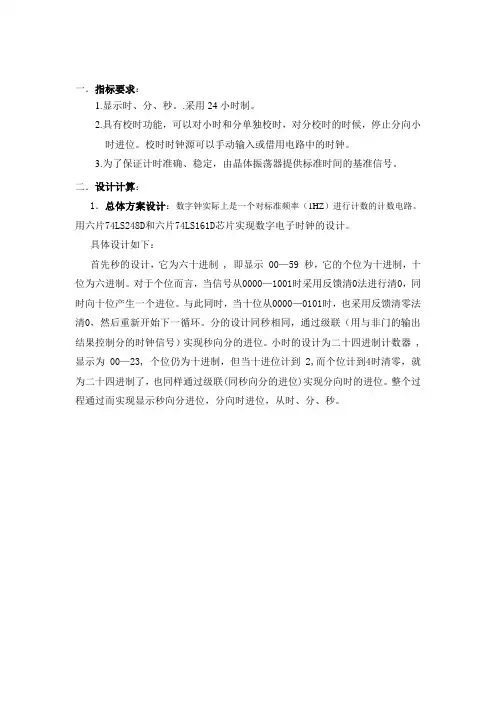

一.指标要求:1.显示时、分、秒。

.采用24小时制。

2.具有校时功能,可以对小时和分单独校时,对分校时的时候,停止分向小时进位。

校时时钟源可以手动输入或借用电路中的时钟。

3.为了保证计时准确、稳定,由晶体振荡器提供标准时间的基准信号。

二.设计计算:1.总体方案设计:数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

用六片74LS248D和六片74LS161D芯片实现数字电子时钟的设计。

具体设计如下:首先秒的设计,它为六十进制 , 即显示 00—59 秒,它的个位为十进制,十位为六进制。

对于个位而言,当信号从0000—1001时采用反馈清0法进行清0,同时向十位产生一个进位。

与此同时,当十位从0000—0101时,也采用反馈清零法清0,然后重新开始下一循环。

分的设计同秒相同,通过级联(用与非门的输出结果控制分的时钟信号)实现秒向分的进位。

小时的设计为二十四进制计数器 ,显示为 00—23, 个位仍为十进制,但当十进位计到 2,而个位计到4时清零,就为二十四进制了,也同样通过级联(同秒向分的进位)实现分向时的进位。

整个过程通过而实现显示秒向分进位,分向时进位,从时、分、秒。

2.单元电路设计:1、秒脉冲发生器数字钟实际上是一个对标准频率(1HZ)迚行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟。

秒脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,本实验为了得到稳定的连续脉冲,我们选用了有极高的频率稳定性的石英晶体多谐振荡器。

采用石英晶体多谐振荡器发出频率很大的脉冲。

当今不管是指针式的电子钟还是数字显示的电子钟都使用了晶体振荡器电路。

2、计数译码显示74LS248译码器译码的是高电平,所以对应的显示器应为共阴极显示器。

所有计数器的显示均采用共阴极显示器SEVEN_SEG_COM。

信号质量测试用例一、引言信号质量测试是在无线通信领域中广泛应用的一项技术,它用于评估信号的稳定性及其对通信质量的影响。

本文将介绍信号质量测试用例的编写方法,旨在帮助测试工程师在进行信号质量测试时能够更加高效、准确地完成任务。

二、测试用例1:信号强度测试1. 测试目的:评估信号的强度是否达到预期标准,以判断其对通信质量的影响。

2. 测试步骤:a) 将测试设备与被测设备相连,并确保连接正常。

b) 在相同环境条件下,逐渐增加被测设备与测试设备之间的距离,记录信号强度的变化。

c) 根据预设的信号强度标准,判断信号是否达到预期要求。

3. 期望结果:a) 信号强度随距离的增加逐渐下降,并在一定距离后低于预设标准。

b) 如果信号强度超出了预设标准,则需要进一步分析原因,可能是设备故障或环境问题。

4. 备注:a) 测试过程中应记录下信号强度的数值,以便后续分析。

b) 可以尝试不同位置和环境下的测试,以更全面评估信号强度。

三、测试用例2:信噪比测试1. 测试目的:评估信号与噪声的比值,以判断信号的可靠性和可用性。

2. 测试步骤:a) 在无噪声的环境下,记录信号的基准值(理想信号)。

b) 逐渐引入噪声,在不同信噪比条件下记录信号的变化。

c) 根据预设的信噪比标准,判断信号是否达到预期要求。

3. 期望结果:a) 随着信噪比的降低,信号的质量逐渐下降。

b) 如果信噪比超出了预设标准,则需要进一步分析原因,可能是设备问题或噪声源的干扰。

4. 备注:a) 在进行信噪比测试时,需要确保测试环境的噪声水平稳定。

b) 可以使用不同噪声源进行测试,以模拟不同实际应用场景下的信号情况。

四、测试用例3:信号延迟测试1. 测试目的:评估信号传输的延迟情况,以判断其对实时通信的影响。

2. 测试步骤:a) 在相同网络环境下,将测试设备与被测设备相连。

b) 向被测设备发送信号,记录信号的发送时间和接收时间。

c) 计算信号的传输延迟。

3. 期望结果:a) 信号的传输延迟应在预设的范围内,保证实时通信的需求。

时钟信号测试方法

时钟信号测试方法是一项非常重要的技术,它可以用于验证时钟信号的质量和准确性。

在本文中,我们将介绍几种常见的时钟信号测试方法,包括:

1. 频率测量法:通过测量时钟信号的频率来判断其准确性和稳定性。

这种方法通常使用频率计或示波器进行测量。

2. 相位测量法:通过测量时钟信号的相位来判断其准确性和稳定性。

这种方法通常使用相位计或频谱分析仪进行测量。

3. 抖动测量法:抖动是指时钟信号在短时间内产生的频率或相位偏移。

抖动测量法可以用于评估时钟信号的稳定性和准确性。

这种方法通常使用抖动仪进行测量。

4. 时钟同步测试法:通过将两个时钟信号进行比较来判断它们的同步性和准确性。

这种方法通常使用同步测试仪进行测量。

总之,时钟信号测试方法是非常重要的,可以帮助我们确保时钟信号的准确性和稳定性,以便在各种应用中使用。

- 1 -。

1.目的测量手机各状态纯工作时长是否符合设计规范和用户正常使用。

2.适用范围适合移动产品试产及相关变更的验证。

3.内容3.1 手机待机时长(测试用例编号:5.4.1)3.1.1 测试条件和说明1)被测机1台装SIM卡、TF卡,测试前手机需至少上电2小时保证后备电池充满电(以保证关机漏电流不是测了后备电池充电电流),测试过程中手机背光等级/时长、键盘锁与音量级等均为默认;2)测试用移动卡2张、测试用电脑1台、程控电源1台(3.8V)、假电池1个、SkyworksLabteststudio电流分析软件(设置:Sample interval:1996.8uS,Sample points:501, Sample length:3600S),如没特别说明,电流值均由电流分析软件读取;3)手机开关机时长规定:开机时长15小时(早上7:30~晚上22:30),关机时长9小时(晚上22:30~早上7:30);4)用户使用时长参考营销部调查结果,在计算手机待机时长时引用。

3.1.2 测试步骤1)关机漏电流:手机关机状态时的电流,在程控电源上直接电流值,关机时长为9H(上面3.1.1第3)点规定)。

2)待机省电平均搜网电流:手机开机待机省电/后台挂Q(不收到消息),正常环境里的30秒平均搜网电流;用户使用时长=15*3600-T1-…T17=54000-6410=47590秒(备注:T1...T17为以下第3到第17项各项用户使用时长)。

3)关机响闹铃电流:手机关机期间响闹铃(闹钟响0db_1Khz.mp3、响铃方式:响铃+振动)30秒手动停止选择开机后进入省电过程中的平均电流;用户使用时长=30秒。

4)开机响闹铃电流:手机待机省电期间响闹铃(闹钟响0db_1Khz.mp3、响铃方式:响铃+振动)30秒后手动停止后进入省电过程中的平均电流;用户使用时长=30秒5)来电响铃电流:正常环境手机待机省电期间外线来电响铃(响铃0db_1Khz.mp3、响铃方式:响铃+振动)10秒平均电流(每天来电4次);用户使用时长=10*4=40秒。

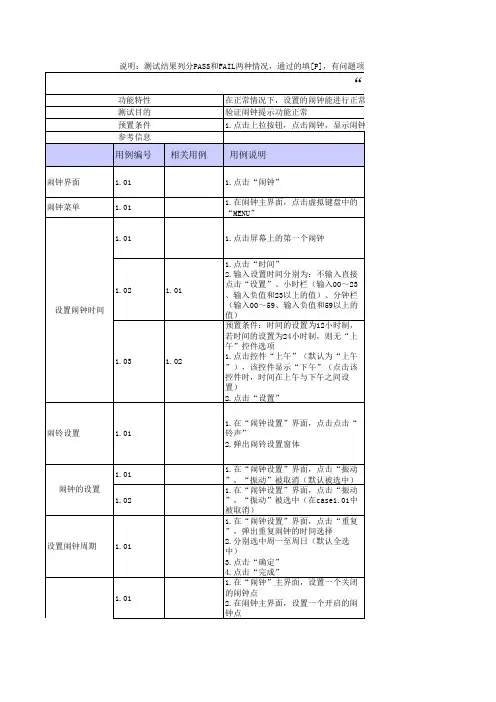

闹钟测试点和测试⽤例【正常和异常场景】【杭州多测师】【杭州多测师_王sir】1、设置时钟和⽇期与当地时间⽇期相符合,整个测试期间,除特别要求更改时间、⽇期外,不要随意更改基准时间;2、⼀般⽇期设置完毕,星期⾃动⽣成,应准确⽆误;3、以24⼩时为⼀观察周期,⽐较⼿机时间与标准时间的误差;4、设置实际不存在的时间和⽇期,设置⽇期0⽉、0⽇、13⽉、32⽇等,设置如2003年2⽉29⽇等不切实际的时间⽇期,⼿机应不予接纳,有正确提⽰;5、设置好时钟、⽇期后通过正常关机、拔电池、⾃动关机等动作后再开机,时间、⽇期不应有错误现象出现,即⼿机保持时钟正常运转;6、⼿机关机后,拔掉电池,观察⼿机可保持时钟继续正常运转最长时间;7、设置特定闹钟,设置的响闹时间应较⼴泛的采样,如23:59、00:00、12:00等,响闹应如期进⾏;8、设置特定闹钟,将闹钟如数设满,有响闹提⽰的,⽤汉字、英语、数字等将提⽰语输满,响闹提⽰⽅式(铃声、振动、灯光等);均应选择,做好记录,观察响闹与实际设置值是否符合;9、设置特定闹钟,将响闹时间设置为过去时,⼿机应不予接纳或显⽰相关错误信息;10、设置特定闹钟,在关机状态下可执⾏闹钟功能的⼿机在关机时需进⾏测试闹钟是否准确,有效;11、对闹钟进⾏操作,闹钟响闹前修改⽇期、时间;闹钟响闹前修改闹铃;闹钟响闹前删除闹钟;闹钟响闹前添加闹铃;闹钟响闹前修改时区;闹钟响闹前关机;闹钟响闹前重启;闹钟响闹前拔电池;12、编辑闹钟,对已设置的闹钟进⾏更改、删除等操作,闹钟响闹时间应符合编辑后的值;13、设置周期闹钟,周期间隔⼀般有⼩时、天、星期、⽉等,均应按实际使⽤进⾏设置,观察响闹是否正确;14、在闹钟设置的任何界⾯,有来电呼⼊、闹钟响闹、来新短消息、低电告警、⾃动关机时间到、⼩区⼴播到,显⽰是否正常(分别测试闹钟功能时有事件到完成选择后再查看事件和马上退出查看);15、在闹钟设置的任何界⾯,有来电卫⼠电话呼⼊、⽆条件转移电话、车载模式下,有来电呼⼊,显⽰是否正常;16、在闹钟设置的任何界⾯,按左软键、右软键、⽅向键、挂机键或按任意⽆效键时,各功能是否正常;在任何界⾯,按挂机键关机,再开机,显⽰是否正常;在输⼊⽂本过程中,反复插拔充电器,是否正常;17、来电、短消息、闹钟要选择不同的提⽰⽅式(如下载铃声、图⽚);。

信号质量测试规范本规范修改记录:目录1引言 (5)2适用范围 (5)3信号质量测试概述 (5)3.1信号完整性 (5)3。

2信号质量 (6)4信号质量测试条件 (10)4.1单板/系统工作条件: (10)4.2信号质量测试人员要求: (10)4。

3示波器选择与使用要求: (10)4。

4探头选择与使用要求 (11)4.5测试点的选择 (12)5信号质量测试通用标准 (12)5。

1信号电平简述: (12)5.2合格标准 (13)5.3信号质量测试结果分析注意事项 ................................................................ 错误!未定义书签。

6信号质量测试方法 . (16)6。

1电源信号质量测试 (16)6。

1.1简述 (16)6。

1。

2测试项目 (16)6.1。

3测试方法 (16)6。

2时钟信号质量测试 (22)6。

2。

1简述 (22)6。

2。

2测试方法 (22)6。

2。

3测试指标与合格标准 (22)6.2。

4注意事项 (24)6。

3复位信号质量测试 (25)6。

3.1简述 (25)6。

3.2测试方法 (25)6。

3.3测试项目与合格标准 (25)6。

3。

4注意事项 (27)6。

3。

5测试示例 (27)6。

4数据、地址信号质量测试 (29)6.4。

1简述 (29)6。

4.2测试方法 (29)6.4。

3测试项目 (30)6。

4。

4测试示例: (30)6.5差分信号质量测试 (31)6.5.1简述 (31)6.5。

2测试项目 (31)6.5。

3测试方法 (32)6。

5。

4合格标准 (32)6。

5。

5注意事项 (34)6。

5。

6测试示例 (34)6.6串行信号质量测试 (35)6.6。

1概述 (35)6.6.2测试项目 (36)6.6.3测试方法 (37)6。

6.4合格标准 (37)7信号质量测试CHECKLIST (39)8测试系统接地说明 (41)9引用标准和参考资料 (43)信号质量测试规范关键词:信号完整性、测试摘要:本规范详细说明了单板信号质量测试的方法.其中包括各类信号波形参数的定义,进行信号质量测试的条件,覆盖范围,合格标准,信号分类,各类信号波形参数的指标,测试点的选择以及测试结果分析重点。

手机闹钟测试用例闹钟测试用例1、基本功能测试:用例名称用例编号01设计人测试目标基本功能:测试闹铃是否正常响起前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号02设计人测试目标基本功能:浏览网页时,闹钟可以响起前置条件设定闹铃时间为17:00步骤操作描述期望结果浏览网页时,闹铃时间到主界面出现闹铃界面,铃声响起点击关闭闹铃闹铃关闭,停留在网页页面用例名称用例编号03设计人测试目标基本功能:输入闹铃后,可以正常响起前置条件输入闹铃时间为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号04设计人测试目标基本功能:设置闹铃后,可以正常响起前置条件输入闹铃时间为23:59步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号05设计人测试目标基本功能:设置闹铃时间后,可以正常响起前置条件输入闹铃时间为00:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号06设计人测试目标基本功能:输入闹铃说明(汉字/英文/数字),闹铃响起时出现提示字前置条件输入闹铃时间为17:00步骤操作描述期望结果闹铃时间到铃声响起,主界面出现输入的提示字点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号07设计人测试目标基本功能:设置闹铃重复,在重复日期可以响起前置条件输入闹铃时间为17:00,重复为每天步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃闹铃关闭次日闹铃时间到主界面出现闹铃界面,并且铃声响起点击关闭闹铃闹铃关闭用例名称用例编号08设计人测试目标基本功能:闹铃响起后点击重响前置条件输入闹铃时间为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起点击重响闹铃暂时关闭五分钟后主界面出现闹铃界面,铃声继续响起点击关闭闹铃闹铃关闭用例名称用例编号09设计人测试目标基本功能:闹铃设置成功后,关闭手机看时间到闹铃是否响起前置条件输入闹铃时间为17:00步骤操作描述期望结果设置完成闹铃,关闭手机手机关闭闹铃时间到铃声响起,出现关闭/重响提示选择重响闹铃暂时关闭,五分钟后再次响起选择关闭出现时候开机提示用例名称用例编号设计人测试目标基本功能:编辑短信时,闹铃响起前置条件输入闹铃时间为17:00步骤期望结果正在编辑短信,闹铃响起短信模块中出现闹铃界面点击重响闹铃铃声暂停,继续编辑短信五分钟后铃声再次响起点击关闭闹铃铃声停止,继续编辑短信2、冲突测试:用例名称用例编号01设计人测试目标冲突测试:闹铃响起时,拔出内存卡前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起拔出内存卡若闹铃铃声来自内存卡则闹铃铃声停止若闹铃铃声来自手机则铃声依然响点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭闹铃继续响用例名称用例编号02设计人测试目标冲突测试:闹铃响起时,插入内存卡前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起插入内存卡闹铃停顿几秒后继续响起点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号03设计人测试目标冲突测试:闹铃响起时,插入充电器前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起插入充电器闹铃停顿几秒后继续响起若闹铃铃声来自手机则铃声依然响点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号04设计人测试目标冲突测试:闹铃响起时,拔出充电器前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起拔出充电器闹铃停顿几秒后继续响起若闹铃铃声来自手机则铃声依然响点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号05设计人测试目标冲突测试:闹铃响起时,拔出充电器前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起拔出充电器闹铃停顿几秒后继续响起若闹铃铃声来自手机则铃声依然响点击关闭闹铃出现提示框询问是否关闭点击是闹铃关闭点击否闹铃继续响用例名称用例编号06设计人测试目标冲突测试:闹铃响起时,来电话但不接听前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来电话出现电话界面,闹铃暂时不响挂断电话闹铃停顿几秒后响起点击关闭闹铃闹铃关闭用例名称用例编号07设计人测试目标冲突测试:闹铃响起时,来短信前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来短信显示有短信,并且闹铃响起点开短信闹铃停止响起退出短信闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号08设计人测试目标冲突测试:闹铃响起时,来彩信前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来彩信显示有彩信,并且闹铃响起点开短彩信闹铃停止响起退出彩信闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号09设计人测试目标冲突测试:闹铃响起时,收到短信发送报告将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,收到短信发送报告显示发送报告,并且闹铃暂停退出发送报告闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,收到彩信发送报告前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,收到彩信发送报告显示发送报告,并且闹铃暂停退出发送报告闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人冲突测试:闹铃响起时,来电话接听前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来电话接听电话,闹铃暂时不响挂断电话闹铃停顿几秒后响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,来电话对方挂断前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来电话出现电话界面,闹铃暂时不响对方挂电话,点击显示来电闹铃依然停顿退出显示来电闹铃继续响起点击关闭闹铃用例名称用例编号设计人测试目标冲突测试:闹铃响起时,来电话接听后对方挂断前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到,来电话接听电话,闹铃暂时不响对方挂电话闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,插入耳机前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起插入耳机显示插入耳机提示,闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,拔出耳机前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起拔出耳机显示拔出耳机提示,闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,充电完成前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起此时充电完成屏幕上显示充电完成提示,闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,低电量前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起此时手机电量低屏幕上显示手机电量低提示,闹铃继续响起点击关闭闹铃闹铃关闭用例名称用例编号设计人测试目标冲突测试:闹铃响起时,低电量自动关机前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起此时手机电量低自动关机屏幕上显示手机电量低自动关机,闹铃关闭,自动关机用例名称用例编号设计人测试目标冲突测试:闹铃响起时,长按关机键前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起此时长按关机键屏幕上显示是否关机提示,闹铃关闭,自动关机用例名称用例编号设计人测试目标冲突测试:闹铃响起时,拔出电池前置条件将闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现闹铃界面,并且铃声响起此时拔出电池铃声消失,非法关机3、压力测试:用例名称用例编号01设计人测试目标压力测试:设置多个闹铃前置条件将10个闹钟响起时间设定为17:00 步骤操作描述期望结果进入闹铃设置界面出现设置新闹铃点击设置新闹铃出现设置新闹铃界面一次设置多个新闹铃闹铃设置成功,并且主界面显示闹铃图标用例名称用例编号02设计人测试目标压力测试:清空设置的闹铃前置条件将50个闹钟响起时间设定为17:00 步骤操作描述期望结果闹铃时间未到手机主界面显示闹铃图标进入闹铃设置清空闹铃,退出闹铃设置手机主界面闹铃图标消失用例名称用例编号03设计人测试目标压力测试:设置多个闹铃同时响起前置条件将10个闹钟响起时间设定为17:00步骤操作描述期望结果闹铃时间到主界面出现多个闹铃界面,并且铃声响起点击关闭闹铃出现提示框询问关闭当前界面/关闭全部界面点击关闭当前界面有一个闹铃界面关闭,铃声依然响起点击关闭全部界面退出闹铃界面,铃声停止。

CLOCK信号完整性测试指导书功能: 信号完整性阶段:验证文档版本: A发布日期: 2009/06/24批准人员审核人员准备人员BY曾瑜黄世民梁波DATE2009/06/242009/06/242009/06/24目录1. 目的 (3)2. 适用范围 (3)3. 测量设备 (4)4. 参考文件 (4)5. 注意事项 (4)6.测试项目 (4)7. 操作步骤 (5)※※修订履历※※REV.修订内容发行日期备注A初版发行2009/06/241. 目的依照规格手册,介绍和规范在测量CLOCK信号时的操作。

2. 适用范围用于VTRON拼墙和IDB产品在做信号完整性量测时的应用。

3. 测量设备Tektronix TDS 3034 Qty=1 Tektronix P6139A Probe Qty=2 4. 参考文件4.1《TDS3034操作手册》4.2 相关测试点位组件的DATASHEET,线路图等。

VTRON 作业指导书 研发中心 /测试部/硬件测试组5. 注意事项5.1 确认测试人员静电环接触良好5.2 在测量时应检查示波器是否运行正常5.3 检查信号连接是否正确,接地是否合理5.4 确定待测系统SUT 是否工作在预定的模式6.测试项目信号测试项测试点参考标准备注Vih (高电平幅值)芯片规格书Vil (低电平幅值))芯片规格书Tr (上升时间)芯片规格书Tf (下降时间)芯片规格书频率芯片规格书占空比芯片规格书正脉冲宽度芯片规格书负脉冲宽度芯片规格书周期芯片规格书抖动芯片规格书Overshoot 芯片规格书CLOCK 信号Undershoot芯片规格书以上为基本测试项目,测试时先参考芯片规格!测试参数图示:图一 CLOCK7. 操作步骤6.1 操作前准备6.1.1 执行探头的校正或DSKEW(多通道),确认结果是PASS.6.2 测试流程6.2.1 按下电源开关,开始进入操作接口对于示波器操作接口和基本操作,參考《TDS3034操作手册》。

高速时钟信号的信号完整性测试与分析

沈慧敏;戎蒙恬

【期刊名称】《黑龙江科技信息》

【年(卷),期】2009(000)021

【摘要】随着高速数字电路的快速发展,信号完整性验证的重要性日益凸现,着重讲述在设计后期,如何通过有效的信号完整性测试,保证CPU时钟的信号完整性,为系统的稳定工作打下基础.

【总页数】2页(P28-29)

【作者】沈慧敏;戎蒙恬

【作者单位】上海交通大学电子工程系,上海,200240;上海交通大学电子工程系,上海,200240

【正文语种】中文

【中图分类】TN929.53

【相关文献】

1.基于高速时钟电路终端的信号完整性分析 [J], 陈倩

2.一种分析高速时钟网络信号完整性的有效方法 [J], 魏敬和;陈军宁;柯导明;吴建辉;陆生礼

3.高速时钟电路的信号完整性设计 [J], 吕霆;祝亮

4.基于AD9517-1的高速时钟系统稳定性设计与信号完整性分析 [J], 俞一超;吴宪顺;庄晴光

5.高速时序信号完整性及时钟端接问题研究 [J], 王典洪;周欣

因版权原因,仅展示原文概要,查看原文内容请购买。

1.目的

测量手机各时钟信号是否符合设计规范,以确保手机各项性能稳定可靠。

2.适用范围

适用于新开发手机产品在试产阶段的评测。

3.测试准备和说明:

3.1程控电源、数字示波器、频率计、原理图及PCB丝印图、原配耳机、SIM卡、TF卡、

烙铁、细导线若干、蓝牙耳机;

3.2测试结果如有必要需附测试波形图。

4.测试过程:

4.1 实时钟32.768KHz时钟测试(测试用例编号:

5.

6.1)

4.1.1测试条件:

被测机开壳,装SIM卡、TF卡开机。

4.1.2 测试步骤:

1)从原理图上找到32.768KHz晶体位置,频率计探头负极接地,正极接晶体XOUT 端,频率计(10M档位)读数即为晶体频率;

2)示波器采集模式设为取样,余辉时间设置为5秒;

3)通道耦合选取直流模式,档位设定为100mV,时间标度设置为10.0us;

4)按测量键选取测量频率,上升时间,下降时间,峰值电压,占空比等;

5)按测试说明要求,在摄像状态选取一个半周期的完整波形,按运行/停止键抓取波形,测量读取数据并按Save键保存波形。

4.1.3 预期结果:

测试项目参考值

电压峰值690-750mV

毛刺0

频偏±20ppm

抖动幅度0

占空比50%

4.2 主时钟26MHz时钟测试(测试用例编号:

5.

6.2)

4.2.1测试条件:

被测机开壳,被测机开壳,装SIM卡、TF卡开机。

4.2.2 测试步骤:

1)从原理图上找到26M晶体位置,频率计探头负极接地,正极接晶体XOUT端,频

率计(120M档位)读数为即晶体频率;

2)示波器采集模式设为取样,余辉时间设置为5秒;

3)通道耦合选取直流模式,档位设定为500mV,时间标度设置为400ns;

4)按测量键选取测量频率,上升时间,下降时间,峰值电压,占空比等;

5)按测试说明要求,在通话状态选取一个半周期的完整波形,按运行/停止键,测量并读取数据,上升时间,下降时间,峰值电压,占空比等,按Save键保

存波形。

4.2.3 预期结果:

测试项目参考值

电压峰值≤600mv

毛刺≤160

频偏±20ppm

抖动幅度0

占空比50%

4.3 蓝牙32MHz时钟测试(测试用例编号:

5.

6.3)

4.3.1测试条件:

被测机开壳,装SIM卡、TF卡开机,蓝牙开启,接蓝牙耳机。

4.3.2 测试步骤:

1)从原理图上找到32M晶体位置,频率计探头负极接地,正极接晶体XOUT端,频

率计(120M档位)读数为即晶体频率;

2)示波器采集模式设为取样,余辉时间设置为5秒;

3)通道耦合选取直流模式,档位设定为200mV,标度设置为400ns;

4)按测量键选取测量频率,上升时间,下降时间,峰值电压,占空比等;

5)按测试说明要求,在蓝牙听mp3状态选取一个半周期的完整波形,按运行/停止

键抓取波形,测量并读取数据再按Save键保存波形。

4.3.3 预期结果:

测试项目参考值

电压峰值≤800mv

毛刺0

频偏±20ppm

抖动幅度0

占空比50%

4.4 FM时钟测试(测试用例编号:

5.

6.4)

4.4.1测试条件:

被测机开壳,装SIM卡、TF卡开机,接耳机开收音。

4.4.2 测试步骤:

1)从原理图上找到FM时钟信号输入位置,频率计探头负极接地,正极接信号输

入端,频率计(10M档位)读数即为时钟频率;

2)示波器采集模式设为取样,余辉时间设置为5秒;

3)通道耦合选取直流模式,档位设定为1.0V,时间标度设置为10.0us;

4)按测量键选取测量频率,上升时间,下降时间,幅值电压,占空比等;

5)按测试说明要求,在插耳机收听调幅广播状态选取一个半周期的完整波形,

按运行/停止键抓取波形;

6)测量并读取数据后按Save键保存波形。

4.4.3 预期结果:

测试项目参考值

上升时间≤300

下降时间≤300

上过冲0.5V

下过冲-0.2V

电压幅值 2.8V

毛刺20mV。