第七章 微序列控制单元设计

- 格式:ppt

- 大小:1.82 MB

- 文档页数:96

微程序控制器的设计与实现一、引言微程序控制器是一种用于指令执行的高级控制器,它通过微指令序列来控制计算机的操作。

本文将介绍微程序控制器的设计与实现方法,包括微程序的设计原理、控制存储器的组织结构、微指令的编码和执行过程等。

二、微程序设计原理微程序设计是一种将指令的操作码映射为一系列微指令的方法。

每个微指令对应着计算机的一条基本操作,例如存储器读取、算术运算等。

微指令序列通过微程序计数器来控制,实现指令的顺序执行。

三、控制存储器的组织结构控制存储器是存储微指令序列的重要组成部分。

它通常采用的是RAM (Random Access Memory)的结构,以实现对微指令的随机读取。

控制存储器的地址由微程序计数器提供,通过地址译码器来选择对应的微指令。

四、微指令的编码微指令的编码是将指令的操作码映射为一系列控制信号的过程。

常见的编码方式有水平编码和垂直编码两种。

水平编码将每个控制信号独立编码,占用较多的位数;垂直编码则将多个控制信号合并编码,占用较少的位数。

根据具体的设计需求,可以选择适合的编码方式。

五、微指令的执行过程微指令的执行过程包括指令的获取、解码和执行三个阶段。

指令的获取是通过微程序计数器提供的地址从控制存储器中读取相应的微指令;指令的解码是将微指令中的控制信号解码为具体的操作;指令的执行是根据解码后的控制信号执行相应的操作,例如读取存储器、进行算术运算等。

六、实现微程序控制器的步骤实现微程序控制器的步骤包括微指令的设计、控制存储器的编程、控制信号的生成等。

首先,根据指令集的要求设计微指令的格式和编码方式;然后,根据微指令的格式编程控制存储器,将微指令序列存储其中;最后,根据微指令的编码生成相应的控制信号,控制计算机的操作。

七、实例分析以一个简单的加法指令为例,介绍微程序控制器的实现过程。

首先,设计微指令的格式,包括操作码、源操作数、目的操作数等字段;然后,编程控制存储器,将微指令序列存储其中;最后,根据微指令的编码生成相应的控制信号,例如读取源操作数、读取目的操作数、进行加法运算等。

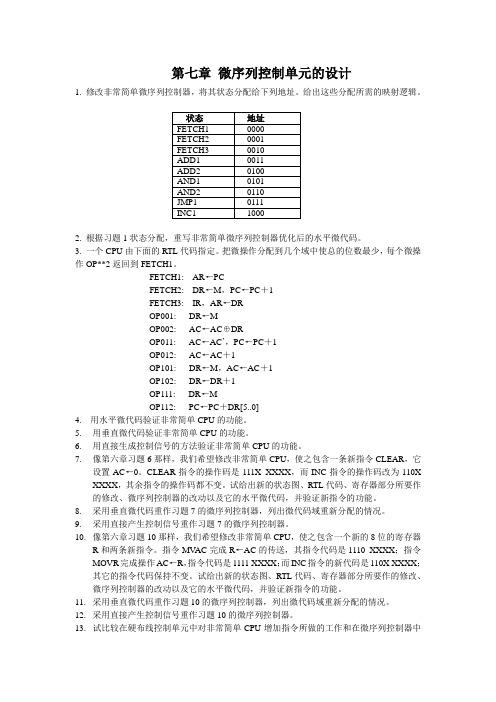

第七章微序列控制单元的设计1. 修改非常简单微序列控制器,将其状态分配给下列地址。

给出这些分配所需的映射逻辑。

2. 根据习题1状态分配,重写非常简单微序列控制器优化后的水平微代码。

3. 一个CPU由下面的RTL代码指定。

把微操作分配到几个域中使总的位数最少,每个微操作OP**2返回到FETCH1。

FETCH1: AR←PCFETCH2: DR←M,PC←PC+1FETCH3: IR,AR←DROP001: DR←MOP002: AC←AC⊕DROP011: AC←AC’,PC←PC+1OP012: AC←AC+1OP101: DR←M,AC←AC+1OP102: DR←DR+1OP111: DR←MOP112: PC←PC+DR[5..0]4. 用水平微代码验证非常简单CPU的功能。

5.用垂直微代码验证非常简单CPU的功能。

6.用直接生成控制信号的方法验证非常简单CPU的功能。

7.像第六章习题6那样,我们希望修改非常简单CPU,使之包含一条新指令CLEAR,它设置AC←0。

CLEAR指令的操作码是111X XXXX,而INC指令的操作码改为110X XXXX,其余指令的操作码都不变。

试给出新的状态图、RTL代码、寄存器部分所要作的修改、微序列控制器的改动以及它的水平微代码,并验证新指令的功能。

8.采用垂直微代码重作习题7的微序列控制器,列出微代码域重新分配的情况。

9.采用直接产生控制信号重作习题7的微序列控制器。

10.像第六章习题10那样,我们希望修改非常简单CPU,使之包含一个新的8位的寄存器R和两条新指令。

指令MV AC完成R←AC的传送,其指令代码是1110 XXXX;指令MOVR完成操作AC←R,指令代码是1111 XXXX;而INC指令的新代码是110X XXXX;其它的指令代码保持不变。

试给出新的状态图、RTL代码、寄存器部分所要作的修改、微序列控制器的改动以及它的水平微代码,并验证新指令的功能。

实验10 微程序控制器设计实验报告姓名:X XX 学号:X XX 专业:计算机科学与技术课程名称:计算机组成同组学生姓名:无实验时间:实验地点:指导老师:XXX一、实验目的和要求1.掌握微程序控制原理2.掌握微程序控制器的设计方法二、实验内容和原理实验内容:1.设计一个微程序控制单元并进行仿真实验原理:1.微程序的原理:●在多时钟CPU设计的实验中,所有的控制信号均根据操作码以及所处的时钟周期,由组合逻辑的方式产生各个状态下的控制信号。

●微程序是将CPU每条指令和所有时钟的控制信号,预先以二进制形式写在控制存储器中。

●多时钟周期的每个状态都对应一组控制信号。

●每条指令都有若干个状态对应若干组控制信号。

●微指令按一定顺序存放在控制存储器中。

2.工作原理图3.微程序控制逻辑图4.微指令及其控制码5.控制存储器内容三、主要仪器设备1.Spartan-III开发板1套2.装有ISE的PC机1台四、操作方法与实验步骤实验步骤:1.创建新的工程和新的源文件2.编写verilog代码(包括以下模块top,MicroCtrl,pbdebounce,time_1ms)3.对程序进行波形仿真4.编写UCF引脚文件,通过编译。

5.. 生成FPGA代码,下载到实验板上并调试,看是否与实现了预期功能实验代码:Top.vmodule top(input system_clk,input clk_i,input rst_i,output [3:0] anode4,output [7:0] segment4,output reg [7:0] led);wire clk;wire rst;reg [2:0] pc;reg [5:0] opcode;wire [17:0] rom_out;pbdebounce p0(system_clk, clk_i, clk);pbdebounce p1(system_clk, rst_i, rst);initial beginpc=0;endalways @ (posedge clk or posedge rst) beginif (rst==1)pc=0;else if (rom_out[1:0]==0)pc=pc+1;endalways @ * begincase (pc)0: opcode = 6'b000000; //R-type1: opcode = 6'b100011; //LW2: opcode = 6'b101011; //SW3: opcode = 6'b000100; //BEQ4: opcode = 6'b000010; //Jdefault: opcode = 6'b000000;endcaseendMicroCtrl MicroCtrl(clk, rst, opcode, rom_out);display display(system_clk, rom_out[17:2], anode4, segment4); always @ * beginled[1:0] = rom_out[1:0];led[2]=0;case (pc)0: led[7:3] = 5'b10000; //R-type1: led[7:3] = 5'b01000; //LW2: led[7:3] = 5'b00100; //SW3: led[7:3] = 5'b00010; //BEQ4: led[7:3] = 5'b00001; //Jdefault: led[7:3] = 5'b11111;endcaseendendmodulempc=0;endalways @ * begincase (mpc)0: rom_out={16'h0851,2'b11};1: rom_out={16'h1800,2'b01};2: rom_out={16'h3000,2'b10};3: rom_out={16'h00C0,2'b11};4: rom_out={16'h0300,2'b00};5: rom_out={16'h00A0,2'b00};6: rom_out={16'hA000,2'b11};7: rom_out={16'h0500,2'b00};8: rom_out={16'h6006,2'b00};9: rom_out={16'h0009,2'b00};default: rom_out=0;endcaseendalways @ (posedge clk or posedge rst) begin if (rst==1)mpc=0;else begincase (rom_out[1:0])0: mpc=0;3: mpc=mpc+1;1: case (opcode)6'b000000: mpc=6; //R-type6'b100011: mpc=2; //LW6'b101011: mpc=2; //SW6'b000100: mpc=8; //BEQ6'b000010: mpc=9; //Jdefault: mpc=0;endcase2: case (opcode)6'b100011: mpc=3; //LW6'b101011: mpc=5; //SWdefault: mpc=0;endcaseendcaseendendendmoduleDisplay.vmodule display(input wire clk,input wire [15:0] digit,//显示的数据output reg [ 3:0] node, //4个数码管的位选output reg [ 7:0] segment);//七段+小数点reg [3:0] code = 4'b0;reg [15:0] count = 15'b0;always @(posedge clk) begincase (count[15:14])//与(count[1:0])的不同?起到分频的作用2'b00 : beginnode <= 4'b1110;code <= digit[3:0];end2'b01 : beginnode <= 4'b1101;code <= digit[7:4];end2'b10 : beginnode <= 4'b1011;code <= digit[11:8];end2'b11 : beginnode <= 4'b0111;code <= digit[15:12];endendcasecase (code)4'b0000: segment <= 8'b11000000;4'b0001: segment <= 8'b11111001;4'b0010: segment <= 8'b10100100;4'b0011: segment <= 8'b10110000;4'b0100: segment <= 8'b10011001;4'b0101: segment <= 8'b10010010;4'b0110: segment <= 8'b10000010;4'b0111: segment <= 8'b11111000;4'b1000: segment <= 8'b10000000;4'b1001: segment <= 8'b10010000;4'b1010: segment <= 8'b10001000;4'b1011: segment <= 8'b10000011;4'b1100: segment <= 8'b11000110;Timer_1ms.vmodule timer_1ms(input wire clk,output reg clk_1ms);reg [15:0] cnt;initial begincnt [15:0] <=0;clk_1ms <= 0;endalways@(posedge clk)if(cnt>=25000) begincnt<=0;clk_1ms <= ~clk_1ms;endelse begincnt<=cnt+1;endendmodule五、实验结果与分析1. 仿真结果如下(仿真时间较长,分2张图展示):Ox00c00 0x0300 2’b003.程序运行成功后,将代码下载到实验板spartan3上验证按动按钮,发现数码管上显示的数值即仿真输出码的[17:2]位,且出现顺序一致,说明程序成功。

计算机组成原理课程设计:中央处理器-微程序控制器设计摘要本文档介绍了一个针对计算机组成原理课程的设计项目,即中央处理器的微程序控制器设计。

在设计中央处理器的微程序控制器时,我们将考虑指令的执行、数据的处理以及控制信号等关键方面。

通过这个设计项目,学生将深入了解计算机系统的核心组件并掌握微程序控制器的设计方法。

引言计算机组成原理课程旨在帮助学生理解计算机硬件系统的基本原理和组成部分。

其中,中央处理器是计算机系统中最核心的部分之一。

微程序控制器是中央处理器的关键组件,它通过微指令序列控制着处理器的各个部件。

本设计项目旨在实践计算机组成原理的理论知识和设计方法,使学生能够了解中央处理器的内部结构和工作原理,并掌握微程序控制器的设计技术。

设计目标本次设计的目标是: 1. 使用合适的指令集设计一个完整的微程序控制器。

2. 实现基本的指令执行功能,包括算术逻辑单元(ALU)操作、内存读写、条件分支和跳转等。

3. 考虑控制信号与数据通路之间的兼容性和时序关系。

4. 考虑指令的效率和性能,实现合理的指令编码和微指令生成策略。

设计内容1. 指令集设计在设计微程序控制器时,首先需要确定适合该设计的指令集。

指令集应该包括基本的算术、逻辑、移位和控制指令,以及内存读写指令。

根据实际需求,可以添加其他合适的指令。

2. 微指令设计为了实现指令集中的每个指令,需要设计相应的微指令。

微指令是一系列控制信号的序列,用于控制中央处理器中各个部件的操作。

每个微指令应该包含控制信号、操作码、寄存器的选择和数据通路的选择等信息。

3. 数据通路设计数据通路连接了CPU中各个部件,包括寄存器、ALU、控制器等。

在设计数据通路时,需要考虑指令的执行顺序、数据的传递和处理,以及控制信号的生成等。

数据通路应该支持指令的执行和数据操作。

4. 控制信号设计控制信号是微程序控制器中最关键的部分,它确定了中央处理器中各个部件的操作方式和时序。

在设计控制信号时,需要考虑不同指令的差异性和并行性,确保指令的正确执行。

微程序控制器的设计与实现

微程序控制器是一种用于控制微程序的硬件设备,它通常由控制存储器、控制

逻辑和时序电路组成。

微程序控制器的设计与实现可以分为以下几个步骤:

1. 确定微指令的格式:微指令是微程序的最小执行单位,包含了一系列控制信号,用于控制计算机的各个部件。

在设计微程序控制器之前,需要确定微指令的格式,包括控制信号的位数和编码方式。

2. 设计控制存储器:控制存储器用于存储微程序,每一个微指令对应一个存储

单元。

在设计控制存储器时,需要确定存储单元的数量和位数,以及存储单元的编址方式。

3. 设计控制逻辑:控制逻辑用于根据当前微指令和计算机的状态生成控制信号。

在设计控制逻辑时,需要根据微指令的格式和计算机的功能要求,确定各个控制信号的生成方式和逻辑关系。

4. 设计时序电路:时序电路用于控制微程序的执行顺序和时序要求。

在设计时

序电路时,需要考虑微指令的执行时间和时序要求,确保微程序的执行顺序和时序满足计算机的功能要求。

5. 实现微程序控制器:根据上述设计结果,可以开始实现微程序控制器。

实现

过程包括选择适当的集成电路、设计电路图、布线和焊接等步骤。

6. 调试和测试:完成微程序控制器的实现后,需要进行调试和测试,确保其功

能和性能符合设计要求。

调试和测试过程包括功能验证、时序分析和性能评估等步骤。

总之,微程序控制器的设计与实现需要进行微指令格式的确定、控制存储器的

设计、控制逻辑的设计、时序电路的设计、微程序控制器的实现以及调试和测试等步骤。

这些步骤需要根据计算机的功能要求和设计约束进行综合考虑和实现。

3.4 常规型微程序控制器组成实验一、实验目的1. 掌握时序发生器的组成原理。

2. 掌握微程序控制器的组成原理。

二、实验电路1. 时序发生器本实验所用的时序电路见图3.4。

电路由一个500KHz晶振、2片GAL22V10、一片74LS390组成,可产生两级等间隔时序信号T1-T4、W1-W3,其中一个W由一轮T1-T4组成,相当于一个微指令周期或硬连线控制器的一拍,而一轮W1-W3可以执行硬连线控制器的一条机器指令。

另外,供数字逻辑实验使用的时钟由NF经一片74LS390分频后产生。

图3.4 时序信号发生器本次实验不涉及硬连线控制器,因此时序发生器中产生W1-W3的部分也可根据需要放到硬连线控制器实验中介绍。

产生时序信号T1-T4的功能集成在图中左边的一片GAL22V10中,另外它还产生节拍信号W1-W3的控制时钟CLK1。

该芯片的逻辑功能用ABEL语言实现。

其源程序如下:MODULE TIMER1TITLE 'CLOCK GENERATOR T1-T4'CLK = .C.;"INPUTMF, CLR, QD, DP, TJ, DB PIN 1..6;W3 PIN 7;"OUTPUTT1, T2, T3, T4 PIN 15..18 ISTYPE 'REG';CLK1 PIN 14 ISTYPE 'COM';QD1, QD2, QDR PIN ISTYPE 'REG';ACT PIN ISTYPE 'COM';S = [T1, T2, T3, T4, QD1, QD2, QDR];EQUATIONSQD1 := QD;QD2 := QD1;ACT = QD1 & !QD2;QDR := CLR & QD # CLR & QDR;T1 := CLR & T4 & ACT # CLR & T4 & ! (DP # TJ # DB & W3) & QDR;T2 := CLR & T1;T3 := CLR & T2;T4 := !CLR # T3 # T4 & !ACT & (DP #TJ# DB& W3) # !QDR;CLK1 = T1 # !CLR& MF;S.CLK = MF;END节拍电位信号W1-W3只在硬连线控制器中使用,产生W信号的功能集成在右边一片GAL22V10中,用ABEL语言实现。