推荐-组合逻辑控制单元设计 精品

- 格式:doc

- 大小:260.43 KB

- 文档页数:12

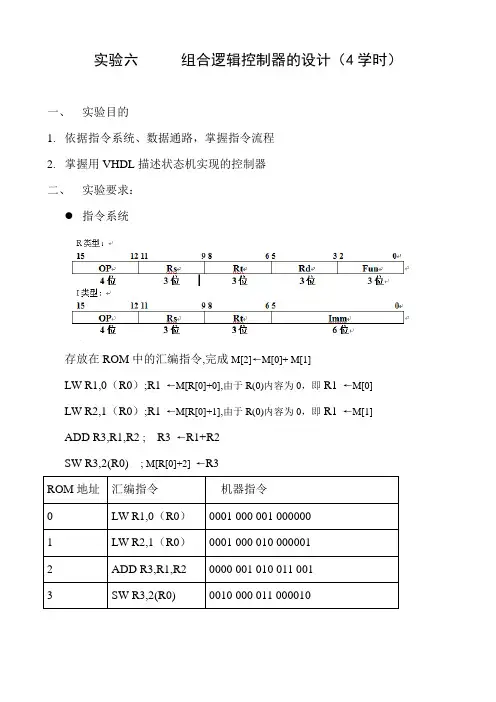

实验六组合逻辑控制器的设计(4学时)

一、实验目的

1.依据指令系统、数据通路,掌握指令流程

2.掌握用VHDL描述状态机实现的控制器

二、实验要求:

指令系统

存放在ROM中的汇编指令,完成M[2]←M[0]+ M[1]

LW R1,0(R0);R1←M[R[0]+0],由于R(0)内容为0,即R1←M[0]

LW R2,1(R0);R1←M[R[0]+1],由于R(0)内容为0,即R1←M[1]

ADD R3,R1,R2 ; R3←R1+R2

SW R3,2(R0) ; M[R[0]+2]←R3

●数据通路如下图所示:

控制信号的含义:

irwr,pcwr,regwr,aluoutregwr,memwr,lmdwr:相应组件的写使能控制信号,为1时,有效

Regdst: 为1时选择RD;为0时选择RT.

Signex:为1时扩展器进行符号扩展;为0时扩展器进行零扩展。

Aluselb:为1时选择暂存器B;为0时选择扩展器的输出端。

Alufunc:0000与运算;0001或运算;0010异或;0011取反;0100加;0101减Memtoreg:为1时选择LMD;为0时选择aluoutput

●给出ROM中指令的指令流程

●依据指令流程图画出状态转换图:

●依据状态转换图,写出控制器的VHDL描述

●控制器与多周期的数据通路形成处理器,通过ROM、RAM中的程序验

证处理器

四、仿真结果及说明

1.指令LW R1,0(R0) 执行过程中状态转换及寄存器、存储器内容变化情况。

硬布线控制器组合逻辑单元logisim设计原理(一)硬布线控制器组合逻辑单元logisim设计引言在数字电路设计中,组合逻辑电路(Combinational Logic Circuit)由一系列的逻辑门和逻辑门之间的连线组成。

而硬布线控制器(Hardwired Control Unit)是指根据固定的逻辑规则实现的指令解析和控制信号生成功能的电路单元。

在本文中,我们将介绍如何利用logisim设计一个基本的硬布线控制器组合逻辑单元。

设计原理硬布线控制器的核心是组合逻辑电路,通过逻辑门和逻辑门之间的连线实现不同的控制信号生成功能。

在logisim中,我们可以利用预置的逻辑门模块和连线工具来实现硬布线控制器的设计。

步骤1.导入logisim在首先,我们需要下载并安装logisim软件。

logisim是一款开源的数字电路设计工具,提供了丰富的组合逻辑元件和连线工具。

2.创建新电路打开logisim后,点击“新建”按钮创建一个新的电路文件。

我们可以将电路文件保存为任意名称,方便后续使用。

3.添加输入端口在logisim中,我们可以通过添加端口元件来实现输入和输出的连接。

点击“添加”按钮,在弹出的菜单中选择“端口”,然后将端口元件拖放到电路画布上。

4.添加逻辑门元件根据具体的设计需求,我们可以在logisim中选择合适的逻辑门元件。

点击“添加”按钮,在弹出的菜单中选择对应的逻辑门元件,然后将其拖放到电路画布上。

5.连线连接通过选中逻辑门元件和端口元件,使用连线工具将它们连接起来。

可以通过点击逻辑门元件或端口元件的输入或输出端口,然后拖动连线工具来绘制连线。

6.设计控制信号逻辑利用不同的逻辑门元件和连线工具,根据逻辑规则来设计控制信号的生成逻辑。

可以使用与门、或门、非门等来实现逻辑运算,并利用连线工具进行输入端口和逻辑门元件之间的连接。

7.添加输出端口在logisim中,通过添加输出端口元件来输出结果。

点击“添加”按钮,在弹出的菜单中选择“端口”,然后将端口元件拖放到电路画布上。

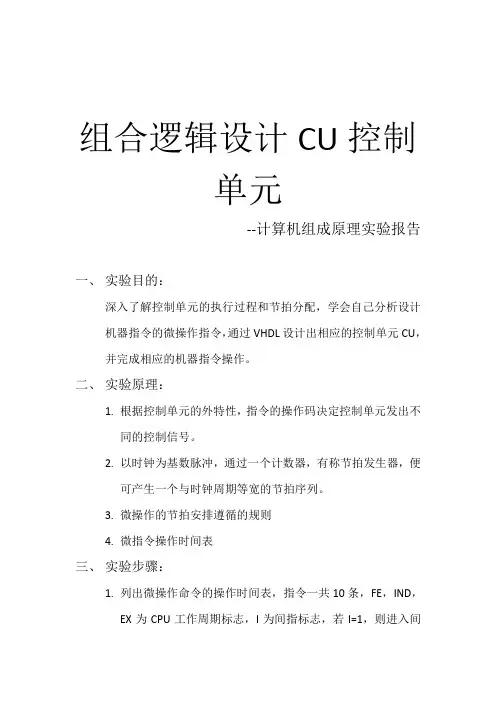

组合逻辑设计CU控制单元--计算机组成原理实验报告一、实验目的:深入了解控制单元的执行过程和节拍分配,学会自己分析设计机器指令的微操作指令,通过VHDL设计出相应的控制单元CU,并完成相应的机器指令操作。

二、实验原理:1.根据控制单元的外特性,指令的操作码决定控制单元发出不同的控制信号。

2.以时钟为基数脉冲,通过一个计数器,有称节拍发生器,便可产生一个与时钟周期等宽的节拍序列。

3.微操作的节拍安排遵循的规则4.微指令操作时间表三、实验步骤:1.列出微操作命令的操作时间表,指令一共10条,FE,IND,EX为CPU工作周期标志,I为间指标志,若I=1,则进入间指周期。

在执行周期的T2时刻,CPU要向所有的中断源发出中断查询信号,若检测到有中断请求并且满足响应条件,则INT触发器置1,标志进入中断周期。

2.写出微操作命令的最简逻辑表达式。

根据位操作命令操作时间表可列出每一个微操作命令的初始逻辑表达式,经化简,整理便可获得能用现成电路实现的微操作命令逻辑表达式。

3.画出微操作命令的逻辑图。

对应每一个微操作命令的逻辑表达式都可画出一个逻辑图。

4.通过以上几条进行相应的VHDL代码编写,执行结果如下。

四、实验结果:通过一个4位二进制数为IR制定指令的标号:根据写出的微操作命令的最简逻辑表达式编写VHDL代码:波形图展示:Ir(指令号),m(工作周期),t(节拍),i(间指标志),a0(负标记),c(微指令执行标志,1代表相应微指令执行)。

指令1展示:STP指令上图为三个工作周期,其中每个工作周期分为3个节拍,最后一行是用到的微操作命令指示。

指令2展示:上图为三个工作周期,其中每个工作周期分为3个节拍,最后一行是用到的微操作命令指示。

五、结论与总结:通过自主着手设计控制单元CU,我对控制单元执行过程产生了更加深入的理解。

将每一条机器指令通过分析设计,转化成CU 可执行的微指令操作。

其间,用到了数字逻辑的化简逻辑表达式,复习了化简得过程。

硬布线控制器组合逻辑单元logisim设计原理硬件布线控制器是一种用于控制计算机硬件的电路单元。

它通过输入和输出设备(如键盘、显示器、鼠标等)与计算机的中央处理器(CPU)进行通信,控制计算机各个部件的操作和数据传输。

硬布线控制器的设计原理是通过使用组合逻辑单元来实现不同的控制功能。

组合逻辑单元是由一系列逻辑门和触发器等构成的,它们可以实现不同的布尔逻辑运算。

在硬布线控制器中,组合逻辑单元被用于实现指令解码、数据传输控制、算术逻辑操作等功能。

在硬布线控制器中,指令解码是其中的一个重要功能。

当计算机接收到指令时,硬布线控制器会将指令进行解码,确定所需的操作,并将其发送到对应的硬件模块执行。

为了实现指令解码,可以使用译码器、多路选择器等组合逻辑单元来实现。

在解码过程中,控制器还需要保存程序计数器(PC)的值,以确保指令的顺序和正确运行。

数据传输控制是另一个重要的功能。

在计算机运行过程中,数据的输入和输出是不可避免的。

硬布线控制器使用组合逻辑单元来控制数据的输入和输出,包括通过总线(如地址总线、数据总线等)进行数据传输、选择合适的存储单元来存储数据等。

此外,硬布线控制器还可以实现算术逻辑操作。

在计算机运行过程中,通常需要进行一些数学或逻辑运算,如加法、减法、与门、或门、非门等。

硬布线控制器使用组合逻辑单元来实现这些运算,以支持计算机对数据的处理和操作。

总之,硬布线控制器通过使用组合逻辑单元实现了各种控制功能,以及数据传输和运算等操作。

它是计算机系统中不可或缺的一部分,能够使计算机能够进行各种操作,并且高效地处理和传输数据。

设计和理解硬布线控制器的原理对于学习和理解计算机系统的工作原理至关重要。

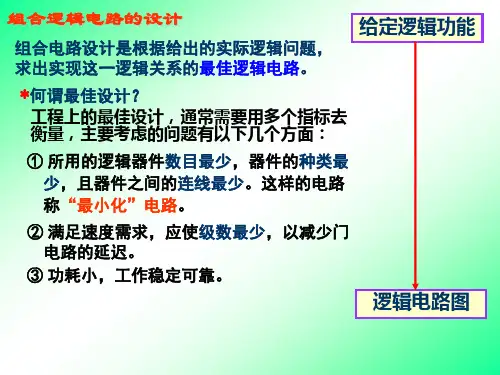

组合逻辑控制器的设计步骤嘿,咱今儿就来说说组合逻辑控制器的设计步骤。

这可不是什么随随便便就能搞定的事儿,就像搭积木,得一块一块精心摆弄才行。

首先呢,你得明确自己要干啥,就跟你出门得知道往哪儿走一样。

搞清楚系统的要求和功能,这可是基础中的基础。

你想想,要是连目标都不清楚,那不就瞎忙活啦?然后呢,根据这些要求,开始设计指令系统。

这指令系统就好比是一套规则,让各个部件知道该干啥,啥时候干。

这可得仔细琢磨,不能出岔子,不然整个系统都得乱套。

接下来,就是设计状态图啦。

这就像是给系统画一幅运行的路线图,每个状态都得考虑清楚,怎么转换,有啥条件。

这可不是闹着玩的,得费点心思呢。

再然后,根据状态图来确定逻辑表达式。

这可有点像解数学题,得一步步推导出来。

这里可不能马虎,一个小错误都可能导致大问题哦。

之后呢,就得选择合适的逻辑器件啦。

这就好比给系统选合适的工具,得好用又顺手。

要是选不好,那可就麻烦啦。

再接着,把这些逻辑器件组合起来,搭建出整个控制器。

这就像盖房子,一砖一瓦都得放对地方。

最后,可别忘了测试和优化呀。

就跟你新做了个东西得试试好不好用一样。

有问题就得赶紧改,可不能等出了大毛病再后悔。

你看,这组合逻辑控制器的设计步骤,一环扣一环,哪一步都不能马虎。

就像一场精彩的表演,每个环节都得配合好,才能呈现出完美的效果。

咱可不能小瞧了这些步骤,只有认真对待,才能设计出好用又可靠的组合逻辑控制器。

这不就跟咱过日子一样嘛,每一步都得走稳了,才能过得踏实,过得好呀!你说是不是这个理儿?。

控制单元的组合逻辑设计控制单元的设计本章以10条机器指令为例,介绍控制单元的两种设计方法。

第一节组合逻辑设计一、组合逻辑控制单元框图从控制单元的外特性图中可以看出,指令的操作码是决定控制单元发出不同控制信号的n关键。

为了简化控制单元的逻辑,将存放在IR的n位操作码经过一个译码电路产生2个输出,这样,每对应一种操作码便有一个输出送至CU。

当然,若指令的操作码长度可变,指令译码线路将更复杂。

控制单元的时钟输入实际上是一个脉冲序列,其频率即为机器的主频,它使CU能按一定的节拍(T)发出各种控制信号。

节拍的宽度应满足数据信息通过数据总线从源到目的所需的时间。

以时钟为计数脉冲,通过一个计数器,又称节拍发生器,便可产生一个与时钟周期等宽的节拍序列。

如果将指令译码和节拍发生器从CU中分离出来,便可得简化的控制单元框图,如下图所示。

二、微操作的节拍安排假设机器采用同步控制,每个机器周期包含3个节拍,而且CPU 内部结构为非总线结构,其中MAR和MDR分别直接和地址总线和数据总线相连,并假设IR的地址码部分与MAR之间有通路。

安排微操作节拍时应注意三点:第一,有些微操作的次序是不容改变的,故安排微操作节拍时必须注意微操作的先后顺序。

第二,凡是被控制对象不同的微操作,若能在一个节拍内执行,应尽可能安排在同一个节拍内,以节省时间。

第三,如果有些微操作所占的时间不长,应该将它们安排在一个节拍内完成,并且允许这些微操作有先后次序。

按上述三条原则,以第九章中所分析的10条指令为例,其微操作的节拍安排如下:1.取指周期微操作的节拍安排①根据原则二,T0节拍可安排两个微操作:PC→MAR,1→R;②根据原则二,T1节拍可安排M(MAR)→MDR和(PC)+1→PC 两个微操作。

③T2节拍可安排MDR→IR,考虑到指令译码时间较短,根据原则三,可将指令译码OP(IR) →ID也安排T2节拍内;实际上(PC)+1→PC操作也可安排在T2节拍内,因一旦PC→MAR 后,PC的内容就可修改。

硬布线控制器组合逻辑单元logisim设计原理硬布线控制器是一种使用硬布线电路实现的组合逻辑控制器。

相比于其他逻辑控制器,硬布线控制器的一个主要优势是其实时性和可靠性。

这是因为硬布线控制器直接使用硬件电路实现逻辑功能,不需要经过中间步骤,使得其执行速度更快,同时也减少了电路中元件的数量,提高了电路的可靠性。

第一步是确定所需的逻辑功能。

硬布线控制器可以实现各种功能,如加法器、减法器、乘法器等。

设计者首先需要明确所需实现的功能,并根据功能需求来确定逻辑门的种类和数目。

第二步是确定输入和输出的位数。

输入和输出的位数决定了逻辑门的数量。

例如,如果需要一个8位加法器,需要8个输入引脚和2个输出引脚。

第三步是选择逻辑门的类型。

逻辑门有多种类型,如与门、或门、非门等。

选择逻辑门的类型需要根据功能需求和电路设计的时序要求来确定。

第四步是将逻辑门按照功能需求进行布线连接。

布线连接的方式可以通过各种方法实现,如连接线、跳线等。

具体的布线方式取决于电路设计者的个人喜好和电路的复杂程度。

第五步是进行模拟测试和调试。

设计者需要利用模拟工具,如logisim等,对设计的电路进行模拟测试和调试。

通过模拟测试,可以验证电路的正确性和稳定性,并进行必要的调整和优化。

以上是硬布线控制器的设计原理。

设计者需要在明确功能需求的基础上,选择适当的逻辑门类型,并进行布线连接。

通过模拟测试和调试,最终实现所需的功能。

硬布线控制器的设计过程需要充分考虑电路的性能要求和电路元件的可靠性,以确保电路的正确运行和长期稳定性。

硬布线控制器组合逻辑单元logisim设计原理硬布线控制器是集成电路中的一种重要设计结构,用于实现各种逻辑电路的功能。

在硬布线控制器中,组合逻辑单元是其中的关键部分,它由多个逻辑门和/或逻辑门组成,用于实现不同的逻辑功能。

本文将探讨硬布线控制器组合逻辑单元的设计原理。

首先,硬布线控制器的组合逻辑单元设计需要考虑以下几个方面:输入与输出、功能实现、电路连接和电路延迟。

接下来,将详细介绍这些方面。

输入与输出是组合逻辑单元设计的基础,通常由多个输入引脚和一个输出引脚组成。

输入引脚用于接收输入信号,输出引脚用于输出逻辑计算的结果。

每个输入引脚可以是高电平(1)或低电平(0),根据每个逻辑门的真值表,可以得出输出引脚的电平。

功能实现是硬布线控制器的关键目标,通过逻辑门的组合和连接,可以实现各种布尔函数的功能。

常见的逻辑门有与门、或门、非门、异或门等。

通过组合这些逻辑门,可以实现各种布尔函数的逻辑计算,从而实现所需的功能。

电路连接是硬布线控制器设计过程中需要考虑的重要因素。

逻辑门之间的连接方式有串联和并联两种。

串联连接表示逻辑门的输出与下一个逻辑门的输入相连,这种连接方式可以通过将输出与输入引脚相连实现。

并联连接表示多个逻辑门的输出连接在一起,这种连接方式可以通过将多个逻辑门的输出引脚都连接到同一个输入引脚实现。

通过逻辑门之间的合理连接,可以实现复杂的逻辑计算功能。

电路延迟是硬布线控制器设计过程中需要考虑的另一个重要因素。

逻辑门的计算需要一定的时间,在计算过程中,输入引脚的电平可能发生变化,这会导致逻辑计算的结果发生错误。

为了解决这个问题,可以在逻辑门的输出和下一个逻辑门的输入之间添加寄存器或缓冲器,用于存储逻辑计算的结果并保持其稳定状态,从而避免电路延迟带来的错误。

综上所述,硬布线控制器组合逻辑单元的设计原理是通过输入与输出、功能实现、电路连接和电路延迟等方面的考虑,构建合适的逻辑门组合以实现所需功能。

掌握这些设计原理,可以帮助我们更好地理解硬布线控制器的工作原理,从而有效地进行硬布线控制器的设计与应用。

一、实验课题实验要求:按照题目要求用硬布线(组合逻辑)控制法设计一个简单模型机的控制单元CU(微操作信号产生电路),决定外部的端口(名称、有效电平)和内部各元件的连接,画出系统框图和逻辑图,设计仿真数据,用VHDL编程和仿真。

主要元件设计:1.指令译码器功能要求:3-8译码器。

2.控制单元功能要求:假设该模型机有8条不同类型的指令。

包括:算术运算、逻辑运算、移位、数据传送、访存操作、转移等。

根据每条指令的功能和时序,分析其执行过程中需要在各个阶段产生的全部微操作,导出产生这些微操作控制信号的逻辑。

3.用层次结构设计的方法设计一个控制单元CU(微操作控制信号产生电路)。

包括指令译码器和控制单元。

功能要求:能够正确产生8条不同指令在执行过程中(每个机器周期、每拍)发出的全部微操作。

二、逻辑设计写该实验的逻辑设计,包括:顶层系统框图,下层各主要元件的系统框图。

顶层和下层各主要元件的端口(引脚)描述:端口名称、功能、有效电平、位数等。

逻辑图,必须在图中清楚地标出每个内部连接线的Signal(与VHDL 程序中的Signal一致)。

根据所用的描述方式,可能还需要有:真值表/功能表/逻辑函数等。

1、3-8译码器:系统框图:S是工作信号,当S=1时,3-8译码器工作;当S=0时,3-8译码器不工作。

A是输入信号,Y是输出信号S A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y01 0 0 0 0 0 0 0 0 0 0 1 加法1 0 0 1 0 0 0 0 0 0 1 0 与1 0 1 0 0 0 0 0 0 1 0 0 或1 0 1 1 0 0 0 0 1 0 0 0 左移1 1 0 0 0 0 0 1 0 0 0 0 右移1 1 0 1 0 0 1 0 0 0 0 0 数据传送1 1 1 0 0 1 0 0 0 0 0 0 取数1 1 1 1 1 0 0 0 0 0 0 0 无条件转移0 ×××0 0 0 0 0 0 0 0Y(0)<=S and (not A(2)) and (not A(1)) and (not A(0));Y(1)<=S and (not A(2)) and (not A(1)) and A(0);Y(2)<=S and (not A(2)) and A(1) and (not A(0));Y(4)<=S and A(2) and (not A(1)) and (not A(0)); Y(5)<=S and A(2) and (not A(1)) and A(0); Y(6)<=S and A(2) and A(1) and (not A(0)); Y(7)<=S and A(2) and A(1) and A(0); 2、控制单元:设计过程:把每条指令的实现分成取指令、分析指令、执行指令三个步骤,每一步由一个机器周期实现,一条指令的实现需要三个机器周期,即M1(取指周期)、M2(分析周期)、M3(执行周期);每个机器周期由三个节拍组成,即T0、T1、T2。

如下图所示:1、加法指令:寄存器R1中的一个数与寄存器R0中的一个数相加,结果放在R1中。

即实现(R0)+(R1)→R12、与指令:寄存器R1中的一个数与寄存器R0中的一个数,结果放在R1中。

即实现(R1)and (R0) → R13、或指令:寄存器R1中的一个数或寄存器R0中的一个数,结果放在R1中。

即实现(R1)or (R0) → R14、逻辑左移指令:寄存器R1中的数左移,移动位数存放在寄存器R0中,结果放在R1中。

即实现(R1))左移(0R R15、逻辑右移指令:寄存器R1中的数左移,移动位数存放在寄存器R0中,结果放在R1中。

即实现(R1))右移(0R R16、数据传送指令:寄存器R0中的数据送到寄存器R1中。

即实现(R0)→ R1。

7、取数指令:取出存储器中的一个数(地址在寄存器R0中)送到寄存器R1中。

即实现 ((R0))→(R1)8、无条件转移指令:寄存器R1中的地址送到PC 中。

即实现(R1)→ PC8条指令的微操作如下表所示,以教材P122的CPU 控制图(省去了M/IO 、ADS )为例: 由于每条指令取指周期的微操作是一样的,所以可以先设计取指周期微操作的节拍安排。

取指周期:T0:PC →AB ,W/R =0T1:DB →IR机器周期节拍T 0 T 1 T 2系统框图:PC→AB = M0·T0W/R=0 = M0·T0+M1·T1·取数DB→IR = M0·T1PC+1 = M0 ·T2rs1→GR = M1 ·T0(rs1)→ALU = M1 ·T0+ = M1 ·T0·取数+M2·T1·(加+传送+取数+转移)ALU→AR =M1 ·T1 ·取数AR→AB =M1·T1 ·取数rd→GR =M1 ·T2·(加法+与+或+左移+右移)(rd)→ALU = M1 ·T2·(加法+与+或+左移+右移)DB→DR = M1 ·T2·取数DR→ALU = M2 ·T0·取数∧= M2·T1·与∨= M2·T1·或←= M2·T1·左移→=M2·T1·右移ALU→GR = M2·T2·(加法+与+或+左移+右移+数据传送+取数) ALU→PC = M2·T2·转移3、层次结构控制单元:逻辑图:三、VHDL程序--3-8译码器library ieee;use ieee.std_logic_1164.all;entity decoder38 isport( S:in std_logic;A:in std_logic_vector(2 downto 0);Y:out std_logic_vector(7 downto 0)); end decoder38;architecture behave of decoder38 isbeginprocess(S)beginif S='1' thenY(0)<=(not A(2)) and (not A(1)) and (not A(0));Y(1)<=(not A(2)) and (not A(1)) and A(0);Y(2)<=(not A(2)) and A(1) and (not A(0));Y(3)<=(not A(2)) and A(1) and A(0);Y(4)<=A(2) and (not A(1)) and (not A(0));Y(5)<=A(2) and (not A(1)) and A(0);Y(6)<=A(2) and A(1) and (not A(0));Y(7)<=A(2) and A(1) and A(0);else Y<="00000000";end if;end process;--控制单元--3-8译码器library ieee;use ieee.std_logic_1164.all;entity CU isport( m:in std_logic_vector(2 downto 0);t:in std_logic_vector(2 downto 0);d:in std_logic_vector(7 downto 0);q:out std_logic_vector(18 downto 0));end CU;architecture behave of CU issignal iq:std_logic_vector(7 downto 0);beginiq(0)<=not d(7) and not d(6) and not d(5) and not d(4) and not d(3) and not d(2) and not d(1) and d(0);iq(1)<=not d(7) and not d(6) and not d(5) and not d(4) and not d(3) and not d(2) and d(1) and not d(0);iq(2)<=not d(7) and not d(6) and not d(5) and not d(4) and not d(3) and d(2) and not d(1) and not d(0);iq(3)<=not d(7) and not d(6) and not d(5) and not d(4) and d(3) and not d(2) and not d(1) and not d(0);iq(4)<=not d(7) and not d(6) and not d(5) and d(4) and not d(3) and not d(2) and not d(1) and not d(0);iq(5)<=not d(7) and not d(6) and d(5) and not d(4) and not d(3) and not d(2) and not d(1) and not d(0);iq(6)<=not d(7) and d(6) and not d(5) and not d(4) and not d(3) and not d(2) and not d(1) and not d(0);iq(7)<=d(7) and not d(6) and not d(5) and not d(4) and not d(3) and not d(2) and not d(1) and not d(0);q(0)<=not m(2) and not m(1) and m(0) and not t(2) and not t(1) and t(0);q(1)<=(not m(2) and not m(1) and m(0) and not t(2) and not t(1) and t(0))or (not m(2) and m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(6));q(2)<=not m(2) and not m(1) and m(0) and not t(2) and t(1) and not t(0);q(3)<=not m(2) and not m(1) and m(0) and t(2) and not t(1) and not t(0);q(4)<=not m(2) and m(1) and not m(0) and not t(2) and not t(1) and t(0);q(5)<=not m(2) and m(1) and not m(0) and not t(2) and not t(1) and t(0);q(6)<=(not m(2) and m(1) and not m(0) and not t(2) and not t(1) and t(0) and iq(6)) or(m(2) and not m(1) and not m(0) and not t(2) and t(1) and not t(0) and (iq(0) or iq(5) or iq(6) or iq(7)));q(7)<=not m(2) and m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(6);q(8)<=not m(2) and m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(6);q(9)<=not m(2) and m(1) and not m(0) and t(2) and not t(1) and not t(0) and(iq(0) or iq(1) or iq(2) or iq(3) or iq(4));q(10)<=not m(2) and m(1) and not m(0) and t(2) and not t(1) and not t(0) and(iq(0) or iq(1) or iq(2) or iq(3) or iq(4));q(11)<=not m(2) and m(1) and not m(0) and t(2) and not t(1) and not t(0) and iq(6);q(12)<=m(2) and not m(1) and not m(0) and not t(2) and not t(1) and t(0) and iq(6);q(13)<=m(2) and not m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(1);q(14)<=m(2) and not m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(2);q(15)<=m(2) and not m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(3);q(16)<=m(2) and not m(1) and not m(0) and not t(2) and t(1) and not t(0) and iq(4);q(17)<=m(2) and not m(1) and not m(0) and t(2) and not t(1) and not t(0)and (iq(0) or iq(1) or iq(2) or iq(3) or iq(4) or iq(5) or iq(6));q(18)<=m(2) and not m(1) and not m(0) and t(2) and not t(1) and not t(0) and iq(7);--层次结构控制单元library ieee;use ieee.std_logic_1164.all;entity HCU isport( S:in std_logic;A:in std_logic_vector(2 downto 0);M:in std_logic_vector(2 downto 0);T:in std_logic_vector(2 downto 0);Q:out std_logic_vector(18 downto 0)); end HCU;architecture struct of HCU issignal i:std_logic_vector(7 downto 0);ponent decoder38port( S:in std_logic;A:in std_logic_vector(2 downto 0);Y:out std_logic_vector(7 downto 0)); end ponent;ponent CUport( m:in std_logic_vector(2 downto 0);t:in std_logic_vector(2 downto 0);d:in std_logic_vector(7 downto 0);q:out std_logic_vector(18 downto 0)); end ponent;beginG1:decoder38 port map(S=>S,A=>A,Y=>i);G2:CU port map(d=>i,t=>T,m=>M,q=>Q);end struct;四、仿真设计3-8译码器仿真设计:设计数据,输出3-8译码器的译码后的8种编码。