第5章 触发器

- 格式:ppt

- 大小:2.56 MB

- 文档页数:33

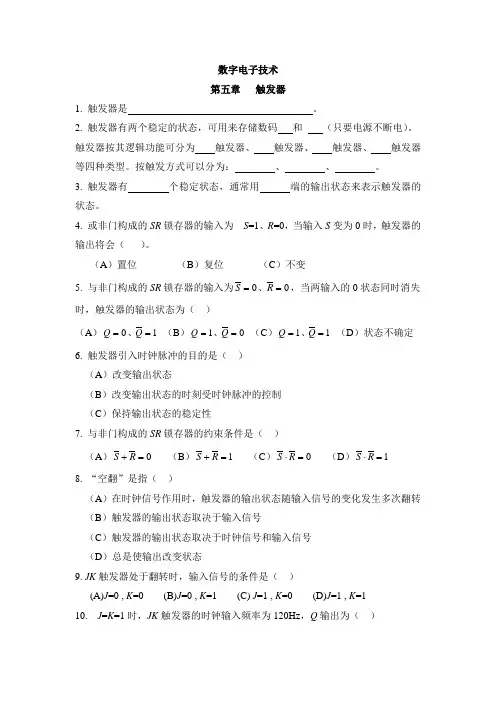

数字电子技术第五章 触发器1. 触发器是 。

2. 触发器有两个稳定的状态,可用来存储数码 和 (只要电源不断电)。

触发器按其逻辑功能可分为 触发器、 触发器、 触发器、 触发器等四种类型。

按触发方式可以分为: 、 、 。

3. 触发器有 个稳定状态,通常用 端的输出状态来表示触发器的状态。

4. 或非门构成的SR 锁存器的输入为 S =1、R =0,当输入S 变为0时,触发器的输出将会( )。

(A )置位 (B )复位 (C )不变5. 与非门构成的SR 锁存器的输入为0 0==R S 、,当两输入的0状态同时消失时,触发器的输出状态为( )(A )1 0==Q Q 、 (B )0 1==Q Q 、 (C )1 1==Q Q 、(D )状态不确定 6. 触发器引入时钟脉冲的目的是( )(A )改变输出状态(B )改变输出状态的时刻受时钟脉冲的控制(C )保持输出状态的稳定性7. 与非门构成的SR 锁存器的约束条件是( )(A )0=+R S (B )1=+R S (C )0=⋅R S (D )1=⋅R S8. “空翻”是指( )(A )在时钟信号作用时,触发器的输出状态随输入信号的变化发生多次翻转(B )触发器的输出状态取决于输入信号(C )触发器的输出状态取决于时钟信号和输入信号(D )总是使输出改变状态9. JK 触发器处于翻转时,输入信号的条件是( )(A)J =0 , K =0 (B)J =0 , K =1 (C) J =1 , K =0 (D)J =1 , K =110. J =K =1时,JK 触发器的时钟输入频率为120Hz ,Q 输出为( )(A)保持为高电平(B)保持为低电平(C)频率为60Hz的方波(D)频率为240Hz的方波*,则输入信号为()11. JK触发器在CP的作用下,要使QQ(A)J=K=0 (B)J=1 , K=0 (C)J=K=Q (D)J=0 , K=112. 下列触发器中,没有约束条件的是()(A)SR锁存器(B)主从JK触发器(C)钟控RS触发器13. 某JK触发器工作时,输出状态始终保持为1,则可能的原因有()(A)无时钟脉冲输入(B)J=K=1 (C)J=K=0 (D)J=1 , K=0 14. 归纳基本RS触发器、同步触发器、主从触发器和边沿触发器触发翻转的特点。

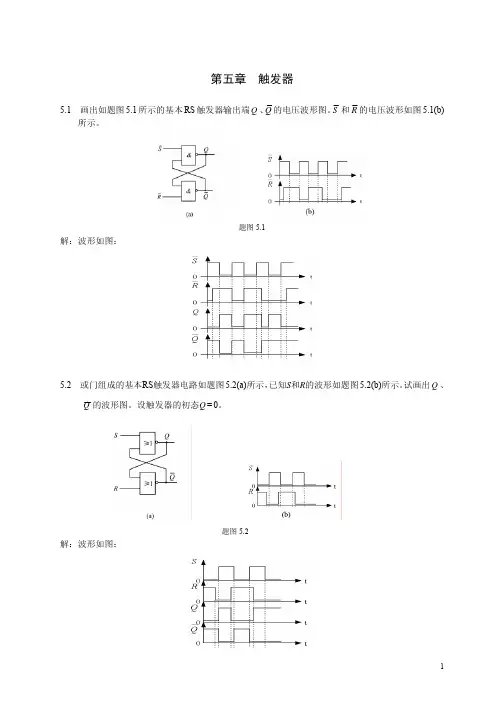

第五章触发器5.1 画出如题图5.1所示的基本RS触发器输出端、Q Q的电压波形图。

S和R的电压波形如图5.1(b)所示。

题图5.1解:波形如图:5.2 或门组成的基本RS触发器电路如题图5.2(a)所示,已知S和R的波形如题图5.2(b)所示。

试画出、Q Q的波形图。

设触发器的初态Q=0。

题图5.2解:波形如图:5.3 题图5.3所示为一个防抖动输出开关电路。

当拨动开关K时,由于开关接通瞬间发生振颤,R和S的波形如图中所示,请画出和Q Q端的对应波形。

题图5.3解:波形如图:5.4有一时钟RS触发器如题图5.4所示,试画出它的输出端的波形。

初态Q Q=0。

题图5.4解:波形如图:5.5 设具有异步端的主从JK 触发器的初始状态Q = 0,输入波形如题图5.5所示,试画出输出端Q 的波形。

题图5.5解:波形如图:5.6 设题图5.6的初始状态为2Q 1Q 0Q = 000,在脉冲CLK 作用下,画出、、的波形(所用器件都是CD4013)。

S 0Q 1Q 2Q D 、R D 分别是CD4013高电平有效的异步置1端,置0端。

题图5.6解:波形如图:5.7 设题图5.7电路两触发器初态均为0,试画出、波形图。

1Q 2Q题图5.7解:波形如图:5.8 已知CMOS 边沿触发结构JK 触发器CD4207各输入端的波形如题图5.8所示,试画出、Q Q 端的对应波形,设初态Q = 0。

S D 为高电平置1端,R D 为高电平置0端,电路为CLK 上升沿触发。

题图5.8解:波形如图:5.9 如题图5.9所示,利用CMOS 边沿触发器和同或门组成的脉冲分频器。

试分析它在一系列CLK脉冲作用下的、和Y 的波形(初始状态1Q 2Q 120Q Q ==)。

题图5.9解:波形如图:5.10 设题图5.10中各个触发器的初始状态皆为Q = 0,试画出每个触发器Q 端波形。

题图5.10解:波形如图:5.11 题图5.11示出了一个单稳态电路和它的工作波形,试分析其工作原理(初态Q=0)。