数字逻辑 第四章 触发器

- 格式:ppt

- 大小:1.16 MB

- 文档页数:52

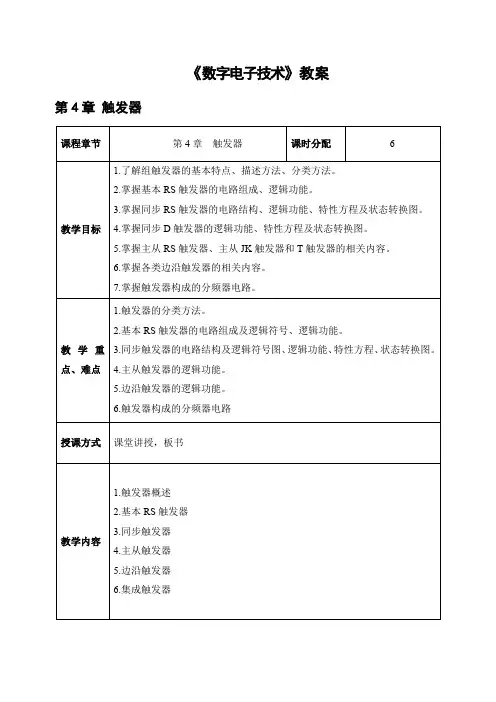

《数字电子技术》教案第4章触发器(a)电路结构(b)逻辑符号图4-1 与非门组成的基本RS触发器(1)当1Q=,0Q=时,称为触发器的1状态。

(2)当0Q=,1Q=时,称为触发器的0状态。

4.2.2基本RS触发器的逻辑功能如表4-1所示为基本RS触发器的特性表(逻辑功能表),其中新的稳定状态1n Q+不仅与输入信号有关,而且与触发器接收输入信号前的原状态n Q有关。

表4-1 “与非门”组成的基本RS触发器特性表R S现态n Q次态1n Q+说明0 001××状态不定,不允许0 1010置01 00111置11 10101保持原状态在基本RS触发器中,输入信号直接加在输出门上,所以输入信号在全部作用时间里(即S或R为0的全部时间),都能直接改变输出门Q或Q的状态。

(1)当0R =,1S =时,输出0Q =,R 端称为直接复位端。

(2)当0S =,1R =时,输出1Q =,S 端称为直接置位端。

4.3同步触发器4.3.1同步 R S 触发器只有在CP 端上出现时钟脉冲时,触发器的状态才能变化,此时触发器状态的改变与时钟脉冲同步,所以又称这类触发器为同步触发器。

如图4-2所示为同步RS 触发器的电路结构及逻辑符号图。

(a )电路结构 (b )逻辑符号图4-2 同步RS 触发器 与基本RS 触发器相比,同步RS 触发器增加了时钟控制端口,以实现对触发器状态转换的时间控制。

由图4-2(a )可知,该电路由两个部分组成,一个是由与非门1G ,2G 组成的基本触发器;另一个是在基本触发器的基础上多加两个与非门3G ,4G 组成的输入控制电路。

其中,3G ,4G 是由时钟脉冲CP 控制的,具有时钟脉冲控制的触发器又称为时钟触发器。

图4-2(a )所示的时钟脉冲为高电平有效,即触发器在CP 1=期间接收输入信号,在CP 0=时状态保持不变。

1.同步RS 触发器的逻辑功能(1)当CP 0=时,3G 和4G 被封锁,不管R 端和S 端的信号如何变化,输出都为1,触发器保持原状态不变,即1n n Q Q +=。

《数字逻辑与电路》复习题第一章数字逻辑基础(数制与编码)一、选择题1.以下代码中为无权码的为CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为 B 。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是CD 。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数(53.5)10等值的数或代码为ABCD 。

A. (0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与八进制数(47.3)8等值的数为:A B。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常用的BC D码有C D 。

A.奇偶校验码B.格雷码C.8421码D.余三码二、判断题(正确打√,错误的打×)1. 方波的占空比为0.5。

(√)2. 8421码1001比0001大。

(×)3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(√)4.格雷码具有任何相邻码只有一位码元不同的特性。

(√)5.八进制数(17)8比十进制数(17)10小。

(√)6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

(√)7.十进制数(9)10比十六进制数(9)16小。

(×)8.当8421奇校验码在传送十进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

(√)三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用1和0来表示。