数电各章习题全解第5章习题作业

- 格式:ppt

- 大小:2.33 MB

- 文档页数:43

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解CP Q0 Q1Q2Q30 0 0 0 11 1 0 0 02 0 1 0 03 0 0 1 04 0 0 0 1 时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解CP Q0 Q1 Q20 0 0 01 1 0 02 0 1 03 0 0 14 0 0 05-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

CP Q1 Q2Q30 0 0 01 1 0 02 0 1 03 1 1 04 0 0 15 0 0 0 该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

(2)若令K3= 1,电路为几进制计数器,画出其状态图。

解:(1CP Q1 Q2Q30 1 2 3 4 5 6 7 0 0 01 0 00 1 01 1 00 0 11 0 1 0 1 1 0 0 0为7进制计数器CP Q1 Q2Q30 1 2 3 4 5 0 0 01 0 00 1 01 1 00 0 11 0 0为4进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q1 Q2Q3Z0 1 2 3 4 5 6 7 0 1 0 0 0 01 0 1 0 1 1 1 00 1 1 11 0 0 0 1 1 0 00 1 0 01 0 1 00 0 1 01 0 0 0该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q4 Q3Q2Q11234 567111111111 0 0 0 00 0 0 11 0 0 11 1 0 11 1 1 00 1 1 11 0 1 11 1 0 10 0 1 00 0 0 10 0 1 11 0 0 10 1 0 00 0 1 10 1 0 11 0 1 10 1 1 00 0 1 11 0 0 00 1 0 11 0 1 00 1 0 11 1 0 00 1 1 11 1 1 1 1 1 1 0由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。

第5章 组合逻辑电路应用习题55.1 设计一个10线-4线编码器,输出为8421BCD 码。

解:设输入9I ,8I …0I 分别表示十进制数码9,8…0,输出3Y ,2Y ,1Y ,0Y 分别表示8421BCD 码的4个二进制位。

输入低电平有效的编码器真值表如下: 得到最简逻辑函数为:893Y =I +I 89=I I 27654Y I I I I = 17632Y I I I I = 5.2 试用线-3的2101Y Y Y ===,31EX Z Y ==,0F Y =,导致1U 对76,A A 进行优先编码,且与门的输出为1U 的编码输出,所以,3210Z Z Z Z 的值在1000—1111之间,1F Z =。

5.3 试分析图P5.3所示电路的功能(74148为8线-3线优先编码器)。

解:由题知0EI =当2A ,3A ...9A 中有逻辑0时,则:则1U 对它们进行优先编码,且1U 的1F Y =,导致2U 的输出全为1,与门的输出为1U 的编码输出,所以3L 2L 1L 0L 的值在0000—0111之间,1F Y =。

如果2A ,3A ...9A 全为逻辑1,则1U 的2101Y Y Y ===,31EX L Y ==,0F Y =,导致2U 对10,A A 进行优先编码,且与门的输出为2U 的编码输出,所以,3L 2L 1L 0L 的值在1000—1111之间,1F Y =。

5.4 分析图P5.4所示电路的功能。

解: 102L Y Y =∙ 23567L Y Y Y Y =∙∙∙ 即1L ABC ABC AC =+= 2L ABC ABC ABC ABC AC AB BC =+++=++74138译码器能实现函数1L AC = 2L AC AB BC =++的功能。

5.5 用2片3线-8线译码器74138,组成4线-16线译码器。

图P5. 4图P5.33 当0EN =时,编码器对输入位号进行编码30Y = 891I I ==,相当于一个输出加上非门的8线-3线优先编码器,按765I I I …0I 的优先级数,对应的输出二进制代码依次为111,110,101…000,所以当时的输出二进制代码依次为0111,0110,0101…0000。

[题5.1] 分析图P5.1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

画出电路的状态转换图,说明电路能否自启动。

答案:答案:11322131233;J K QJ K Q J Q Q K Q ì==ï==íï==î3Y Q =电路能自启动。

状态转换图如图A5.1。

[题5.7] 在图P5.7电路中,若两个移位寄存器中的原始数据分别为A 3 A 2 A 1 A 0=1001,B 3 B 2 B 1 B 0=0011,试问经过4个CP 信号作用以后两个寄存器中的数据如何?这个电路完成什么功能?成什么功能?答案:经过四个时钟信号作用以后,两个寄存器里的数据分别为:A 3 A 2 A 1 A 0=1100,B 3B 2B 1 B 0=0000。

这是一个四位串行加法计数器。

这是一个四位串行加法计数器。

[题5.8] 分析图P5.8的计数器电路,说明这是多少进制的计数器。

十进制计数器74160的功能表见表5.3.4。

答案:答案:电路为七进制计数器。

图P5.8电路为七进制计数器。

[题5.9] 分析图P5.9的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。

十六进制计数器74LS161的功能表见表5.3.4。

答案:答案:。

这是一个十进制计数器。

电路的状态转换图如图A5.9。

这是一个十进制计数器。

[题5.10] 试用4位同步二进制计数器74LS161接成十二进制计数器,标出输入、输出端。

可以附加必要的门电路。

74LS161的功能表见表5.3.4。

答案:答案:见图A5.10 [题5.11] 试分析图P5.11的计数器在M=1和M=0时各为几进制。

74160的功能表见表5.3.4。

答案:答案:M=1时为六进制计数器,M=0时为八进制计数器。

时为八进制计数器。

[题5.16] 图P5.16电路是由两片同步十进制计数器74160组成的计数器,试分析这是多少进制的计数器,两片之间是几进制。

第五章锁存器和触发器

1、1n n Q S RQ +=+, 0SR =

2、n

Q , 0 3、32

4、T

7、

A B

J

4-13题解图

8、

D=B A ⊕

第六章时序逻辑电路

1、输入信号,原来的状态

2、异

3、n

4、4,4

5、反馈清零、反馈置数

6、N

7、状态方程和输出方程:

8、激励方程

状态方程

输出方程

Z=AQ1Q0

根据状态方程组和输出方程可列出状态表,如表题解6.2.4所示,状态图如图题解6。

2.4所示。

14、

15、状态方程为:

24、解:74HC194功能由S1S0控制

00 保持,01右移10 左移11 并行输入

当启动信号端输人一低电平时,使S1=1,这时有S。

=Sl=1,移位寄存器74HC194执行并行输人功能,Q3Q2Q1Q0=D3D2D1D0=1110。

启动信号撤消后,由于Q。

=0,经两级与非门后,使S1=0,这时有

S1S0=01,寄存器开始执行右移操

作。

在移位过程中,因为Q3Q2、

Q1、Q0中总有一个为0,因而能

够维持S1S0=01状态,使右移操作

持续进行下去。

其移位情况如图题

解6,5,1所示。

该电路能按固定的时序输出低电平

脉冲,是一个四相时序脉冲产生电

路。

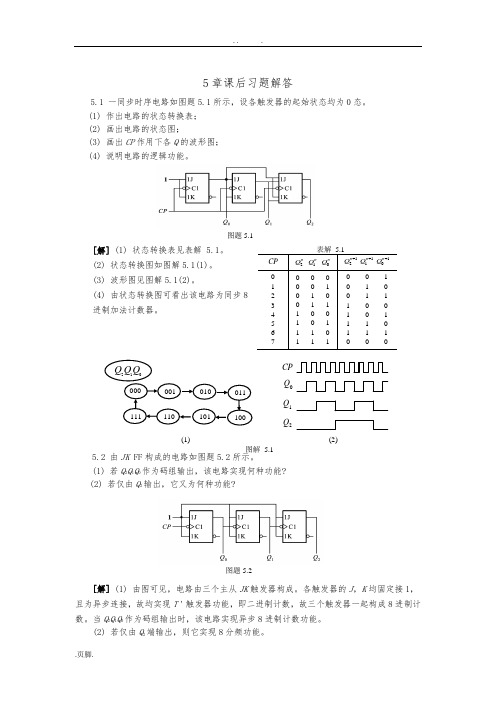

5章课后习题解答5.1 一同步时序电路如图题5.1所示,设各触发器的起始状态均为0态。

(1) 作出电路的状态转换表;(2) 画出电路的状态图;(3) 画出CP作用下各Q的波形图;(4) 说明电路的逻辑功能。

[解] (1) 状态转换表见表解 5.1。

(2) 状态转换图如图解5.1(1)。

(3) 波形图见图解5.1(2)。

(4) 由状态转换图可看出该电路为同步8进制加法计数器。

5.2 由JK FF构成的电路如图题5.2所示。

(1) 若Q2Q1Q0作为码组输出,该电路实现何种功能?(2) 若仅由Q2输出,它又为何种功能?[解] (1) 由图可见,电路由三个主从JK触发器构成。

各触发器的J,K均固定接1,且为异步连接,故均实现T'触发器功能,即二进制计数,故三个触发器一起构成8进制计数。

当Q2Q1Q0作为码组输出时,该电路实现异步8进制计数功能。

(2) 若仅由Q2端输出,则它实现8分频功能。

图题5.1图题5.2000 001 010 011111 110 101 100QQQ12CPQQ1Q2(1) (2)图解 5.1CP210n n nQ Q Q+1+1+1210n n nQ Q Q12345670 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 10 0 10 1 00 1 11 0 01 0 11 1 01 1 10 0 05.3 试分析图题5.3所示电路的逻辑功能。

[解] (1) 驱动程式和时钟方程02nJ Q =,01K =;0CP CP = 111J K ==;01CP Q =210n nJ Q Q =,21K =;2CP CP = (2) 将驱动方程代入特性方程得状态方程0+1000020 ()n n n n nQ J Q K Q Q Q CP =+=+1111 ()n n Q Q CP =+12210 ()n n n n Q Q Q Q CP =(3) 根据状态方程列出状态转换真值表(4) 作状态转换图(5) 逻辑功能:由状态转换图可见该电路为异步5进制计数器。

自我检查题5.1 时序电路和组合电路的根本区别是什么?同步时序电路与异步时序电路有何不同?解答:从功能上看,时序电路任何时刻的稳态输出不仅和该时刻的输入相关,而且还决定于该时刻电路的状态,从电路结构上讲,时序电路一定含有记忆和表示电路状态的存储器。

而组合电路任何时刻的稳态输出只决定于该时刻各个输入信号的取值,由常用门电路组成则是其电路结构的特点。

在同步时序电路中,各个触发器的时钟信号是相同的,都是输入CP 脉冲,异步时序电路则不同,其中有的触发器的时钟信号是输入cp 脉冲,有的则是其他触发器的输出,前者触发器的状态更新时同步的,后者触发器状态更新有先有后,是异步的。

5.2 画出图T5.2所示电路的状态和时序图,并简述其功能。

图T5.2解:(1)写方程式 驱动方程 nQ K J 200==n Q K J 011==n n Q Q J 012=, n Q K 22=输出方程:nQ Y 2= (2) 求状态方程nn n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 02020202000010+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01011010111111+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01222201222212=+=+=+(3)画状态图和时序图 状态图如下图所示:101时序图如下图所示:CP Q 0Q 1Q 25.3 试用边沿JK 触发器和门电路设计一个按自然态序进行计数的七进制同步加法计数器。

解:(1)状态图如下图:(2)求状态方程、输出方程CQ Q Q n n n /101112+++的卡诺图如下图所示:输出方程为nn Q Q C 12=状态方程:n n n n n Q Q Q Q Q 120112+=+ n n n n n n Q Q Q Q Q Q 0120111+=+ n n n n n Q Q Q Q Q 120110+=+驱动方程:n n n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 0122120121220112)(++=++=+n n n n n n Q Q Q Q Q Q 1021011+=+n n n n n Q Q Q Q Q 0012101)(++=+与JK 触发器的特性方程 比较,可以得到驱动方程 n n Q Q J 012= 、 n Q K 12=n Q J 01= 、n n Q Q K 021=n n n n Q Q Q Q J 12120=+= 10=K(4) 无效状态转换情况 111/1000 能自启动(5) 逻辑图如下图所示:5.4 画出用时钟脉冲上升沿触发的边沿D 触发器组成的4位二进制异步加法计数器和减法计数器的逻辑电路图。

第五章习题1.题图5-1所示电路是用两片555组成的脉冲发生器,试画出Y 1和Y 2两处的输出波形,并标注要紧参数(参数只需估算)。

R 1C 133kR 233k 10题图5-12.题图5-2所示的555按时器组成的单稳态触发器及输入v I 的波形,求: (1)输出信号v O 的脉冲宽度T W ;(2)对应v I 画出v C 、v O 的波形,并标明波形幅度。

v I /V CC /3v Iv O题图5-23.由555按时器组成的多谐振荡器如图5-3所示,已知V DD =12V 、C =μF、R 1=15k Ω、R 2=22k Ω。

试求:(1)多谐振荡器的振荡周期;(2)画出的v C 和v O 波形。

v O /Vv C /V00tR Cv v OR题图5-34.由555按时器、3位二进制加计数器、理想运算放大器A 组成如题图5-4所示电路。

设计数器初始状态为000,且输出低电平V OL =0 V ,输出高电平V OH = V ,R d 为异步清零端,高电平有效。

(1)说明虚框(1)、(2)部份各组成什么功能电路?(2)虚框(3)组成几进制计器? (3)对应CP 画出v O 波形,并标出电压值。

题图5-45.用集成芯片555组成的施密特触发器电路及输入波形i v 如题图5-5所示,要求: (1)求出该施密特触发器的阈值电压V T +、V T -;(2)画出输出v o 的波形。

v I /V tv O /Vv v O题图5-56.用集成按时器555组成的电路及可产生的波形如题图5-6(a )、(b )所示,试回答: (1)该电路的名称;(2)指出(b )图中v C 波形是1~8引脚中,哪个引脚上的电压波形; (3)求出矩形波的宽度t W 。

v Iv O 0.3v v(a ) (b )题图5-67.题图5-7为简易门铃电路,设电路中元器件参数适合,R >>R 1,S 为门铃按钮,当按钮按一下放开后,门铃可响一段时刻。

思考题与习题5-1 在如图5-1所示的四位移位寄存器中,假定开始时Q3Q2Q1Q0为1101状态。

若串行输入序列101101与CP脉冲同步地加在D SR串行输入端时,请对应画出各触发器Q 3Q2Q1Q端的输出波形。

图T5-15-2 图T5-2电路中各触发器的初始状态均为0,请对应输入CP和IN的波形,画各触发器Q端的输出波形。

图T5-25-3 试用两片74LS194电路构成一个八位移位寄存器,并画出逻辑电路图。

5-4 请用上升沿触发的D触发器构成一个异步三位二进制加法计数器。

并对应CP画出Q1、Q2、Q3的波形。

图T5-45-5 请用JK 触发器构成一个脉冲反馈式异步六进制加法计数器,并画出对应于CP 脉冲的工作波形。

图T5-5用三位JK 触发器构成八进制计数器,然后在状态110时利用与非门反馈至清零端构成六进制计数器,图略。

5-6请分析如图T5-6所示的阻塞反馈式异步计数器电路的逻辑功能,指出该计数器为几进制,并画出计数状态转换图。

图T5-6解:(1)驱动方程:J I =3Q ,K 1=1; J 2=1,K 2=1;J 3=nQ n Q 21,K 3=1;代入得状态方程: (CP 脉冲下降沿时刻)(Q 1下降沿时刻) (CP 脉冲下降沿时刻)列出状态转换图(略)分析得出该计数器为5进制计数器,状态从000-100,其它的三个状态下一状态均为000,因此该电路是异步五进制计数器,具有自启动功能。

5-7 分析图T5-7同步计数器电路的逻辑功能。

图T5-7nn n n n Q K ,Q J Q K ,Q J Q K ,J 232312323111====== n Q n Q Q n 1311=+n Q Q n 221=+n Q n Q n Q Q n 31231=+nn n nn n nn n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 23232132123123113111=⋅+⋅=⋅+⋅=+=⋅+=+++n n n Q Q Q 123 111213+++n n n Q Q Q0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 1 0 1 1 1 1 0 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 1因为该计数器设计了清零端,因此可实现从000开始进入循环圈的2进制计数器的功能,但我们也发现,它也可以实现三进制。

第五章(时序逻辑电路)作业1、时序逻辑电路如图5-1所示,试分析该电路的逻辑功能。

要求:写出电路的激励方程、状态方程和状态转换表,画出电路的状态转换图,并说明电路能否自启动。

图5-1 时序逻辑电路2、试用文字语言描述图5-2所示状态图的状态变化情况,并写出其相应的状态转换表。

.ABCD0/10/00/00/01/01/01/01/1....图5-2 状态图3、图5-3所示的是5位右移寄存器与输入信号DATA 、时钟CLK 的波形图,设寄存器初始状态为00000,试画出寄存器输出Q 4~Q 0的波形图。

110105位右移寄存器DATACLKDATACLK...Q Q Q Q Q 01234高位移位输出..图5-3 5位右移寄存器与DATA 、CLK 的波形图4、试用JK 触发器设计一个同步八进制计数器,其状态S 0、S 1…S 7的编码分别为000、001、011、010、110、111、101、100。

5、试用上升沿JK 触发器构成异步3位二进制加法计数器,要求画出逻辑电路图,以及计数器输入时钟CLK 与JK 触发器输出端Q 2~Q 0的波形图。

6、图5-4所示为异步4位二进制加法计数器74LS293组成的计数器电路,试说明该计数电路是多少进制计数器,并说明复位信号RESET 的有效电平,R0(1)12R0(2)1310911548A B A B C DCK CK Q Q Q Q 74L S293&1≥CLKRESET....图5-4 74LS293组成的计数器电路7、试用74LS161连接成计数长度M=8的计数器,可采用几种方法?并画出相应的接线图。

8、试用2片74LS161组成十二进制计数器,要求计数值为1~12。

9、试分析图5-5所示时序逻辑电路为多少进制计数器,是同步电路还是异步电路。

图5-5 计数器电路10、图5-6是一个地下车库入库车辆数量统计、显示装置的逻辑电路图,该地下车库可以停放99辆车,在入口处和出口处分别安装有车辆传感器用于检测车辆的进入和驶出,该装置可以实时显示车库内停放车辆的数量。

第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。

解CP Q0 Q1Q2Q30 0 0 0 11 1 0 0 02 0 1 0 03 0 0 1 04 0 0 0 1 时序图:CPQ0Q1Q2Q35-2分析题5-2图所示电路,画出电路的状态图。

解CP Q0 Q1 Q20 0 0 01 1 0 02 0 1 03 0 0 14 0 0 05-3 JK触发器组成5-3图所示电路。

分析该电路为几进制计数器,并画出电路的状态图。

CP Q1 Q2Q30 0 0 01 1 0 02 0 1 03 1 1 04 0 0 15 0 0 0 该电路为五进制计数器5-4JK触发器促成如图5-4图所示的电路。

(1)分析该电路为几进制计数器,画出状态图。

(2)若令K3= 1,电路为几进制计数器,画出其状态图。

解:(1CP Q1 Q2Q30 1 2 3 4 5 6 7 0 0 01 0 00 1 01 1 00 0 11 0 1 0 1 1 0 0 0为7进制计数器CP Q1 Q2Q30 1 2 3 4 5 0 0 01 0 00 1 01 1 00 0 11 0 0为4进制计数器5-5 试画出题5-5图(a)所示电路中B,C端的波形。

输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19CPAQ0Q1BC5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q1 Q2Q3Z0 1 2 3 4 5 6 7 0 1 0 0 0 01 0 1 0 1 1 1 00 1 1 11 0 0 0 1 1 0 00 1 0 01 0 1 00 0 1 01 0 0 0该电路能够自启动5-7 分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。

CP Q4 Q3Q2Q11234 567111111111 0 0 0 00 0 0 11 0 0 11 1 0 11 1 1 00 1 1 11 0 1 11 1 0 10 0 1 00 0 0 10 0 1 11 0 0 10 1 0 00 0 1 10 1 0 11 0 1 10 1 1 00 0 1 11 0 0 00 1 0 11 0 1 00 1 0 11 1 0 00 1 1 11 1 1 1 1 1 1 0由状态图可见,电路图能够自启动5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。