数字集成电路习题

- 格式:pdf

- 大小:824.43 KB

- 文档页数:16

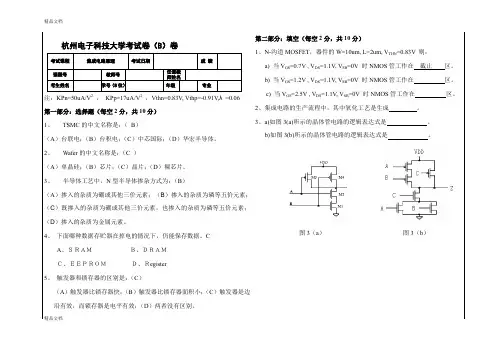

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷B姓名 学号 班级 任课教师一、填空题(本大题共10小题,每空格1分,共10分)请在每小题的空格中填上正确答案。

错填、不填均无分。

1.(1011111.01)2=( )102.若10010110是82421BCD 码的一组代码,则它对应的十进制数是________。

3.逻辑函数B A AB F +=的反函数F =________。

4.不会出现的变量取值所对应的最小项叫做 。

5.组合逻辑电路任何时刻的稳定输出仅仅只决定于__________各个输入变量的取值。

6.描述时序逻辑电路的逻辑表达式有驱动方程、________________和输出方程。

7.1K ×4位ROM ,有 位地址输入。

8.要把模拟量转化成数字量一般要经过四个步骤,分别称为采样、保持、________、编码。

9.D/A 转换器的主要参数有 、转换时间和转换精度。

10.集成单稳态触发电路的暂稳态维持时间取决于 。

二、选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

11.若已知Y XY YZ Z Y XY +=++,判断等式=+++))()((Z Y Z Y Y X Y Y X )(+成立的最简单方法是依据 规则。

【 】A .代入规则B .对偶规则C .反演规则D .互补规则12.F (A ,B ,C )的任意两个最小项之积等于 。

【 】 A .0 B .1 C .ABC D .ABC13.+0+1A A A ⋅⋅等于 。

【 】 A .0 B .1 C . A D .A 14.将TTL 与非门正常使用时,多余的输入端应 。

【 】 A .全部接高电平 B .部分接高电平,部分接地 C .全部接地 D .部分接地,部分悬空 15. S R 触发器不具有 功能。

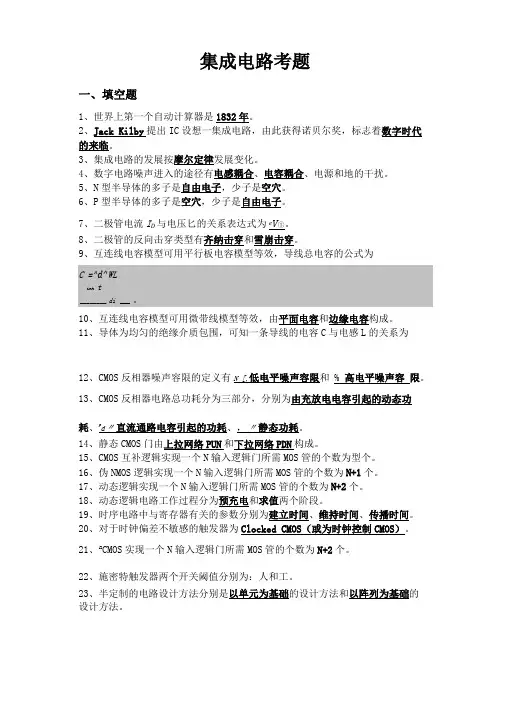

集成电路考题一、填空题1、世界上第一个自动计算器是1832年。

2、Jack Kilby提出IC设想一集成电路,由此获得诺贝尔奖,标志着数字时代的来临。

3、集成电路的发展按摩尔定律发展变化。

4、数字电路噪声进入的途径有电感耦合、电容耦合、电源和地的干扰。

5、N型半导体的多子是自由电子,少子是空穴。

6、P型半导体的多子是空穴,少子是自由电子。

7、二极管电流I D与电压匕的关系表达式为e V①。

8、二极管的反向击穿类型有齐纳击穿和雪崩击穿。

9、互连线电容模型可用平行板电容模型等效,导线总电容的公式为10、互连线电容模型可用微带线模型等效,由平面电容和边缘电容构成。

11、导体为均匀的绝缘介质包围,可知一条导线的电容C与电感L的关系为12、CMOS反相器噪声容限的定义有N [,低电平噪声容限和 %高电平噪声容限。

13、CMOS反相器电路总功耗分为三部分,分别为由充放电电容引起的动态功耗、P d〃直流通路电容引起的功耗、,〃静态功耗。

14、静态CMOS门由上拉网络PUN和下拉网络PDN构成。

15、CMOS互补逻辑实现一个N输入逻辑门所需MOS管的个数为型个。

16、伪NMOS逻辑实现一个N输入逻辑门所需MOS管的个数为N+1个。

17、动态逻辑实现一个N输入逻辑门所需MOS管的个数为N+2个。

18、动态逻辑电路工作过程分为预充电和求值两个阶段。

19、时序电路中与寄存器有关的参数分别为建立时间、维持时间、传播时间。

20、对于时钟偏差不敏感的触发器为Clocked CMOS(或为时钟控制CMOS)。

21、C2CMOS实现一个N输入逻辑门所需MOS管的个数为N+2个。

22、施密特触发器两个开关阈值分别为:人和工。

23、半定制的电路设计方法分别是以单元为基础的设计方法和以阵列为基础的设计方法。

二、简答题 1、画出双阱CMOS电路工艺顺序简化图。

(P31)2、二极管的电流受工作温度的双重影响。

(P60)(1)出现在电流方程的①T与温度呈线性关系,①T的增加会使电流下降。

1、在数字集成电路中,以下哪个元件常用于存储二进制信息?A、电阻B、电容C、触发器D、电感(答案:C)2、模拟集成电路中,用于放大电信号的主要元件是?A、二极管B、晶体管C、电阻D、电容(答案:B)3、以下哪种逻辑门电路可以实现“与”运算?A、NOT门B、OR门C、AND门D、XOR门(答案:C)4、在数字电路中,时钟信号的主要作用是?A、提供电源B、控制信号同步C、放大信号D、转换信号格式(答案:B)5、模拟集成电路中,常用于稳定输出电压的元件是?A、运算放大器B、比较器C、稳压二极管D、晶体管(答案:C)6、数字集成电路中,D触发器的输出在何时更新?A、时钟信号上升沿B、时钟信号下降沿C、随时更新D、根据输入信号变化(答案:A,注:也可能是B,具体取决于触发器类型,但此题通常按常见上升沿触发考虑)7、以下哪种电路常用于将模拟信号转换为数字信号?A、放大器B、滤波器C、模数转换器(ADC)D、数模转换器(DAC)(答案:C)8、在模拟集成电路中,用于产生稳定电流源的元件或电路是?A、电流镜B、电压源C、电阻网络D、电容器(答案:A)9、数字集成电路中,用于实现计数功能的电路是?A、加法器B、寄存器C、计数器D、译码器(答案:C)10、以下哪种电路或元件在模拟集成电路中常用于信号的滤波?A、放大器B、比较器C、滤波器D、振荡器(答案:C)。

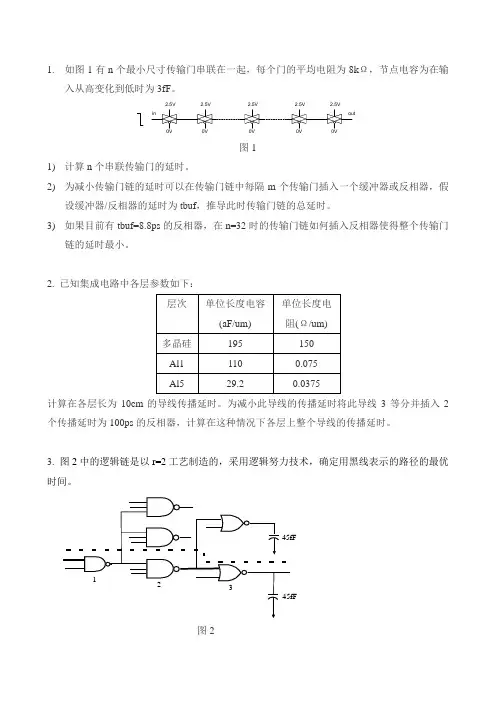

1.如图1有n个最小尺寸传输门串联在一起,每个门的平均电阻为8kΩ,节点电容为在输入从高变化到低时为3fF。

图11)计算n个串联传输门的延时。

2)为减小传输门链的延时可以在传输门链中每隔m个传输门插入一个缓冲器或反相器,假设缓冲器/反相器的延时为tbuf,推导此时传输门链的总延时。

3)如果目前有tbuf=8.8ps的反相器,在n=32时的传输门链如何插入反相器使得整个传输门链的延时最小。

2. 已知集成电路中各层参数如下:计算在各层长为10cm的导线传播延时。

为减小此导线的传播延时将此导线3等分并插入2个传播延时为100ps的反相器,计算在这种情况下各层上整个导线的传播延时。

3.图2中的逻辑链是以r=2工艺制造的,采用逻辑努力技术,确定用黑线表示的路径的最优时间。

图24.画出用于计算图3所示逻辑电路的开关时间模型,并给出上升时间和下降时间表达式。

假设所有管子的宽长比都一样。

ac图35.已知集成电路中Al5层参数如下:单位长度电容32 aF/um;单位长度电阻0.035Ω/um。

计算在该层长为12cm的导线传播延时。

为减小此导线的传播延时将此导线3等分并插入2个传播延时为80ps的反相器,计算在这种情况下各层上整个导线的传播延时。

6.将一个NMOS器件如图1所示放入测试配置装置,输入电压为Vin=2V,电流源为固定电流50μA,R为一个可变电阻,在10kΩ和30 kΩ之间变化,M1有短沟道效应,具体已知参数:k’ = 110*10-6 V/A2,VT = 0.4,VDSAT = 0.6V,W/L = 2.5μ/0.25μ,为了简单起见,体效应和沟道长度调制忽略,即λ=0, γ=0。

当R=10kΩ时,晶体管所处的工作区,求解VD 和VS。

图4. 测试配置装置7.将一个NMOS器件如图1所示放入测试配置装置,输入电压为Vin=2V,电流源为固定电流50μA,R为一个可变电阻,在10kΩ和30 kΩ之间变化,M1有短沟道效应,具体已知参数:k’ = 110*10-6 V/A2,VT = 0.4,VDSAT = 0.6V,W/L = 2.5μ/0.25μ,为了简单起见,体效应和沟道长度调制忽略,即λ=0, γ=0。

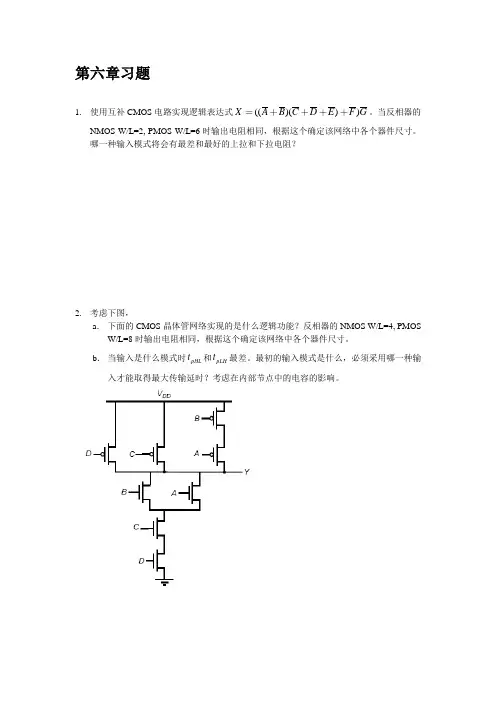

第六章习题

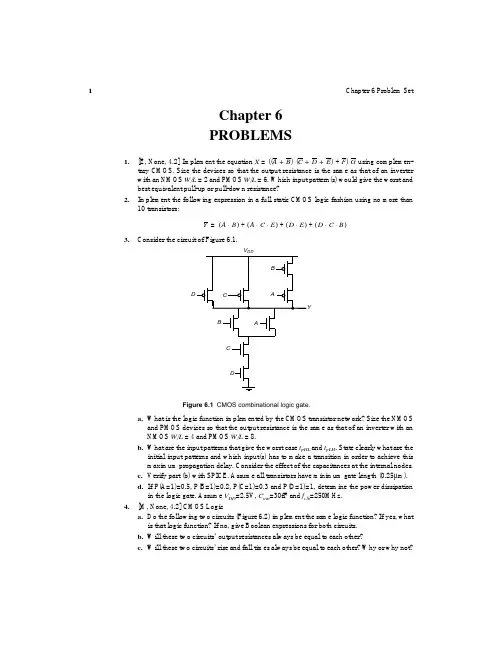

1. 使用互补CMOS 电路实现逻辑表达式(()())X A B C D E F G 。

当反相器的NMOS W/L=2, PMOS W/L=6时输出电阻相同,根据这个确定该网络中各个器件尺寸。

哪一种输入模式将会有最差和最好的上拉和下拉电阻?

2. 考虑下图,

a . 下面的CMOS 晶体管网络实现的是什么逻辑功能?反相器的NMOS W/L=4, PMOS W/L=8时输出电阻相同,根据这个确定该网络中各个器件尺寸。

b . 当输入是什么模式时pHL t 和pLH t 最差。

最初的输入模式是什么,必须采用哪一种输入才能取得最大传输延时?考虑在内部节点中的电容的影响。

3.CMOS组合逻辑

a.下图中的两个电路A和B是否实现同一个逻辑函数?如果是的话,是什么逻辑;

如果不是的话,给出两个电路的布尔表达式。

b.这两个电路的输出电阻是否总是相同?分析解释。

c.这两个电路的上升下降时间是否总是相同?分析解释。

数字集成电路设计期末考试浙江大学一.单选题1、以下编码中为有权码的是()A、ASCII码B、余3码C、5421BCD码D、右移码余3码与8421BCD码都只有9个2、二进制数11000110对应的格雷码是()A、11100010B、10100101C、11011001D、10010101二进制——格雷码(循环码,任意两个相邻码之间只有一位不同):a.最高位不变;b.二进制的后一位与前一位异或的到格雷码的下一位格雷码——二进制:a.最高位不变;b.高位二进制码于次高位格雷码异或得到二进制的下一位3、若字长为8,带符号数-10011的补码是()。

A、11101100B、11101101C、11001100D、11001101符号位0正1负,符号位加上字长一共有6位,在除去符号位的最高位补上0凑够8位,则源码为10010011,符号位不变,其余位取反加一后为11101101。

正数的原码=反码=补码4、十进制数76所对应的8421BCD码是()。

A、01001100B、00111001C、01111001D、011101107对应0111,6对应01105、余3码10010101对应的二进制数是()。

A、10100011B、10010010C、00111110D、01100010余3码1001对应6,0101对应2,即62,62用除二取余算出其对应的二进制数为111110,前面补零即为C6、余3码10010101转换成8421码是()。

A、00111110B、01100010C、01010011D、100100101001(十进制为9)减0011(3)为0110(6),同,即为B7、对二进制数100101,若采用偶校验,则校验位上应该填()。

A、0B、1奇校验:使信息位和校验位中“1”的个数共计为奇数;偶校验:使信息位和校验位中“1”的个数共计为偶数。

奇偶校验码只能找错不能纠错,只能发现单错不能发现双错。

数字集成电路练习题一、填空题1.微波迈克尔逊干涉仪的半反镜可用____________、____________、____________等材料制作,实验中未用补偿板,是因为____________。

微波是波长在____________至____________范围内的电磁波,若微波实验中用的固定输出的的信号发生器,实验时用____________来调节____________。

2.由于微波频率较高,它的传输要采用____________或____________,微波测量的基本参量有____________、____________等。

3.单位体积内物体的质量称为物体的____________。

4.物理实验中常用的基本方法:____________、交换法、____________、_________、转换测量法、光学测量法。

5.测量可分为直接测量和____________。

6.相对论效应实验中,采用___________验证物体高速运动的_________与__________关系。

7.低温温度的测量一般可用___________、___________、__________测量。

_________温度计是负温度系数的。

8.高温超导材料的临界温度一般约在________以上。

超导材料的物理特性是_________、____________。

9.在速调管内电场和磁场作____________振荡,它们的位相差为____________。

微波在波导管中传输的波长,称为___________波长,它与波导宽度____________关。

10.检波晶体、二极管的伏安特性是非线性的,其电流I与探针所在处电场强度E的关系式为____________。

11.β粒子与物质作用,其单能峰的____________、____________均发生变化。

而γ射线与物质相互作用,____________变化,____________不变。

课时4数字集成电路一、基础巩固篇1.下列对于MOS管的描述,不恰当...的是()A.MOS管属于电压控制元件B.栅极G用来控制导通与截止C.漏极D通常接地D.MOS管作为开关时工作在截止与导通状态2.数字集成电路有多种类型,最常用的有TTL和CMOS两种,它们各有优缺点,适用于不同的场合中。

下列不是..TTL电路优点的是()A.速度快B.允许负载流过的电流较大C.抗静电能力强D.功耗小3.下列有关如图所示的数字集成电路芯片的说法中,正确的是()A.该芯片的名称是双4输入与门B.7脚接电源正极,14脚接地C.该芯片能实现或逻辑关系D.如果工作的电压为12 V,则该芯片为CMOS型电路4.如图所示是CT74LSO4集成芯片引脚图,共有____个门电路,每个门电路有____个输入端、____个输出端。

横线上分别应该填()A.6、6、6B.6、1、1C.1、6、6D.1、1、15.晶体管电路如图所示,请完成以下任务:(1)三极管型号是________(在①NPN型;②PNP型中选择合适的选项,将序号填写在“______”处);(2)将开关断开,LED1和LED2分别为________和________(在①熄灭;②点亮中选择合适的选项,将序号填写在“________”处);将开关闭合,LED1和LED2分别为______和______(在①熄灭;②点亮中选择合适的选项,将序号填写在“______”处);(3)开关闭合时,三极管基极和发射极之间的电压为__________ V,三极管处于__________状态(在①饱和;②截止中选择合适的选项,将序号填写在“________”处);集电极和发射极之间________(在①导通;②截止中选择合适的选项,将序号填写在“______”处),LED2被________(在①短路;②开路中选择合适的选项,将序号填写在“______”处)。

二、素养提升篇1.如图所示是数字集成电路CC4001引脚排列及功能图,在实际使用中,下列说法中不正确...的是()A.该集成电路是TTL类型B.如果电路中只需用一个或非门,可任选其中一组C.把其中一组或非门的两个输入端并接后,可以实现非门的功能D.把该集成块中的或非门加以组合,可以实现与门功能2.如图所示的集成逻辑门电路引脚图(V CC=5 V),关于该电路描述错误..的是()A.该集成电路属于TTL类型B.该集成电路的名称为四2输入与非门C.该集成电路由普通晶体三极管构成D.该集成电路的四个与非门作用各不相同3.如图a所示为小明设计的湿度警示实验电路,R S为负系数湿敏电阻,电路中所用芯片为四2输入与非门74LS00。

数字集成电路复习考题

数字集成电路复习

前言:看完后一定要自己默写一遍

一.确定组合逻辑延时最小时的尺寸?page186

反相器:1,三输入与非门:5/3,二输入与非门:5/3

输出负载是一个电容,其电容为第一级(最小尺寸的反相器)输入电容的5倍,因此该电路的等效扇出为1/5L g F C C==二.用图解的方法得到电压传输特性曲线求解图中门的阈值电压V TN?

三.一个PMOS管的阈值电压为-0.4V,计算VSB=2.5V,20.6T

VΦ=-时的阈值电压?Page64

四.绘制CMOS反相器的版图?

五.一个CMOS反相器,Kr=1,VDD=5V,VTN=0.8V,VTP=-1V,Cox=4F/cm2,un=500cm2/Vs,up=200cm2/Vs.由逻辑阈值点确定

的最大噪声容限为多少?

六.根据如下的逻辑关系式合成CMOS逻辑门,画出原理图()

=+⋅+

F D A B C。

说明:[难度等级(E容易M中等C难),需要的设计工具,与之相关的章节]第5章CMOS反相器4. [E, None, 3.3.3]对于图5.3中的输出负载为3pF的反相器:a. 计算t plh,t phl和t pb. 上升延时和下降延时是否相等?为什么?c. 计算静态和动态功耗,假设门的时钟频率尽可能的快。

图5.3 电阻负载反相器7. 考虑图5.5中的电路。

器件M1是一个标准的NMOS器件。

器件M2除了阈值电压为负并且其值为-0.4V之外,和M1有共同的特性。

假设耗尽型器件M2的所有电流公式和不等式(来决定工作模式)与规范的NMOS器件相同。

并假设输入IN有0V到2.5V的摆幅。

图5.5 一个耗尽型负载的NMOS反相器a.器件M2的栅极和源极相连。

如果V IN =0V,那么输出电压是多少?在稳态,对于这个输入,器件M2的工作模式是什么?b.计算V IN =2.5V时的输出电压。

为简化计算,你可以假设V OUT很小。

在稳态,对于这个输入,器件M2的工作模式是什么?c.假设Pr(LN=0)=0.3,这个电路的静态功耗是多少?8. [M, None, 3.3.3]一个NMOS晶体管用来向一个大电容充电,如图5.6所示:a. 确定这个电路的t pLH,假设输入节点有一个0到2.5V的理想阶跃信号。

b. 假设一个5kΩ的电阻R S用来对电容放电至地,确定t pHL的值。

c. 确定在对电容充电期间从电源得到多少能量。

其中多少能量在M1中被消耗?在放电期间,多少能量在下拉电阻上消耗?当R S减小至1kΩ时又是多少?d. NMOS晶体管用一个PMOS器件代替,k p和原先NMOS的k n相等。

替换后的结构是否比以前快?解释为什么。

图5.6 注明W/L比的电路图12. 考虑图5.9的低摆幅驱动:a. 输出节点(V out)的电压摆幅是多少?假设γ =0。

b. 输入端有一个从0V 到2.5V的翻转,估算(i)来自于电源的能量和(ii)能量损耗。