片上计算机系统 实验2 五位定点数补码加法 减法器

- 格式:doc

- 大小:192.50 KB

- 文档页数:2

课程设计任务书

2014~2015学年第 1 学期

学生姓名:专业班级:

指导教师:杨斐工作部门:计算机学院

一、课程设计题目硬件加减法器、乘法器的设计

二、课程设计内容(含技术指标)

1.利用QUARTUS软件设计一个5位加减法器和一个5位乘法器,分别实现两个5位有符号数(用二进制补码表示)的减法、减法、乘法运算。

2.加减法器电路(行波进位法):

一位全加器FA:求补器:(4位为例)

N位行波进位补码加、减法器:

3.乘法器核心电路(带求补器的阵列乘法器):

1)无符号阵列乘法器:

2)带求补器的阵列乘法器

输入数据分别存放在X、Y两个数据寄存器中,经过运算后,将乘积以十进制显示在数码管上。

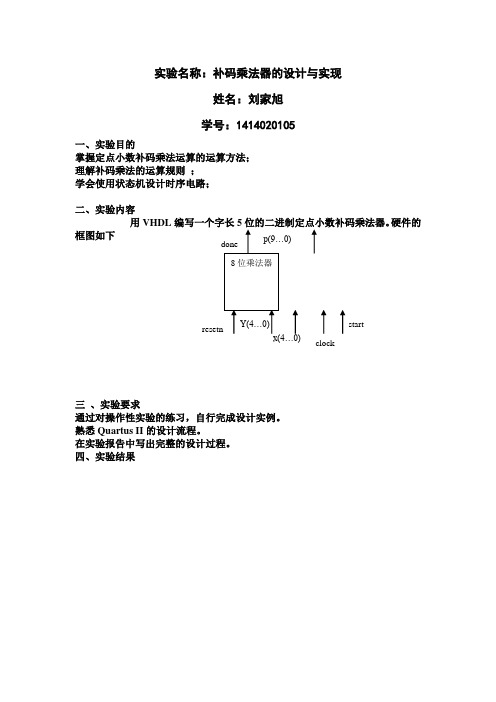

乘法器总体框图参考下图:(加减器类似)

三、进度安排

1.2014年12月12日,课题讲解,布置任务

2.2014年12月13日,分析、讨论、进行各子模块的设计设计

3.2014年12月16-18日,完成各模块联调,进行测试

4.2014年12月18日,成果验收,进行答辩

四、基本要求

1.能够熟练掌握计算机中乘法器模块的工作原理及其多种实现方案;

2.掌握硬件描述语言VHDL及原理图设计方法;

3.熟练掌握Quartus II软件平台;

4.各小组按模块分工,每人独立完成自己负责的模块;

5.合作完成最终的硬件下载及调试;

6.独立撰写符合要求的课程设计报告。

定点数补码加减法运算基本公式◆定点整数:[x ±y]补=[x]补+ [±y]补(mod 2n+1)◆定点小数:[x ±y]补=[x]补+ [±y]补(mod 2)定点数补码加减法运算◆符号位和数值位可同等处理;◆只要结果不溢出,将结果按2n+1或2取模,即为本次运算结果。

溢出判别方法——直接判别法◆同号补码相加,结果符号位与加数相反;◆异号补码相减,结果符号位与减数相同;------变形补码判别法变形补码,也叫模4补码:采用双符号位表示补码判别方法:双符号位结果00正01上溢10下溢11负——进位判别法判别方法:◆最高数值位的进位与符号位的进位是否相同;判别公式◆溢出标志V=C f⊕C n-1其中C f为符号位产生的进位,C n-1为最高数值位产生的进位。

定点除法运算约定判溢出:小数定点除法|x| <|y|,整数定点除法|x| >|y|被除数不等于0,除数不能为0串行除法-------原码恢复余数法步骤:1.用不含符号位的被除数+【-|y|】补:若余数为正,商1若余数为负,商0,并+【|y|】补恢复余数2.余数整体左移低位补0 +【-|y|】,余数处理同上PS:被除数(或余数)的绝对值减去除数的绝对值;机器内部用补码的加法运算实现在最末尾上商第一次上商判溢出小数定点除法|x| <|y|,整数定点除法|x| >|y|左移n次,上商n+1次符号位异或形成-------原码交替法运算规则:◆符号位不参加运算,取双符号位;◆用被除数减去除数:当余数为正时,商上1,余数左移一位,再减去除数;当余数为负时,商上0,余数左移一位,再加上除数。

◆根据余数的正负,再做如上处理(上商、加减除数)◆当第n+1步余数为负时,需加上|Y|得到第n+1步正确的余数,最后余数为r n×2-n(余数与被除数同号)。

Ps:上商n+1次n为商的精度第一次上商判溢出移n次加n+1次用移位的次数判断除法是否结束(是否达到要求的精度)并行除法并行除法器的类型◆恢复余数阵列除法器◆不恢复余数阵列除法器(采用加减交替法原理)基本元件:可控加法/减法(CAS)单元Ps:除数用补码表示,右移时符号位保持不变◆补码阵列除法器。

计算机组成原理与汇编语言实验报告实验二: 加减法运算器的设计与实现专业班级:xxxxxxxxxx学号:xxxxxxx 姓名:xxx学号:xxxxxxx 姓名:xxx实验地点:实验时间:实验二加减法运算器的设计一、实验目的1、理解加减法运算器的原理图设计方法2、掌握加减法运算器的VERILOG语言描述方法3、理解超前进位算法的基本原理4、掌握基于模块的多位加减运算器的层次化设计方法5、掌握溢出检测方法和标志线的生成技术6、掌握加减运算器的宏模块设计方法二、实验任务1、用VERILOG设计完成一个4位行波进位的加减法运算器,要求有溢出和进位标志,并封装成模块。

模块的端口描述如下:module lab2_RippleCarry 宽度可定制(默认为4位)的行波进位有符号数的加减法器。

#(parameter WIDTH=4)( input signed [WIDTH-1:0] dataa,input signed [WIDTH-1:0] datab,input add_sub, // if this is 1, add; else subtractinput clk,input cclr,input carry_in, //1 表示有进位或借位output overflow,output carry_out,output reg [WIDTH-1:0] result)2、修改上述运算器的进位算法,设计超前进位无符号加法算法器并封装成模块。

模块的端口描述如下:module lab2_LookaheadCarry // 4位超前进位无符号加法器(input [3:0] a,input [3:0] b,input c0,//carry_ininput clk,input cclr,output reg carry_out,output reg [3:0]sum);3、在上述超前进位加法运算器的基础上,用基于模块的层次化设计方法,完成一个32位的加法运算器,组内超前进位,组间行波进位。

定点加减法

位运算与逻辑运算非常简单

定点加、减法运算补码加法定点整数[x +y ]=补[x ]+补[y ]

补(mod 2)n +1定点小数[x +y ]=补[x ]+补[y ]补(mod 2)

补码减法定点整数[x −y ]=补[x ]−补[y ]=补[x ]+补[−y ]补(mod 2)n +1定点小数[x −y ]=补[x ]−补[y ]=补[x ]+补[−y ]补(mod 2)

等于的各位取反,末位加1

[−y ]补[y ]补定点数补码的加减法运算定点整数[x ±y ]=补[x ]+补[±y ]补(mod 2)n +1定点小数

[x ±y ]=补[x ]+补[±y ]补(mod 2)溢出概念与检验方法溢出

在定点数机器中,数的大小超出定点数能表示范围上溢数据大于机器所能表示的最大正数

下溢数据小于机器所能表示的最小负数

检验方法直接判别法

同号补码相加,结果符号位与加数相反异号补码相减,结果符号位与减数相同

硬件实现较复杂

变形补码判别法模4补码采用双符号位表示补码硬件实现简单,只需要对结果的符号进行异或

进位判别法

判别方法

最高位的进位与符号位的进位是否相同判别公式溢出标志V =C C f ⨁n −1二进制加法减法器逻辑门符号

一位半加器和全加器

全加器的逻辑结构门电路的时间延迟通常采用一个与非门或者一个或非门的时间延迟作为度量单位补充内容

与非门具有函数完备性在使用多发射极晶 体管的TTL集成电路中,与非门需要的晶体管也少于其他任何门电路多位二进制数据加法/减法器。

实验2 五位定点数补码加法/ 减法器

一、实验目的

1. 掌握计算机中定点数的加减法运算方法

2. 掌握在运算过程中溢出的判断方法

3. 在理解运算方法的基础上,掌握通过Verilog HDL语言描述的手段

二、实验内容

用Verilog HDL编写一个5位定点数补码加法/ 减法器,并进行设计综合和功能模拟

三、实验要求

1. 通过对操作性实验的练习,自行完成设计实例

2. 下载到DE II上进行验证

3. 熟悉Quartus II的设计流程

4. 在实验报告中写出完整的设计过程

四、实验结果

1. 补码加减法器程序代码(V erilog HDL)

module Sub_Add(sel,a,b,out,overflow);

input [4:0]a,b;

input sel;

output[4:0]out;

output overflow;

//reg [4:0] out;

reg overflow;

reg[5:0]aa,bb,out1;

always@(a,b)

begin

aa={a[4],a};

bb={b[4],b};

if(sel)

out1=aa+bb;

else

out1=aa+~bb+1;

overflow=out1[5]^out1[4];

end

assign out=out1[4:0];

endmodule

2. 波形图设定

3. 模拟结果。