计算机系统结构实验教程

- 格式:doc

- 大小:119.00 KB

- 文档页数:4

本科教学实验讲义(实验)课程名称计算机体系结构学院(部、中心):信息学院执笔人(签字): 唐斌审核人(签字):编写时间:2016.7.9贵州财经大学教务处印制年月日实验一流水线技术一、实验目的1.加深对计算机流水线基本概念的理解;2.理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作;3.加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU性能的影响;4.进一步理解解决数据冲突的方法,掌握如何应用定向技术来减少数据冲突引起的停顿。

5.加深对指令调度和延迟分支技术的理解;6.熟练掌握用指令调度技术来解决流水线中的数据冲突的方法;7.进一步理解指令调度技术和延迟分支技术对CPU性能的改进。

二、实验平台模拟器MIPSsim、计算机三、实验内容和步骤1、流水线工作原理a. 启动MIPSsim。

b. 勾选配置菜单中的“流水方式”,使模拟器工作于流水方式下。

c.观察程序在流水线中的执行情况,步骤如下:(1)用MIPSsim的“文件”菜单中的“载入程序”来加载pipeline.s(在模拟器所在文件夹下的“样例程序”文件夹中);(2)关闭定向功能。

这是通过在“配置”菜单中去选“定向”(即使得该项前面没有“√”号)来实现的;(3)用单步执行一周期的方式(“执行”菜单中,或用F7)执行该程序,观察每一周期中,各段流水寄存器内容的变化、指令的执行情况(代码窗口)以及时钟周期图;(4)当执行到第10个时钟周期时,各段分别正在处理的指令是:IF:ID:EX:MEM:WB:画出这时的时钟周期图。

(5). 这时各流水寄存器中的内容为:IF/ID.IR:IF/ID.NPC:ID/EX.A:ID/EX.B:ID/EX.Imm:ID/EX.IR:EX/MEM.ALUo:EX/MEM.IR:MEM/WB.LMD:MEM/WB.ALUo:MEM/WB.IR:2、流水线中的冲突a. 启动MIPSsim。

b. 观察和分析结构冲突对CPU性能的影响,步骤如下:(1)加载structure_hz.s(在模拟器所在文件夹下的“样例程序”文件夹中);(2)执行该程序,找出存在结构冲突的指令对以及导致结构冲突的部件;(3) 记录由结构冲突引起的停顿时钟周期数,计算停顿时钟周期数占总执行周期数的百分比;(4)把浮点加法器的个数改为6个;(5)再次重复上述(1)~(3)的工作;(6)分析结构冲突对CPU性能的影响,讨论解决结构冲突的方法。

计算机系统结构实验报告实验目的:掌握计算机系统的基本结构和工作原理,了解计算机系统的组成部分及其相互关系。

实验仪器和材料:计算机硬件设备(主机、硬盘、内存、显卡等)、操作系统、实验指导书、实验报告模板。

实验原理:实验步骤:1.搭建计算机硬件设备,将主机、硬盘、内存、显卡等组装连接好。

2. 安装操作系统,如Windows、Linux等。

3.启动计算机,进入操作系统界面。

4.打开任务管理器,查看CPU的使用情况。

5.打开任务管理器,查看内存的使用情况。

6.运行一些应用程序,观察CPU和内存的使用情况。

7.尝试使用输入输出设备,如键盘、鼠标等。

实验结果:通过实验,我们可以观察到计算机系统的硬件部分和软件部分的工作情况。

通过任务管理器,我们可以查看到CPU的使用情况和内存的使用情况。

在运行应用程序时,我们可以观察到CPU和内存的使用情况的变化。

通过使用输入输出设备,我们可以与计算机进行交互操作。

实验分析:从实验结果可以看出,计算机系统的硬件部分和软件部分都是相互关联的。

CPU作为计算机的核心部件,负责执行各种指令,通过数据传输和计算来完成各种操作。

而内存则用于存储数据和程序,通过读写操作来完成对数据的处理。

硬盘则用于长期存储数据。

操作系统则是计算机系统的管理者,通过调度CPU和内存的使用来实现对计算机资源的分配。

结论:计算机系统是由硬件和软件部分组成的,其中硬件部分包括CPU、内存、硬盘等,软件部分包括操作系统、应用程序等。

计算机系统通过CPU 的运算和数据传输来实现各种操作。

通过实验,我们可以观察到计算机系统的工作情况,并深入了解计算机系统的组成和工作原理。

实验总结:通过本次实验,我们对计算机系统的基本结构和工作原理有了更深入的了解。

实验中,我们搭建了计算机硬件设备,安装了操作系统,并通过观察和分析实验结果,进一步认识到计算机系统的组成部分和各部分之间的相互关系。

通过操作输入输出设备,我们还实践了与计算机进行交互操作的过程。

计算机系统结构课程实验指导书2016——2017 学年第 2学期姓名:徐益学号:201415725指导教师:薛素静教研室:计算机系统结构教研室实验:存贮层次模拟器1学时:4学时实验类型:(综合/设计):设计一、实验目的与要求使学生清楚认识虚拟存贮层次结构,熟练掌握常用的几种存储地址映像与变换方法,以及FIFO、LRU等替换算法的工作全过程。

要求用程序实现任意地址流在存储层次上的命中情况,实验结束后提交源程序和实验说明书。

二、实验内容在模拟器上实现在任意地址流下求出在 Cache—主存两层存贮层次上的命中率。

三、实验步骤1.Cache—主存:映像方式要实现全相联、直接映象、组相联方式三种方式,并选择每一种映像方式下输出结果;替换算法一般使用LRU算法。

2.要求主存容量、Cache大小、块大小以及组数等可以输入修改。

3.求出命中率;显示替换的全过程;任选一种高级语言来做。

4.要设计简洁、易于操作的界面。

四、实验仪器设备计算机(装有java、Apache tomcat)五、实验过程1、设计思想:(1)在本次实验中,我使用的是java语言来实现。

(2)首先,建一个web项目,然后将整个实验分为前端和后端两部分,前端为jsp页面,用来输入数据和显示实验结果。

后端为Java,在本次实验我用了一个MyServlt类,在这个类中用来接收前端的数据,然后进行一系列的逻辑处理;即各个算法的具体实现。

最后将数据传送给前端输出。

(3)将整个cache看成是一个对象,然后建一个实体类Cache。

在这个类中有cache的大小、块大小、块数、块地址、计数器、计时器等属性。

块地址用于存放地址流,计数器用于计算命中率,当命中一次,计数器加1。

计时器用于LRU 算法。

当命中时,计时器清零。

每一个循环结束,有地址的块计时器加1;替换时,找到计时器最大的块地址,然后把它替换出去。

(4)将要输出的数据封装成一个类,然后进行输出。

六、实验代码1、前端代码:Index.jsp代码(用于输入数据):在本页面中用到jqurey插件以达到美观效果,其中的js、css等代码就不粘贴出来了。

中国矿业大学计算机科学与技术学院计算机组织与体系结构实验一目录1.实验目的 (2)2.实验设备 (2)3.实验内容和步骤 (2)4.实验步骤 (7)5.实验结果 (9)6.实验体会 (19)1.实验目的1)了解运算器的组成结构;2)掌握运算器的工作原理。

2.实验设备PC机一台,TD-CMA实验系统一套。

3.实验内容和步骤本实验的原理如图1-1所示。

运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A和暂存器B,三个部件同时接受来自A和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),各部件对操作数进行何种运算由控制信号S3…S0和CN来决定,任何时候多路选择开关只选择三部件中一个部件的结果作为ALU的输出。

如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU零标志。

ALU中所有模块集成在一片FPGA中。

逻辑运算部件由逻辑门构成,较为简单,而后面又有专门的算术运算部件设计实验,在此对两个部件不再赘述。

移位运算采用的是桶形移位器,一般采用交叉开关矩阵来实现,交叉开关的原理如图1-2所示。

图中显示的是一个4*4的矩阵(系统中是一个8*8的矩阵)。

每一个输入都通过开关与一个输出相连,把沿对角线的开关导通,就可实现移位功能,即:1)对于逻辑左移或逻辑右移功能,将一条对角线的开关导通,这将所有的输入位与所使用的输出分别相连,而没有同任何输入相连的则输出连接0。

2)对于循环右移功能,右移对角线同互补的左移对角线一起激活。

例如,在4位矩阵中使用‘右1’和‘左3’对角线来实现右循环1位。

3)对于未连接的输出位,移位时使用符号扩展或是0填充,具体由相应的指令控制。

使用另外的逻辑进行移位总量译码和符号判别。

图1-1 运算器原理图运算器部件由一片FPGA实现。

ALU的输入和输出通过三态门74LS245连到CPU内总线上,另外还有指示灯标明进位标志FC和零标志FZ。

计算机系统结构实验指导主编:刘文英宋继志中国石油大学(华东)计算机与通信工程学院目录实验一熟悉模拟器W IN DLX的使用 (1)一、实验目的 (1)二、实验平台 (1)三、实验内容和步骤 (1)四、实验任务 (6)实验二流水线中的相关 (8)一、实验目的 (8)二、实验平台 (8)三、实验内容和步骤 (8)实验三环境熟悉与基本CPU设计 (10)一、实验目的 (10)二、实验说明 (10)三、基本CPU的设计 (14)四、实验步骤与现象 (19)五、实验思考总结 (20)实验四多级流水CPU设计 (21)一、实验目的 (21)二、流水线的工作原理 (21)三、5级流水无Cache的CPU (24)四、实验步骤与现象 (31)五、实验总结思考 (32)附录A TEC-CA开放式CPU实验教学系统介绍 (33)A.1 TEC-CA的总体结构概述 (33)A.1.1 TEC-CA的组成部分 (33)A.1.2 TEC-CA的总体结构 (34)A.2 TEC-CA的设计指导思想 (34)A.3 TEC-CA的功能概述 (35)A.3.1 TEC-CA的基本功能 (35)A.3.2 TEC-CA的扩展功能 (35)A.4 子板 (36)A.4.1 Cyclone系列FPGA的特点 (36)A.4.2 Cyclone系列FPGA的结构 (37)A.4.3 TEC-CA-I子板和实验平台的连接 (38)A.4.4 使用EPlC6和EPlCl2的限制 (38)A.5 实验平台 (41)A.5.1 实验平台布局图 (41)A.5.2 实验平台上的指示灯 (42)A.5.2 实验平台上的指示灯 (43)A.5.3 实验平台上的开关 (43)A.5.4 实验平台上的指示灯和逻辑笔 (45)A.5.5 实验平台上的短路子和单脉冲按钮 (46)A.6 TEC-CA的3种调试模式及其设定 (46)A.6.1 TEC-CA的3种调试模式 (46)A.6.2 三种调试模式的设定 (48)A.7 FPGA-CPU的一般实验步骤 (48)A.8 TEC-CA出厂时模式开关和短路子的默认设置 (50)附录B 调试软件DEBUGCONTROLLER (51)B.1 简介 (51)B.1.1 用户界面 (51)B.1.2 命令 (53)B.1.3 Debugcontroller使用流程 (56)B.2 规则文件语法与编写指南 (60)B.2.1 基本语法 (60)B.2.2 进阶使用 (62)B.3 汇编程序格式说明 (64)附录C TEC-CA教学机用前准备工作 (66)实验一熟悉模拟器WinDLX的使用一、实验目的1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点。

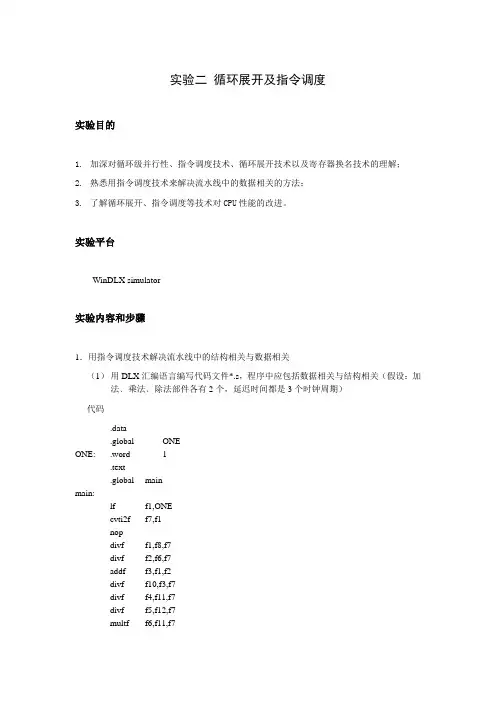

实验二循环展开及指令调度实验目的1.加深对循环级并行性、指令调度技术、循环展开技术以及寄存器换名技术的理解;2.熟悉用指令调度技术来解决流水线中的数据相关的方法;3.了解循环展开、指令调度等技术对CPU性能的改进。

实验平台WinDLX simulator实验内容和步骤1.用指令调度技术解决流水线中的结构相关与数据相关(1)用DLX汇编语言编写代码文件*.s,程序中应包括数据相关与结构相关(假设:加法﹑乘法﹑除法部件各有2个,延迟时间都是3个时钟周期)代码.data.global ONEONE: .word 1.text.global mainmain:lf f1,ONEcvti2f f7,f1nopdivf f1,f8,f7divf f2,f6,f7addf f3,f1,f2divf f10,f3,f7divf f4,f11,f7divf f5,f12,f7multf f6,f11,f7multf f6,f4,f5divf f13,f6,f7Finish:trap 0(2)通过Configuration菜单中的“Floating point stages”选项,把加法﹑乘法﹑除法部件的个数设置为2个,把延迟都设置为3个时钟周期;(3)用WinDLX运行程序。

记录程序执行过程中各种相关发生的次数、发生相关的指令组合,以及程序执行的总时钟周期数;结构相关1次别在9 10行数据相关3次分别在5 6 11行(4)采用指令调度技术对程序进行指令调度,消除相关;.data .global ONEONE: .word 1.text.global mainmain:lf f1,ONEcvti2f f7,f1nopdivf f1,f8,f7divf f2,f6,f7divf f10,f3,f7divf f4,f11,f7addf f3,f1,f2multf f6,f11,f7divf f5,f12,f7multf f6,f4,f5divf f13,f6,f7Finish:trap 0(5)用WinDLX运行调度后的程序,观察程序在流水线中的执行情况,记录程序执行的总时钟周期数;(6)根据记录结果,比较调度前和调度后的性能。

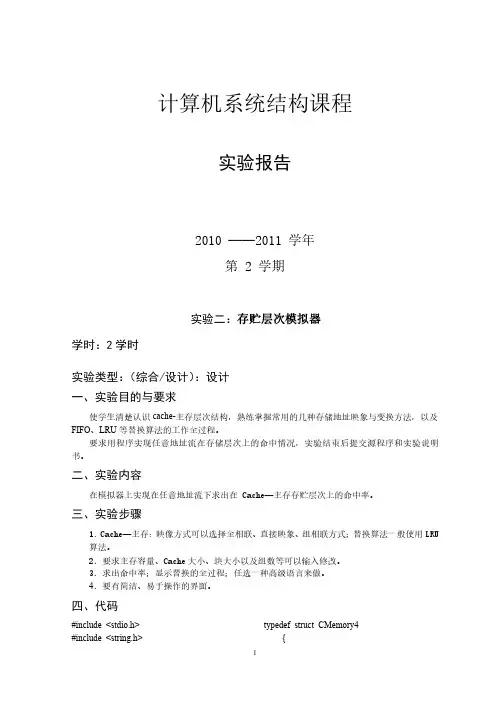

计算机系统结构课程计算机系统结构课程实验报告2010 2010 ——————2011 2011 2011 学年学年学年第 2 2 学期学期学期实验二:存贮层次模拟器学时:学时:22学时实验类型:(综合(综合//设计):设计 一、实验目的与要求使学生清楚认识cache-主存层次结构,熟练掌握常用的几种存储地址映象与变换方法,以及FIFO 、LRU 等替换算法的工作全过程。

等替换算法的工作全过程。

要求用程序实现任意地址流在存储层次上的命中情况,实验结束后提交源程序和实验说明书。

书。

二、实验内容在模拟器上实现在任意地址流下求出在在模拟器上实现在任意地址流下求出在 Cache Cache Cache—主存存贮层次上的命中率。

—主存存贮层次上的命中率。

—主存存贮层次上的命中率。

三、实验步骤1.Cache Cache—主存:—主存:映像方式可以选择全相联、直接映象、组相联方式;替换算法一般使用LRU算法。

算法。

2.要求主存容量、.要求主存容量、Cache Cache 大小、块大小以及组数等可以输入修改。

大小、块大小以及组数等可以输入修改。

3.求出命中率;显示替换的全过程;任选一种高级语言来做。

.求出命中率;显示替换的全过程;任选一种高级语言来做。

4.要有简洁、易于操作的界面。

.要有简洁、易于操作的界面。

四、代码#include <stdio.h> #include <string.h> typedef struct CMemory4 { int gm;//组号组号组号int bm; }; CMemory4 mem4[50]; typedef struct CCach4 { int gc; int bc; int cc; int bs; }; CCach4 cac4[50]; int a2[10][20],b2[10][20]; void inputmem2(int m_num,int group) //输入输入 { int i,t=0,nn=0; for(i=0;i<m_num;) { for(int j=0;j<group;j++) { if(i>=m_num) { break; } printf("第%d块",i); scanf("%d",&nn); mem4[i].bm=nn; mem4[i].gm=nn%group; i++; } } } void initcac2(int ilen,int group) // { int i=0,j=0; for(i;i<group;i++) { for(j;j<ilen/group;j++) { //cac[j].gc=i;// cac4[j].bc=-1;// cac4[j].cc=0; cac4[j].bs=j; } } } void change2(int x,int y,int cnum) { for(int i=0;i<cnum;i++) { cac4[i].cc+=1; } a2[y][x]=cac4[y].bc; b2[y][x]=cac4[y].cc; } void fdl(int cnum) { int tmp; tmp=cac4[0].bc; for(int i=0;i<cnum;i++) { cac4[i].bc=cac4[i+1].bc; } cac4[cnum-1].bc=tmp; } float steadcac2(int tt,int c_num,int j,float h,int i,int g,int group) { float sc=h; int fi=1,fj;//判断是否装满的标记判断是否装满的标记判断是否装满的标记for (int jj=0;jj<c_num;jj++)//判断cache中是否装满中是否装满 { if(jj%group==g&&cac4[jj].bc==-1) { fi=0;//没有装满没有装满fj=jj; break; } } if(fi==0)// 未装满未装满{ cac4[fj].bc=tt;//装入Cache中printf("块%d装入%d组%d块号\n",tt,g,cac4[fj].bs); } else //装满装满装满{ int m=0; for(m;m<c_num;m++) { if(tt==cac4[m].bc) { printf("块%d命中%d组%d块号\n",tt,g,cac4[m].bs); sc=sc+1;//命中命中break; } } if (m==c_num) { fdl(c_num);//FIFO替换,把进队较早的替换掉替换,把进队较早的替换掉cac4[0].bc=tt; printf("块%d替换%d组%d块号\n",tt,g,cac4[m].bs); } } return sc; } bool compare2(int m_num,int c_num,int group) { float sc=0; int sm=0,max,j=0,gm,gc,gt=0,tt,bm; for(int i=0;i<m_num;i++)//内存单元内存单元内存单元{ for(j=0;j<c_num; j++) { gm=mem4[i].gm; gc=j%group; bm=mem4[i].bm; if(gm==gc)//检查组号相等检查组号相等{ if(cac4[gt].bc==bm) { sc=sc+1;//命中命中printf("块%d命中%d组%d块号!\n",bm,gc,cac4[gt].bs); } else { if(j==0) { gt=0; } else { gt++; } sc=steadcac2(bm,c_num,gt,sc,i,gc,group); } sm++; if(gt>=c_num/group) { gt=0; } break; } } } printf("命中率:H=%.2f\n",sc/sm); return 1; } void Flink()// { int m_num,c_num,group; printf("请输入内存大小:"); scanf("%d",&m_num); printf("请输入Cache大小:"); scanf("%d",&c_num); printf("请输入组数:"); scanf("%d",&group); inputmem2(m_num,group); initcac2(c_num,group); // compare2(m_num,c_num,group); } 结果截图:结果截图:。

计算机系统结构模拟实验手册孟昭进刘东升赵斯琴编内蒙古师范大学计算机与信息工程学院二00六年五月计算机系统结构模拟实验手册目录第一部分预备知识 (3)1.指令集结构发展概述 (4)2.WinDLX简介 (6)3.DLX指令集结构 (7)3.1 DLX的寄存器 (7)3.2 DLX的数据类型 (7)3.3 DLX的寻址模式 (7)3.4 DLX指令格式 (8)3.5 DLX指令集 (8)4.WinDLX模拟器教程 (13)4.1 WinDLX模拟器的安装 (13)4.2 开始和配置WinDLX (13)4.3装载测试程序 (14)4.4 模拟运行程序 (18)5.实验中用到的几个.s文件 (24)第二部分实验项目 (25)实验一熟悉WinDLX的使用 (26)一、实验目的 (26)二、实验内容 (26)三、实验报告 (26)实验二DLX流水线结构相关 (27)一、实验目的 (27)二、实验内容 (27)三、实验报告 (27)实验三DLX流水线数据相关 (28)一、实验目的 (28)二、实验内容 (28)三、实验报告 (28)实验四DLX流水线指令调度 (29)一、实验目的 (29)二、实验内容 (29)三、实验报告 (29)实验五编译器对系统性能的影响实验 (30)一、背景知识 (30)二、gcc简介 (31)三、icc 简介 (32)·1·计算机系统结构模拟实验手册.2.四、实验目的 (32)五、实验内容 (32)六、实验报告 (33)实验六CPU性能测试实验 (34)一、背景知识 (34)二、实验目的 (35)三、实验内容 (35)四、实验报告 (35)实验七基于Cache的矩阵乘积算法性能改善实验 (39)一、背景知识 (39)二、实验目的 (40)三、实验内容 (40)四、实验报告 (40)参考文献 (43)计算机系统结构模拟实验手册第一部分预备知识·3·计算机系统结构模拟实验手册·4·1.指令集结构发展概述IBM资深专家 C.M.Amdahl 1964年在介绍IBM 360系统时首先提出计算机系统结构(computer architecture)的概念:计算机系统结构是程序员所看到的计算机的属性,即概念性结构与功能特性。

大连理工大学实验报告计算机系统结构实验实验一MIPS指令系统和MIPS体系结构学院(系):电子信息与电气工程学部专业:计算机科学与技术学生姓名:班级:学号:大连理工大学Dalian University of Technology实验一MIPS指令系统和MIPS体系结构一、实验目的和要求1. 了解熟悉MIPSsim模拟器。

2. 熟悉MIPS指令系统及其特点。

3. 熟悉MIPS体系结构。

二、实验步骤1、启动MIPSsim。

2、选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。

3、参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

4、选择“文件”->“载入程序”选项,加载样例程序alltest.asm,然后查看“代码”窗口,查看程序所在的位置(起始地址为0x00000000)。

5、查看“寄存器”窗口PC寄存器的值:[PC]= 0x00000000 。

6、执行load和store指令,步骤如下:(1)单步执行一条指令(F7)。

(2)下一条指令地址为= 0x00000004 ,是一条有(有,无)符号载入字节(字节,半字,字)指令。

(3)单步执行一条指令(F7)。

(4)查看R1的值,[R1]=0X FFFFFFFFFFFFFF80 。

(5)下一条指令地址为=0X00000008 ,是一条有(有,无)符号载入字(字节,半字,字)指令。

(6)单步执行1条指令。

(7)查看R1的值,[R1]=0X0000000000000080 。

(8)下一条指令地址为=0X0000000C ,是一条无(有,无)符号载入字(字节,半字,字)指令。

(9)单步执行1条指令。

(10)查看R1的值,[R1]= 0X0000000000000080 。

(11)单步执行1条指令。

(12)下一条指令地址为0X00000014 ,是一条保存字(字节,半字,字)指令。

(13)单步执行一条指令。

(14)查看内存BUFFER处字的值,值为0x00000080 。

实验一算术逻辑运算实验一.实验目的1.了解运算器的组成结构。

2.掌握运算器的工作原理。

3.学习运算器的设计方法。

4.掌握简单运算器的数据传送通路。

5.验证运算功能发生器74LS181 的组合功能。

二.实验设备TDN-CM+或TDN-CM++教学实验系统一套。

三.实验原理实验中所用的运算器数据通路图如图2.6-1。

图中所示的是由两片74LS181 芯片以并/串形式构成的8 位字长的运算器。

右方为低4 位运算芯片,左方为高4 位运算芯片。

低位芯片的进位输出端Cn+4 与高位芯片的进位输入端Cn 相连,使低4 位运算产生的进位送进高4 位运算中。

低位芯片的进位输入端Cn 可与外来进位相连,高位芯片的进位输出引至外部。

两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。

为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。

要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。

当T4 脉冲来到的时候,总线上的数据就被锁存进DR1 或DR2 中了。

为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。

若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。

否则输出高阻态。

2图2.6-1 运算器通路图数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。

其中,输入开关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时,开关上的数据则通过三态门而送入内总线中。

总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。

控制信号中除T4 为脉冲信号,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出端。

实验一流水线及流水线中的冲突

实验目的

1.加深对计算机流水线基本概念的理解;

2.理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作;

3.加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU性能的影响;

4.进一步理解解决数据冲突的方法,掌握如何应用定向技术来减少数据冲突引起的停顿。

5.加深对指令调度和延迟分支技术的理解;

6.熟练掌握用指令调度技术来解决流水线中的数据冲突的方法;

7.进一步理解指令调度技术和延迟分支技术对CPU性能的改进。

实验平台

指令级和流水线操作级模拟器MIPSsim,

实验内容和步骤

首先要掌握MIPSsim模拟器的使用方法。

一、流水线及流水线中的冲突观察

1. 启动MIPSsim。

2.根据预备知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义。

(用鼠标双击各段,就可以看到各流水寄存器的内容)

3. 熟悉MIPSsim模拟器的操作和使用方法。

可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中),然后分别以单步执行一个周期、执行多个周期、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化,特别是流水寄存器内容的变化。

4. 勾选配置菜单中的“流水方式”,使模拟器工作于流水方式下。

5.观察程序在流水线中的执行情况,步骤如下:

(1)用MIPSsim的“文件”菜单中的“载入程序”来加载pipeline.s(在模拟器所在文

件夹下的“样例程序”文件夹中);

(2)关闭定向功能。

这是通过在“配置”菜单中去选“定向”(即使得该项前面没有“√”

号)来实现的;

(3)用单步执行一周期的方式(“执行”菜单中,或用F7)执行该程序,观察每一周

期中,各段流水寄存器内容的变化、指令的执行情况(代码窗口)以及时钟周期

图;

(4)当执行到第10个时钟周期时,各段分别正在处理的指令是:

IF:

ID:

EX:

MEM:

WB:

画出这时的时钟周期图。

6. 这时各流水寄存器中的内容为:

IF/ID.IR:

IF/ID.NPC:

ID/EX.A:

ID/EX.B:

ID/EX.Imm:

ID/EX.IR:

EX/MEM.ALUo:

EX/MEM.IR:

MEM/WB.LMD:

MEM/WB.ALUo:

MEM/WB.IR:

7. 观察和分析结构冲突对CPU性能的影响,步骤如下:

(1)加载structure_hz.s(在模拟器所在文件夹下的“样例程序”文件夹中);

(2)执行该程序,找出存在结构冲突的指令对以及导致结构冲突的部件;

(3) 记录由结构冲突引起的停顿时钟周期数,计算停顿时钟周期数占总执行周期数的百分比;

(4)把浮点加法器的个数改为6个;

(5)再次重复上述(1)~(3)的工作;

(6)分析结构冲突对CPU性能的影响,讨论解决结构冲突的方法。

8. 观察数据冲突并用定向技术来减少停顿,步骤如下:

(1)把浮点加法器的个数改为1个;

(2)加载data_hz.s(在模拟器所在文件夹下的“样例程序”文件夹中);

(3)关闭定向功能。

这是通过在“配置”菜单中去选“定向”(即使得该项前面没有“√”

号)来实现的;

(4)用单步执行一个周期的方式(F7)执行该程序,同时查看时钟周期图,列出在什么时刻发生了RAW(先写后读)冲突;

(5)记录数据冲突引起的停顿时钟周期数以及程序执行的总时钟周期数,计算停顿时钟周期数占总执行周期数的百分比;

(6)复位CPU;

(7)打开定向功能。

这是通过在“配置”菜单中勾选“定向”(即使得该项前面有一个“√”号)来实现的;

(8)用单步执行一周期的方式(F7)执行该程序,同时查看时钟周期图,列出在什么时刻发生了RAW(先写后读)冲突,并与(3)的结果进行比较;

(9)记录数据冲突引起的停顿时钟周期数以及程序执行的总时钟周期数。

计算采用定向技术后性能提高的倍数。

二、指令调度和延迟分支

1. 启动MIPSsim。

2. 根据预备知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义。

(用鼠标双击各段,就可以看到各流水寄存器的内容)

3. 勾选配置菜单中的“流水方式”,使模拟器工作于流水方式下。

4. 用指令调度技术解决流水线中的结构冲突与数据冲突。

(1)启动MIPSsim;

(2)通过“配置”菜单中的“常规配置”项把加法﹑乘法﹑除法部件的个数设置为两个,把它们的延迟时间都设置为3个时钟周期;

(3)用MIPSsim的“文件”菜单中的“载入程序”来加载schedule.asm(在模拟器所在文件夹下的“样例程序”文件夹中);

(4)关闭定向功能。

这是通过在“配置”菜单中去选“定向”(即使得该项前面没有“√”

号)来实现的。

(5)执行所载入的程序,通过查看统计数据和时钟周期图,找出并记录程序执行过程中各种冲突发生的次数、发生冲突的指令组合,以及程序执行的总时钟周期数;

(6)采用指令调度技术对程序进行指令调度,消除冲突。

将调度后的程序放到after-schedule.asm中;

(7)载入after-schedule.asm;

(8)执行该程序,观察程序在流水线中的执行情况,记录程序执行的总时钟周期数;

(9)根据记录结果,比较调度前和调度后的性能。

论述指令调度对于提高CPU性能的作用。

5. 用延迟分支减少分支指令对性能的影响。

(1)启动MIPSsim;

(2)载入branch.asm;

(3)关闭延迟分支功能。

这是通过在“配置”菜单中去选“延迟分支”来实现的;

(4)执行该程序,观察并记录发生分支延迟的时刻,保存下其时钟周期图(可用拷屏的方法);

(5)记录执行该程序所花的总时钟周期数;

(6)假设延迟槽为一个,对branch.asm进行指令调度,然后存到delayed-branch.asm中;(7)载入delayed-branch.asm;

(8)打开延迟分支功能;

(9)执行该程序,观察其时钟周期图,保存下其时钟周期图;

(10)记录执行该程序所花的总时钟周期数;

(11)对比上述两种情况下的时钟周期图;

(12)根据记录结果,比较没采用延迟分支和采用了延迟分支的性能。

论述延迟分支对于提高CPU性能的作用。