PCB电路板 EMI设计规范及步骤

- 格式:docx

- 大小:33.67 KB

- 文档页数:2

第二篇抗干扰3(部分)3 提高敏感器件的抗干扰性能提高敏感器件的抗干扰性能是指从敏感器件这边考虑尽量减少对干扰噪声的拾取,以及从不正常状态尽快恢复的方法。

提高敏感器件抗干扰性能的常用措施如下:(1)布线时尽量减少回路环的面积,以降低感应噪声。

(2)布线时,电源线和地线要尽量粗。

除减小压降外,更重要的是降低耦合噪声。

(3)对于单片机闲置的I/O口,不要悬空,要接地或接电源。

其它IC的闲置端在不改变系统逻辑的情况下接地或接电源。

(4)对单片机使用电源监控及看门狗电路,如:IMP809,IMP706,IMP813,X25043,X25045等,可大幅度提高整个电路的抗干扰性能。

(5)在速度能满足要求的前提下,尽量降低单片机的晶振和选用低速数字电路。

(6)IC器件尽量直接焊在电路板上,少用IC座。

第三篇印制电路板的可靠性设计-去耦电容配置在直流电源回路中,负载的变化会引起电源噪声。

例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。

配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。

如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

第四篇电磁兼容性和PCB设计约束(缺具体数据)PCB布线对PCB的电磁兼容性影响很大,为了使PCB上的电路正常工作,应根据本文所述的约束条件来优化布线以及元器件/接头和某些IC所用去耦电路的布局(一)、PCB材料的选择通过合理选择PCB的材料和印刷线路的布线路径,可以做出对其它线路耦合低的传输线。

电路板EMI设计介绍在现代电子设备中,电路板是连接各个电子元件的重要组成部分。

然而,电路板在高频运行时可能会产生电磁干扰(EMI),对周围的电子设备和系统造成不利影响。

因此,进行电路板EMI设计是必要的,以确保设备的正常工作和可靠性。

本文将详细探讨电路板EMI设计的相关内容。

电磁干扰概述电磁干扰是指电磁场的能量在电路板或其它电子设备中引起的非预期影响。

这些干扰可以来自电源、信号线、地线等各种来源。

电磁干扰可能导致电路板的性能下降、设备故障、通信中断等问题,因此需要通过EMI设计来减小这些干扰。

EMI设计原则在进行电路板EMI设计时,需要遵循一些基本原则,以确保设计的高效和可靠。

以下是一些常用的EMI设计原则:1. 布局和层叠设计合理的电路板布局和层叠设计可以最大程度地减小电磁干扰。

布局设计应将信号线和电源线与敏感线路、高频线路等相隔离,并避免并行布线。

层叠设计可以通过在不同层次上布置信号层、地层和电源层,有效降低电磁辐射。

2. 地线设计地线是电路板EMI设计中非常重要的一部分。

合理的地线布局可以减小地回线的电阻和电感,降低电磁干扰。

使用大面积的地层和多个接地点,可以提高地线的效果。

3. 滤波设计滤波是减小电磁干扰的一种重要手段。

在电路板设计中,可以通过添加滤波电容、电感和滤波器等元件,来抑制高频噪声和谐波。

4. 屏蔽设计屏蔽设计是减小电磁辐射和接收外部干扰的有效方法。

可以在电路板和电子器件之间设置屏蔽罩,以防止电磁干扰的传播。

EMI设计步骤进行电路板EMI设计时,可以按照以下步骤进行:1. 确定设计需求和规范首先,需要明确设计的需求和规范。

根据电子设备的用途和运行环境,制定相应的EMI设计要求。

2. 进行电路板布局设计根据设计需求,进行电路板的布局设计。

将信号线、地线和电源线合理布置,并避免并行布线和敏感线路的相互干扰。

3. 进行层叠设计根据电路板的复杂度和性能要求,进行层叠设计。

将信号层、地层和电源层分开布局,以降低电磁辐射。

高速PCB设计EMI规则引言:随着信号上升沿、下降沿时间的减小,信号频率的提高,电子产品的EMI问题,也越来越受到电子工程师的光注。

在高速PCB设计的成功,对整个产品的EMI问题的解决的贡献越来越受到重视。

做了多年的产品级EMI设计,现整理一些最为普通的高速PCB设计EMI方面的规则和大家共享。

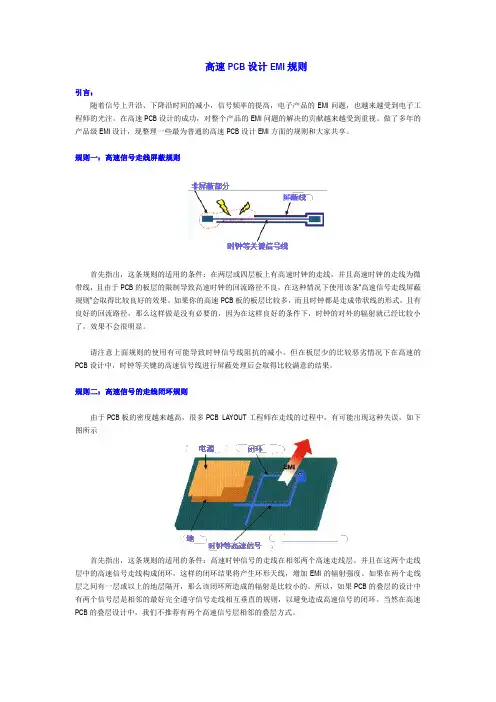

规则一:高速信号走线屏蔽规则首先指出,这条规则的适用的条件:在两层或四层板上有高速时钟的走线,并且高速时钟的走线为微带线,且由于PCB的板层的限制导致高速时钟的回流路径不良,在这种情况下使用该条"高速信号走线屏蔽规则"会取得比较良好的效果。

如果你的高速PCB板的板层比较多,而且时钟都是走成带状线的形式,且有良好的回流路径,那么这样做是没有必要的,因为在这样良好的条件下,时钟的对外的辐射就已经比较小了,效果不会很明显。

请注意上面规则的使用有可能导致时钟信号线阻抗的减小。

但在板层少的比较恶劣情况下在高速的PCB设计中,时钟等关键的高速信号线进行屏蔽处理后会取得比较满意的结果。

规则二:高速信号的走线闭环规则由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,有可能出现这种失误,如下图所示首先指出,这条规则的适用的条件:高速时钟信号的走线在相邻两个高速走线层。

并且在这两个走线层中的高速信号走线构成闭环,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

如果在两个走线层之间有一层或以上的地层隔开,那么该闭环所造成的辐射是比较小的。

所以,如果PCB的叠层的设计中有两个信号层是相邻的最好完全遵守信号走线相互垂直的规则,以避免造成高速信号的闭环。

当然在高速PCB的叠层设计中,我们不推荐有两个高速信号层相邻的叠层方式。

规则三:高速信号的走线开环规则规则二提到高速信号的闭环会造成EMI辐射,同样的开环同样会造成EMI辐射,如下图所示:首先指出,这条规则的适用的条件:在高速PCB设计中,几乎没有人可以避免该条规则。

PCB 板EMC EMI 的设计技巧随着IC 器件集成中心议题:EMI的产生及抑制原理详析数字电路PCB的EMI控制技术详析EMI的其它控制手段详析EMI分析与测试详析解决方案:叠层设计、合理布局、布线电源系统设计、接地、串接阻尼电阻、屏蔽、扩频引言随着IC 器件集成度的提高、设备的逐步小型化和器件的速度愈来愈高,电子产品中的EMI问题也更加严重。

从系统设备EMC /EMI设计的观点来看,在设备的PCB设计阶段处理好EMC/EMI问题,是使系统设备达到电磁兼容标准最有效、成本最低的手段。

本文介绍数字电路PCB设计中的EMI控制技术。

1 EMI的产生及抑制原理EMI的产生是由于电磁干扰源通过耦合路径将能量传递给敏感系统造成的。

它包括经由导线或公共地线的传导、通过空间辐射或通过近场耦合三种基本形式。

EMI的危害表现为降低传输信号质量,对电路或设备造成干扰甚至破坏,使设备不能满足电磁兼容标准所规定的技术指标要求。

为抑制EMI,数字电路的EMI设计应按下列原则进行:* 根据相关EMC/EMI技术规范,将指标分解到单板电路,分级控制。

* 从EMI的三要素即干扰源、能量耦合途径和敏感系统这三个方面来控制,使电路有平坦的频响,保证电路正常、稳定工作。

* 从设备前端设计入手,关注EMC/EMI设计,降低设计成本。

2 数字电路PCB的EMI控制技术在处理各种形式的EMI时,必须具体问题具体分析。

在数字电路的PCB设计中,可以从下列几个方面进行EMI控制。

2.1 器件选型在进行EMI设计时,首先要考虑选用器件的速率。

任何电路,如果把上升时间为5ns的器件换成上升时间为2.5ns的器件,EMI会提高约4倍。

EMI的辐射强度与频率的平方成正比,最高EMI频率(fknee)也称为EMI发射带宽,它是信号上升时间而不是信号频率的函数:fknee =0.35/Tr (其中Tr为器件的信号上升时间)这种辐射型EMI的频率范围为30MHz到几个GHz,在这个频段上,波长很短,电路板上即使非常短的布线也可能成为发射天线。

PCB可制造性设计规范PCB (Printed Circuit Board)的制造性设计规范是指在设计和布局PCB电路板时所需考虑的一系列规范和标准,以确保电路板的制造过程顺利进行并获得可靠性和性能。

一、尺寸规范1.PCB电路板的尺寸要符合制造商的要求,包括最小尺寸、最大尺寸和板上零部件之间的间距。

2.确保电路板的边缘清晰、平整,并防止零部件或钳具与电路板边缘重叠。

二、层规范1.根据设计要求确定所需的层次和层的数量,确保原理图和布局文件的一致性。

2.定义PCB的地平面层、电源层、信号层和垫层、焊盘层等的位置和规格。

三、元件布局规范1. 合理布局元件,以最小化路径长度和EMI (Electromagnetic Interference),提高电路的可靠性和性能。

2.避免元件之间的相互干扰和干涉,确保元件之间有足够的间距,以便于焊接工序和维修。

四、接线规范1.线路走向应简洁、直接,避免交叉和环形走线。

2.确保信号和电源线路之间的隔离,并使用正确的引脚布局和接线技术。

五、电路可靠性规范1.选择适当的层次和厚度,以确保足够强度和刚度。

2.确保电路板表面和感应部件光滑,以防止划伤和损坏。

六、焊接规范1.在设计中使用标准的焊盘尺寸和间距,以方便后续的手工或自动焊接。

2.制定适当的焊盘和焊缺陷防范措施,以最小化焊接问题的发生。

七、标准规范1. 遵循IPC (Institute for Interconnecting and Packaging Electronic Circuits)标准,以确保PCB的制造符合国际标准。

2.正确标注和命名电路板上的元件和信号,以方便生产和测试。

八、生产文件和图纸规范1.提供准确和详细的生产文件和图纸,包括层叠图、金属化孔、引线表和拼图图等。

2.确保文件和图纸的易读性和可修改性。

九、封装规范1.选择适当的封装类型和尺寸,以满足电路板的要求。

2.避免使用不常见或过于复杂的封装,以确保可靠的元件焊接和连接。

開關電源的PCB設計規範在任何開關電源設計中,pcb板的物理設計都是最後一個環節,如果設計方法不當,pcb可能會輻射過多的電磁干擾,造成電源工作不穩定,以下針對各個步驟中所需注意的事項進行分析:一、從原理圖到pcb的設計流程建立元件參數->輸入原理網表->設計參數設置->手工佈局->手工佈線->驗證設計->複查->cam輸出。

二、參數設置相鄰導線間距必須能滿足電氣安全要求,而且為了便於操作和生產,間距也應儘量寬些。

最小間距至少要能適合承受的電壓,在佈線密度較低時,信號線的間距可適當地加大,對高、低電平懸殊的信號線應盡可能地短且加大間距,一般情況下將走線間距設為8mil。

焊盤內孔邊緣到印製板邊的距離要大於1mm,這樣可以避免加工時導致焊盤缺損。

當與焊盤連接的走線較細時,要將焊盤與走線之間的連接設計成水滴狀,這樣的好處是焊盤不容易起皮,而是走線與焊盤不易斷開。

三、元器件佈局實踐證明,即使電路原理圖設計正確,印製電路板設計不當,也會對電子設備的可靠性產生不利影響。

例如,如果印製板兩條細平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射雜訊;由於電源、地線的考慮不周到而引起的干擾,會使產品的性能下降,因此,在設計印製電路板的時候,應注意採用正確的方法。

每一個開關電源都有四個電流回路:(1). 電源開關交流回路(2). 輸出整流交流回路(3). 輸入信號源電流回路(4). 輸出負載電流回路輸入回路通過一個近似直流的電流對輸入電容充電,濾波電容主要起到一個寬頻儲能作用;類似地,輸出濾波電容也用來儲存來自輸出整流器的高頻能量,同時消除輸出負載回路的直流能量。

所以,輸入和輸出濾波電容的接線端十分重要,輸入及輸出電流回路應分別只從濾波電容的接線端連接到電源;如果在輸入/輸出回路和電源開關/整流回路之間的連接無法與電容的接線端直接相連,交流能量將由輸入或輸出濾波電容並輻射到環境中去。

PCB EMI设计规范1 、IC的电源处理1.1)保证每个IC的电源PIN都有一个0.1UF的去耦电容,对于BGA CHIP,要求在BGA 的四角分别有0.1UF、0.01UF的电容共8个。

对PCB走线的电源尤其要注意加滤波电容,如VTT等。

这不仅对稳定性有影响,对EMI也有很大的影响。

2、时钟线的处理2.1)建议先走时钟线。

2.2)频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个。

2.3)频率小于66M的时钟线,每条过孔数不要超过3个,平均不得超过2.5个2.4)长度超过12inch的时钟线,如果频率大于20M,过孔数不得超过2个。

2.5)如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。

旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过300MIL。

图2.5-1过孔处的旁路电容2.6)所有时钟线原则上不可以穿岛。

下面列举了穿岛的四种情形。

2.6.1) 跨岛出现在电源岛与电源岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)有两个电源岛,且第四层的PCB走线必须跨过这两个岛。

2.6.2) 跨岛出现在电源岛与地岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)的一个电源岛中间有一块地岛,且第四层的PCB走线必须跨过这两个岛。

如图2.6-2所示。

2.6.3) 跨岛出现在地岛与地层之间。

此时时钟线在第一层PCB走线,第二层(地层)的中间有一块地岛,且第一层的PCB走线必须跨过地岛,相当于地线被中断。

如图2.6-3所示。

2.6.4) 时钟线下面没有铺铜。

若条件限制实在做不到不穿岛,保证频率大于等于66M 的时钟线不穿岛,频率小于66M的时钟线若穿岛,必须加一个去耦电容形成镜像通路。

在两个电源岛之间并靠近跨岛的时钟线,放置一个0.1UF的电容。

1.0 目的规范MI制作及处理顾客文件的标准,以便准确、及时地指导和服务生产。

2.0 范围适用于工程部MI的制作,对顾客资料进行工程处理、检查(包括NOPE单)。

3.0 职责工程制作人员依据本规范对顾客资料进行工程制作、检查、MI制作(本规范与顾客的要求发生冲突时,应以顾客要求为准,但顾客要求应符合本公司的生产、工艺能力,如超出则应按相关程序进行问题反馈)。

在此过程中应遵循“尊重顾客设计意图”的总原则,对顾客文件的改动影响到其电气性能、物理使用性能时,应使顾客清楚知悉,并有顾客书面确认,或根据顾客的要求进行相应的改动。

4.0 工作流程5.0 工程处理要求及标准5.1 顾客资料5.1.1顾客资料的类型顾客资料包括CAD文件:PROTEL FOR DOS & WINDOWS 系列(98,99,99se,dxp),PADS2000,POWERPCB系列,ORCAD(ORCAD设计的文件需提供元件面正面线路的图纸以便核对)。

光绘文件:GERBER (RS-274-D & RS-274-X) Barco格式,孔文件:EXCELLON 孔位图。

5.1.2顾客资料的检查顾客资料内容应完整、一致,顾客资料与产品资料应一致,同时顾客的要求应满足公司ERP中《能力查询》要求,如出现不完整、不一致应按相关程序进行问题反馈,如有超出能力则由公司高层进行评审。

5.1.3 顾客文件的转换及调入5.1.3.1顾客文件类型的识别1)光绘文件:可直接在光绘机上绘制的文件,其特点在于其由坐标、G指令、D码(光圈)组成。

通过使用编辑软件或程序管理软件如WINDOWS COMMANDER的F3(View)功能对文件的查看来判断顾客提供的是否为光绘文件。

2)对于提供的非光绘文件根据文件后缀名和文件头可判断使用何种软件进行转换,其与产品资料上文件格式和版本号不一致时以产品资料信息为准。

另外其他设计的软件如AUTOCAD软件设计的文件,工程制作处理时此类文件需发给顾客确认或让顾客提供GERBER 格式文件。

PCB工艺设计规范1.目的规范产品的PCB工艺设计,规定PCB工艺设计的相关参数,使得PCB的设计满足可生产性、可测试性、安规、EMC、EMI等的技术规范要求,在产品设计过程中构建产品的工艺、技术、质量、成本优势。

2.适用范围本规范适用于所有电了产品的PCB工艺设计,运用于但不限于PCB的设计、PCB投板工艺审查、单板工艺审查等活动。

本规范之前的相关标准、规范的内容如与本规范的规定相抵触的,以本规范为准。

3.定义导通孔(via):一种用于内层连接的金属化孔,但其中并不用于插入元件引线或其它增强材料。

盲孔(Blind via):从印制板内仅延展到一个表层的导通孔。

埋孔(Buried via):未延伸到印制板表面的一种导通孔。

过孔(Through via):从印制板的一个表层延展到另一个表层的导通孔。

元件孔(Component hole):用于元件端子固定于印制板及导电图形电气联接的孔。

Stand off:表面贴器件的本体底部到引脚底部的垂直距离。

4.引用/参考标准或资料TS—S0902010001 <<信息技术设备PCB安规设计规范>>TS—SOE0199001 <<电子设备的强迫风冷热设计规范>>TS—SOE0199002 <<电子设备的自然冷却热设计规范>>IEC60194 <<印制板设计、制造与组装术语与定义>> (Printed Circuit Board design manufacture and assembly-terms and definitions)IPC—A—600F <<印制板的验收条件>> (Acceptably of printed board)IEC609505.规范内容5.1 PCB板材要求5.1.1确定PCB使用板材以及TG值确定PCB所选用的板材,例如FR—4、铝基板、陶瓷基板、纸芯板等,若选用高TG值的板材,应在文件中注明厚度公差。

电路板emi设计一、什么是电路板EMI设计?电路板EMI(Electromagnetic Interference)设计是指在电路板设计过程中,考虑到电磁干扰的问题,采取相应的措施来减少或避免电磁干扰对其他设备或系统的影响。

二、为什么需要进行电路板EMI设计?1. 法规要求:各国针对电子设备的电磁兼容性都有相关法规和标准,如欧盟CE标准、美国FCC标准等,要求产品在使用过程中不会对其他设备造成干扰。

2. 保证产品质量:如果产品存在较强的EMI问题,可能会导致产品性能下降、寿命缩短等质量问题。

3. 提高市场竞争力:通过进行EMI设计,可以提高产品的稳定性和可靠性,增强市场竞争力。

三、如何进行电路板EMI设计?1. 布局设计:尽可能地将信号线和地线分离,并采用合适的层次布局和分区布局。

同时,在布局时还需考虑到信号传输路径的长度、方向等因素。

2. 组件选择:选择符合EMC要求的元器件,并尽可能地选用抗干扰能力强的元器件。

同时,还需注意元器件的布局和连接方式。

3. 地线设计:地线是电路板EMI设计中最重要的因素之一。

需要确保地线尽可能宽且连续,并且各个部分之间要进行良好的连接。

4. 滤波器设计:在电路板上添加合适的滤波器可以有效地减少EMI问题,如降噪电容、滤波电感等。

5. 接口设计:对于涉及到接口的部分,需要采用合适的防干扰措施,如添加磁珠、使用屏蔽罩等。

6. 仿真测试:在进行实际生产前,需要进行仿真测试,以验证电路板EMI设计的效果是否符合预期。

四、常见的EMI问题及解决方案1. 信号串扰:信号线和地线之间距离过近或者布局不当可能会导致信号串扰。

解决方案包括增加信号线和地线之间距离、采用合适的层次2. 辐射干扰:较高频率的信号可能会通过空气传播而产生辐射干扰。

解决方案包括添加屏蔽罩、采用合适的滤波器等。

3. 接口干扰:接口部分容易受到外部干扰。

解决方案包括添加磁珠、使用屏蔽罩等。

4. 地线问题:地线不良可能会导致信号串扰、辐射干扰等问题。

EMI相关PCB布局布线规则引言电磁干扰(Electromagnetic Interference,简称EMI)是在电路板(PCB)设计中常遇到的问题。

它可能导致信号质量下降,甚至对整个电子系统造成严重的损坏。

为了有效减少EMI对电子系统的干扰,我们需要遵循一定的PCB布局布线规则。

EMI的来源首先,我们需要了解EMI的来源。

EMI可能来自以下几个方面:1.高频信号:在高频信号传输过程中,电流和电压变化迅速,容易产生电磁辐射。

2.快速开关:当快速开关的电源或信号线上出现较大的电流变化时,也会产生较强的辐射。

3.地线回流:当大电流通过地线返回电源时,也会产生较强的辐射。

4.辐射天线:射频电路中的辐射天线可能会通过电磁波和其他设备进行干扰。

PCB布局布线规则为了有效降低EMI的干扰,我们可以遵循以下几个PCB布局布线规则:1. 地线规划地线是减少EMI的关键。

正确规划地线布局可以提供低阻抗回路,减少回流噪音。

以下是地线布局的一些建议:•使用星型接地:将所有地线连接到一个共同的地点,以避免形成环路。

•保持短接:最小化地线的长度,避免地线成为天线。

•分离模拟和数字地线:为模拟和数字电路分别设计独立的地线,以减少干扰交叉。

•分层地线:根据电路需求,将地线分为不同的层次,以减少干扰。

2. 信号与电源线分离将信号线和电源线分离布局可以降低互相干扰的可能性。

以下是一些建议:•远离电源线:尽量将信号线远离电源线,以减少电磁干扰。

•使用屏蔽线:对于高频信号线,使用屏蔽线可以有效减少互相干扰。

•增加地隔离:在电源和信号地之间增加地隔离层,以减少共地干扰。

3. 电源和地面平面电源和地面平面是减少EMI的重要设计元素。

以下是一些建议:•使用整片平面:在PCB设计中尽量使用整片电源与地面平面,减少回流干扰。

•分离模拟和数字平面:为模拟和数字电路分别设计独立的电源平面,以减少干扰交叉。

•避免孔渗透:在电源和地面平面上避免使用过多的孔,以防止干扰的穿透。

规范MI 制作及处理顾客文件的标准,以便准确、及时地指导和服务生产。

2.0 范围适用于工程部MI 的制作,对顾客资料进行工程处理、检查(包括NOPE 单)。

3.0 职责工程制作人员依据本规范对顾客资料进行工程制作、检查、MI 制作(本规范与顾客的要求发生冲突时,应以顾客要求为准,但顾客要求应符合本公司的生产、工艺能力,如超出则应按相关程序进行问题反馈).在此过程中应遵循“尊重顾客设计意图”的总原则,对顾客文件的改动影响到其电气性能、物理使用性能时,应使顾客清楚知悉,并有顾客书面确认,或根据顾客的要求进行相应的改动.4.0 工作流程5.0 工程处理要求及标准5。

1 顾客资料5.1.1顾客资料的类型顾客资料包括CAD 文件:PROTEL FOR DOS & WINDOWS 系列(98,99,99se,dxp ),PADS2000,POWERPCB 系列,ORCAD(ORCAD 设计的文件需提供元件面正面线路的图纸以便核对).光绘文件:GERBER (RS —274-D & RS-274—X) Barco 格式,孔文件:EXCELLON 孔位图。

5.1.2顾客资料的检查顾客资料内容应完整、一致,顾客资料与产品资料应一致,同时顾客的要求应满足公司ERP 中《能力查询》要求,如出现不完整、不一致应按相关程序进行问题反馈,如有超出能力则由公司高层进行评审。

5.1.3 顾客文件的转换及调入5.1。

3.1顾客文件类型的识别1)光绘文件:可直接在光绘机上绘制的文件,其特点在于其由坐标、G 指令、D 码(光圈)组成。

通过使用编辑软件或程序管理软件如WINDOWS COMMANDER 的F3(View )功能对文件的查看来判断顾客提供的是否为光绘文件。

2) 对于提供的非光绘文件根据文件后缀名和文件头可判断使用何种软件进行转换,其与产品资料上文件格式和版本号不一致时以产品资料信息为准。

认或让顾客提供GERBER 格式文件。

PCB电路板 EMI设计规范及步骤

来源:华强PCB

1 、IC的电源处理

1.1)保证每个IC的电源PIN都有一个0.1UF的去耦电容,对于BGA CHIP,要求在BGA 的四角分别有0.1UF、0.01UF的电容共8个。

对PCB走线的电源尤其要注意加滤波电容,如VTT等。

这不仅对稳定性有影响,对EMI也有很大的影响。

2、时钟线的处理

2.1)建议先走时钟线。

2.2)频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个。

2.3)频率小于66M的时钟线,每条过孔数不要超过3个,平均不得超过2.5个

2.4)长度超过12inch的时钟线,如果频率大于20M,过孔数不得超过2个。

2.5)如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。

旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过

300MIL。

图2.5-1过孔处的旁路电容

2.6)所有时钟线原则上不可以穿岛。

下面列举了穿岛的四种情形。

2.6.1) 跨岛出现在电源岛与电源岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)有两个电源岛,且第四层的PCB走线必须跨过这两个岛。

2.6.2) 跨岛出现在电源岛与地岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)的一个电源岛中间有一块地岛,且第四层的PCB走线必须跨过这两个岛。

如图2.6-2所示。

2.6.3) 跨岛出现在地岛与地层之间。

此时时钟线在第一层PCB走线,第二层(地层)的中间有一块地岛,且第一层的PCB走线必须跨过地岛,相当于地线被中断。

如图2.6-3所示。

2.6.4) 时钟线下面没有铺铜。

若条件限制实在做不到不穿岛,保证频率大于等于66M的时钟线不穿岛,频率小于66M的时钟线若穿岛,必须加一个去耦电容形成镜像通路。

在两个电源岛之间并靠近跨岛的时钟线,放置一个0.1UF的电容。

2.7)当面临两个过孔和一次穿岛的取舍时,选一次穿岛。

2.8)时钟线要远离I/O一侧板边500MIL以上,并且不要和I/O线并行走,若实在做不到,时钟线与I/O口线间距要大于50MIL。

2.9)时钟线走在第四层时,时钟线的参考层(电源平面)应尽量为时钟供电的那个电源面上,以其他电源面为参考的时钟越少越好,另外,频率大于等于66M的时钟线参考电源面必须为

3.3V电源平面。

2.10)时钟线打线时线间距要大于25MIL。

2.11)时钟线打线时进去的线和出去的线应该尽量远。

尽量避免类似图A和图C所示的打

线方式,采用类似图B和图D的打线方式,若时钟线需换层,避免采用图E的打线方式,采用图F的打线方式。

2.12) 时钟线连接BGA等器件时,若时钟线换层,尽量避免采用图G的PCB走线形式,过孔不要在BGA下面走,最好采用图H的PCB走线形式。

2.13) 注意各个时钟信号,不要忽略任何一个时钟,包括AUDIO CODEC的AC_BITCLK,尤其注意的是FS3-FS0,虽然说从名称上看不是时钟,但实际上跑的是时钟,要加以注意。

2.14) Clock Chip上拉下拉电阻尽量靠近Clock Chip。

3. I/O口的处理

3.1) 各I/O口包括PS/2、USB、LPT、COM、SPEAK OUT、 GAME分成一块地,最左

与最右与数字地相连,宽度不小于200MIL或三个过孔,其他地方不要与数字地相连。

3.2)若COM2口是插针式的,尽可能靠近I/O地。

3.3)I/O电路EMI器件尽量靠近I/O SHIELD。

3.4) I/O口处电源层与地层单独划岛,且Bottom和TOP层都要铺地,不许信号穿岛(信

号线直接拉出PORT,不在I/O PORT中长距离PCB走线)。

给出了I/O口处理的参考示意图。

4. 几点说明

A.对EMI PCB设计规范,PCB设计工程师要严格遵守,EMI工程师有检查的权力,违背EMI PCB设计规范而导至EMI测试FAIL,责任由PCB设计工程师承担。

B.EMI工程师对PCB设计规范负责,对严格遵守EMIPCB设计规范,但仍然EMI测试FAIL,EMI工程师有责任给出解决方案,并总结到EMIPCB设计规范中来。

C.EMI工程师对每一个外设口的EMI测试负有责任,不可漏测。

D.每个PCB设计工程师有对该PCB设计规范作修改的建议权和质疑的权力。

EMI工程师有责任回答质疑,对工程师的建议通过实验后证实后加入PCB设计规范。

E.EMI工程师有责任降低EMIPCB设计的成本,减少磁珠的使用个数。