哈尔滨工业大学数字电路考研真题和答案

- 格式:docx

- 大小:505.21 KB

- 文档页数:8

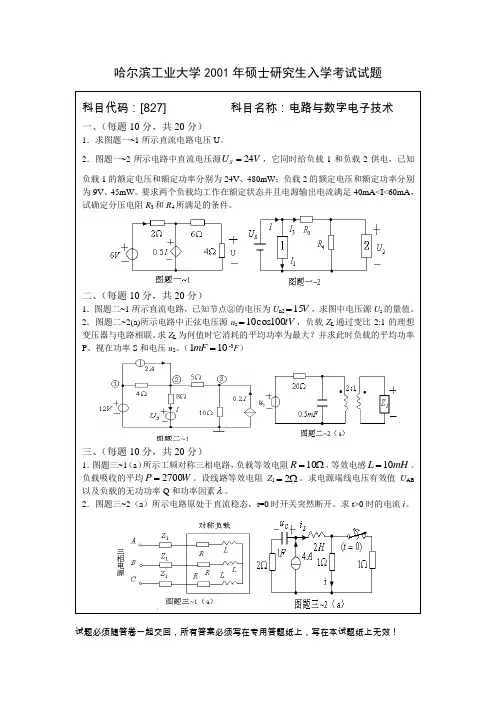

哈尔滨工业大学2001年硕士研究生入学考试试题试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!34(每题10分,共20分)三、(每题10分,共20分)图题三~1(a )所示工频对称三相电路,负载等效电阻负载吸收的平均W P 2700=。

设线路等效电阻试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!哈尔滨工业大学2002年硕士研究生入学考试试题试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!34(每题10分,共20分)三、(每题10分,共20分)图题三~1(a )所示工频对称三相电路,负载等效电阻负载吸收的平均W P 2700=。

设线路等效电阻试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!哈尔滨工业大学2003年硕士研究生入学考试试题试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!34(每题10分,共20分)2三、(每题10分,共20分)图题三~1(a )所示工频对称三相电路,负载等效电阻W P 2700=试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!哈尔滨工业大学2004年硕士研究生入学考试试题试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!所示电路中运算放大器为理想运算放大器,求该二端口的电阻参数矩阵所示正弦交流电路,已知︒∠=∙01I A ,求电压∙U 及整个电路吸收的有功功试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!哈尔滨工业大学2005年硕士研究生入学考试试题试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!试题必须随答卷一起交回,所有答案必须写在专用答题纸上,写在本试题纸上无效!2.图题二~2所示电路,V wt wt u S )]2cos(25)cos(2910[++=,Ω=10R ,Ω=91wL ,Ω=32wL ,Ω=12)(1wC 。

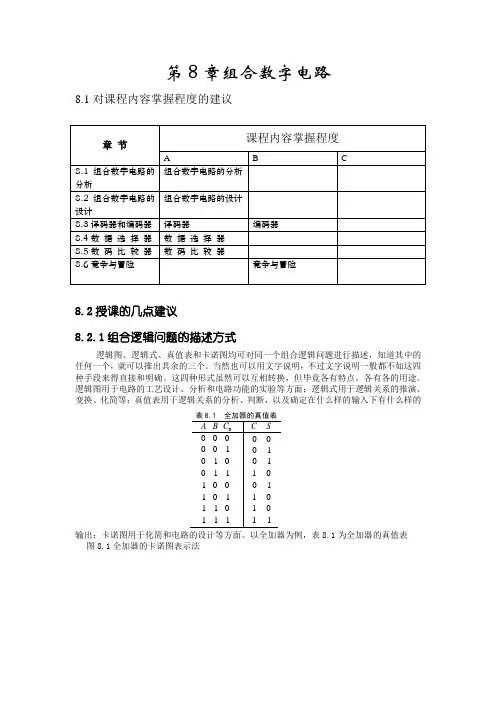

第8章组合数字电路8.1对课程内容掌握程度的建议8.2授课的几点建议8.2.1组合逻辑问题的描述方式逻辑图、逻辑式、真值表和卡诺图均可对同一个组合逻辑问题进行描述,知道其中的任何一个,就可以推出其余的三个。

当然也可以用文字说明,不过文字说明一般都不如这四种手段来得直接和明确。

这四种形式虽然可以互相转换,但毕竟各有特点,各有各的用途。

逻辑图用于电路的工艺设计、分析和电路功能的实验等方面;逻辑式用于逻辑关系的推演、变换、化简等;真值表用于逻辑关系的分析、判断,以及确定在什么样的输入下有什么样的输出;卡诺图用于化简和电路的设计等方面。

以全加器为例,表8.1为全加器的真值表 图8.1全加器的卡诺图表示法表8.1 全加器的真值表1SC B A C 00101001100000010110111101111111100000010000111( )a 10BC 0A 1111全加器的和S10000111( )b 10B C 0A1111全加器的进位C图8.1全加器的卡诺图全加器的逻辑式:00(1,2,4,7)S AC BC C C ABC m =+++=∑00(3,5,6,7)C BC AC AB m =++=∑全加器的逻辑图如图8.2所示B AC图8.2 全加器的逻辑图全加器是一个比较有代表性的组合数字电路,在后面中规模集成电路数据选择器应用设计、ROM 应用中是以此为例进行讲解的,因此,应对全加器的逻辑描述熟练掌握。

8.2.2组合逻辑电路的分析组合数字电路的框图如图8.3所示,每一个输出都是一个组合逻辑函数。

),,,,(12111n n X X X X f P -=Λ),,,,(12122n n X X X X f P -=Λ ……),,,,(121n n m m X X X X f P -=Λ在本章中要讨论四个问题,组合数字电路的分析;组合数字电路的设计;通用组合数字电路的应用和组 图8.3 组合数字电路框图在分析之前,要对电路的性质进行判断,是否是组合数字电路,如果是,则按组合数字电路的分析方法进行。

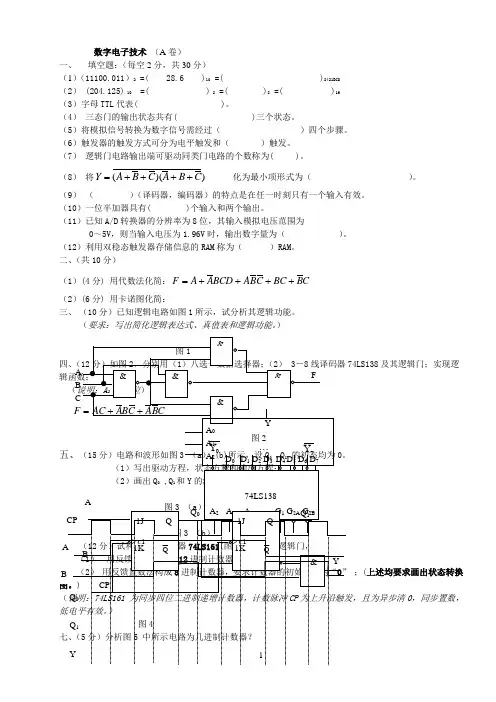

数字电子技术 (A 卷)一、 填空题:(每空2分,共30分) (1)(11100.011)2 =( 28.6 )10 =( )8421BCD (2) (204.125) 10 =( ) 2 =( )8 =( )16 (3)字母TTL 代表( )。

(4) 三态门的输出状态共有( )三个状态。

(5)将模拟信号转换为数字信号需经过( )四个步骤。

(6)触发器的触发方式可分为电平触发和( )触发。

(7) 逻辑门电路输出端可驱动同类门电路的个数称为( )。

(8) 将))((C B A C B A Y ++++= 化为最小项形式为( )。

(9) ( )(译码器,编码器)的特点是在任一时刻只有一个输入有效。

(10)一位半加器具有( )个输入和两个输出。

(11)已知A/D 转换器的分辨率为8位,其输入模拟电压范围为0~5V ,则当输入电压为1.96V 时,输出数字量为( )。

(12)利用双稳态触发器存储信息的RAM 称为( )RAM 。

二、(共10分) (1)(4分) 用代数法化简:C B BC C B A BCD A A F ++++=(2)(6分) 用卡诺图化简: 三、 (10分)已知逻辑电路如图1所示,试分析其逻辑功能。

(要求:写出简化逻辑表达式、真值表和逻辑功能。

)图1四、(12分)如图2,分别用(1)八选一数据选择器;(2) 3-8线译码器74LS138及其逻辑门;实现逻辑函数: (说明:A 2 为高位) C B A C B A AC F ++=五、(15分)电路和波形如图3 (a ),(b)所示,设Q 0 ,Q 1 的初态均为0。

(1)写出驱动方程,状态方程和输出方程;(2)画出Q 0 ,Q 1和Y 的波形(直接画在本试卷上)。

图3 (a )图3 (b )六、(12分)试利用集成计数器74LS161(图4)和必要的逻辑门, (1) 用反馈清零法构成12进制计数器; (2) 用反馈置数法构成8进制计数器,要求计数器的初始状态为“0” ;(上述均要求画出状态转换图。

哈工大数电2000-2021打印哈尔滨工业大学硕士研究生入学考试试题二OOO 年数字逻辑电路试题一、回答下列各题(每小题5分,共25分) 1 写出图1所示电路的逻辑表达式。

A B Rc Rb 图1+Ec T �� FCP D1 Q1 D2 Q2 D3 Q3 D4 Q4 C D 图22 移位寄存器型计数器如图2所示,若起始状态为Q1Q2Q3Q4=0001,请写出从Q4输出一个周期的m序列。

3 画出下图电路在CP和D的作用下,Q1、Q2的输出波形,初态为00。

Sd Rd Sd Rd二、由8选1数据选择器CT4151构成的电路如下图所示,请写出该电路输出函数Y的逻辑表达式,以最小项之和(Σm(┅,┅, ))形式表示。

如果要实现逻辑函数Y=Σm(1,2,5,7,8,10,14,15),则图中接线应怎样改动?(10分)三、某大厅有一盏灯和分布在不同位置的四个开关(A、B、C、D)。

试利用四选一数据选择器为大厅设计一个电灯开关控制逻辑电路,使得人们可以在大厅的任何一个位置控制灯的亮或灭。

例如:可以用A开关打开,然后用B(或C、D、A)开关熄灭。

(15分)CP四、脉冲分配电路一般由计数器和译F1码电路组成,试用D触发器和与F2 非门设计如图所示波形的脉冲分F3F4配器电路。

(15分) F5 五、试用JK触发器和门电路设计一自动售饮料机的时序控制电路。

其投币口每次只能投入一枚5角或1元的硬币,投入1.5元硬币后,自动售货机给出一瓶饮料。

如投入两元硬币,则在给出一瓶饮料的同时,退出一枚5角硬币。

(20分)要求:1 状态设置合理,状态图标注清楚; 2 画出逻辑电路图;3 检验自启动。

39哈尔滨工业大学硕士研究生入学考试试题二OO一年数字逻辑电路试题一、解答下列各题(每小题5分,共25分)1. 将D触发器转换成JK触发器,画出逻辑电路图。

2. 试画出111序列检测器的状态图,当连续输入三个1时输出为1,否则输出为0。

数字电路考研试题及答案一、选择题(每题2分,共10分)1. 在数字电路中,以下哪个选项不是基本逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D2. 一个触发器的输出Q在时钟脉冲的上升沿从0变为1时,输出Q的状态会如何变化?A. 保持不变B. 翻转C. 变为0D. 变为1答案:B3. 在数字电路设计中,以下哪个选项不是常用的编码方式?A. 二进制编码B. 格雷码C. BCD码D. 十进制编码答案:D4. 以下哪个选项不是数字电路中常用的存储元件?A. 触发器B. 寄存器C. 计数器D. 运算放大器答案:D5. 在数字电路中,同步电路与异步电路的主要区别是什么?A. 同步电路使用时钟信号,异步电路不使用B. 同步电路不使用时钟信号,异步电路使用C. 同步电路速度更快D. 异步电路速度更快答案:A二、填空题(每题2分,共10分)1. 一个4位二进制计数器可以表示的最大十进制数是______。

答案:152. 如果一个逻辑门的输入端悬空,其逻辑状态通常被视为______。

答案:高电平3. 在数字电路中,一个D触发器的D输入端表示数据输入,那么Q端表示______。

答案:数据输出4. 一个8位移位寄存器可以存储的二进制数的最大位数是______。

答案:85. 在数字电路中,一个简单的同步计数器的计数范围是从0计数到______。

答案:2^n - 1(其中n是计数器的位数)三、简答题(每题10分,共20分)1. 请简述数字电路与模拟电路的主要区别。

答案:数字电路主要处理离散的数字信号,具有确定的高低电平状态,而模拟电路处理连续变化的信号,信号值可以在一个范围内连续变化。

数字电路使用二进制编码,而模拟电路不需要编码。

数字电路抗干扰能力强,易于集成,而模拟电路则相反。

2. 解释什么是时序逻辑电路,并给出一个实际应用的例子。

答案:时序逻辑电路是一种数字电路,其输出不仅取决于当前的输入,还取决于电路的当前状态。

哈尔滨工业大学一九九七年硕士研究生考试试题数字逻辑电路一. (10分)1. 由双极型三极管构成放大器,在正常工作状态下测得管子三个引脚对地的电位为V1=0伏,V2=-6伏,V3=-5.3伏,问此管是什么类型管?管脚1,2,3各是什么极?2. 放大电路如图1所示。

试说明稳定静态工作点Q 的物理过程。

3. 由理想运放构成如图2电路。

其中R 1=R 4,R 2=R 3。

(1) 其增益函数表达式 A(j ω)=Vo/Vi ; (2) 其直流增益 ;(3) 求3dB 上限频率ωH 。

二. 放大电路如图3所示,已知晶体管的参数为:hfe1=hfe2=49, rbb ’=300Ω, hoe=hre=0.静态工作电流:IcQ1=IcQ2=1 mA. 电容对交流可认为短路。

求输入电阻Ri, 输出电阻R0和电压增益Av 。

(10分)R 6图1 图2三.回答下列各题(20分)1. 在下图所示电路中,M1为TTL 与非门,VoH=3.6V, 最大拉电流Ilmax=13mA, 要实现Rb 应 > ( ) Rb 应 < ( )2. 在下图所示电路中M1,M2,M3为TTL OC 门,M4为TTL 与非门,V1,V2为二只20k Ω/V 的电压表,问:S1断开 V1=( ) V2=( )S1合上 A1A2, B1B2, C1C2全为低 V1=( ) V2=( ) S1合上 A1A2为高,B1B2, C1C2为低 V1=( ) V2=( ) 3. 写出下面电路真值表及逻辑表达式。

4. 设计一个序列信号检测器用以及检测0101。

当检测到此码组时输出为1,否则输出为0。

只画出状态转换图。

F1=AB ,F2=AB四.试分别用八选一数据选择器、PLA 设计下列函数。

( 10分) F =)14,13,11,9,7,6,5,4,3(4m五.试用最少数目的与非门将下图(a),(b),(c)所示各电路合并成一个多输出端的组合网络,要求输入变量仅以原变量出现。

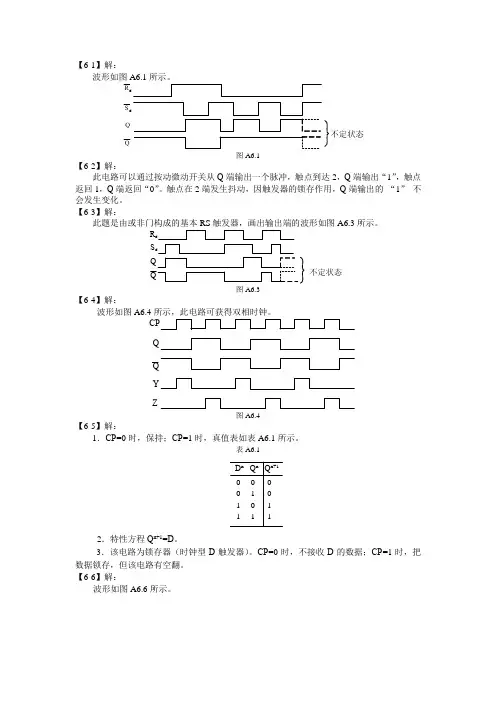

【6-1】解:波形如图A6.1所示。

R d S d QQ不定状态图A6.1【6-2】解:此电路可以通过按动微动开关从Q 端输出一个脉冲,触点到达2,Q 端输出“1”,触点返回1,Q 端返回“0”。

触点在2端发生抖动,因触发器的锁存作用,Q 端输出的 “1” 不会发生变化。

【6-3】解:此题是由或非门构成的基本RS 触发器,画出输出端的波形如图A6.3所示。

d S dR不定状态图A6.3【6-4】解:波形如图A6.4所示,此电路可获得双相时钟。

Q Q CPY Z图A6.4【6-5】解:1.CP =0时,保持;CP =1时,真值表如表A6.1所示。

表A6.1D n Q n Q n+1 0 0 0 0 1 0 1 0 1 1 1 12.特性方程Q n+1=D 。

3.该电路为锁存器(时钟型D 触发器)。

CP =0时,不接收D 的数据;CP =1时,把数据锁存,但该电路有空翻。

【6-6】解:波形如图A6.6所示。

CP J KJ K QQ图A6.6【6-7】解:波形如图6.7所示。

D Q图A6.7【6-8】解:D 触发器转换为J-K 触发器 n n n n D J Q K Q J Q K Q =+=⋅ 如图A6.8(a)所示。

JK 触发器转换为D 触发器 J D =,K D = 如图A6.8(b)所示。

QJCPQD(a) (b)图A6.8【6-9】解:1.CP 作用下的输出Q 0 Q 1和Z 的波形如图; 2、Z 对CP 三分频。

CP Q Q Z01图A6.9【6-10】解:输出波形如图6.10所示。

CP A F图A6.10【6-11】解:输出波形如图A6.11所示。

CP Q A 01Q图A6.11【6-12】解:见图6.11(b)所示。

该电路A 输入每出现一次下降沿,Q 1端就输出一个宽度等于时钟周期的脉冲。

AQ0Q 1CP图A6.12。