第8章 基本逻辑电路设计_有限状态机

- 格式:pptx

- 大小:476.30 KB

- 文档页数:22

1.1概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

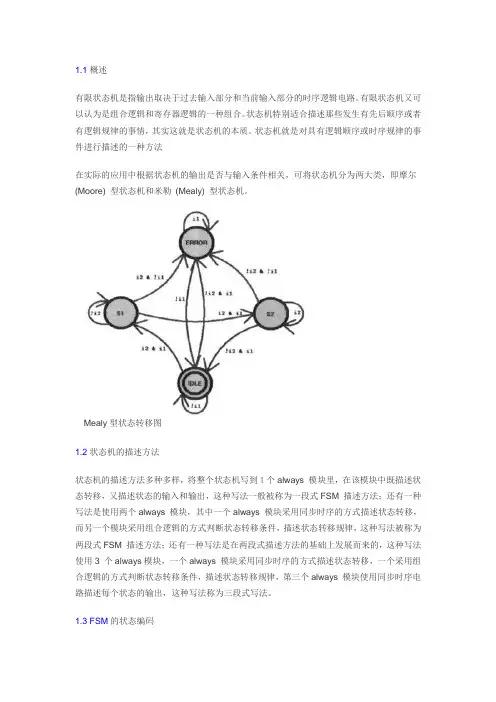

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore) 型状态机和米勒(Mealy) 型状态机。

Mealy型状态转移图1.2状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always 模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

EDA技术第八章有限状态机设计有限状态机(Finite State Machine,简称FSM)是一种用于描述和建模系统行为的数学模型。

它可以将系统的行为抽象化为一个有限的状态集合和状态间的转移关系。

在EDA(Electronic Design Automation,电子设计自动化)技术中,有限状态机设计是一项关键技术,用于设计和实现数字电路中的控制逻辑。

有限状态机设计通常包括状态定义、状态转移关系以及输出逻辑的设计。

首先,需要明确定义系统的状态集合。

每个状态代表了系统在特定时间点的行为和状态。

状态可以是简单的布尔值,也可以是复杂的数据结构。

在有限状态机设计中,对状态的定义要具体明确,以便于后续的状态转移关系和输出逻辑的设计。

接下来,需要定义状态间的转移关系。

转移关系决定了系统在不同状态间的切换条件和方式。

可以通过绘制状态转移图或者使用状态转移表的方式来描述状态间的转移关系。

状态转移关系需要保证系统在任意时间点都有确定性的行为,即从一个状态到另一个状态的转移是唯一确定的。

最后,需要设计输出逻辑。

输出逻辑定义了系统在不同状态下的输出行为。

输出可以是控制信号,也可以是数据等其他形式。

输出逻辑的设计需要根据系统的需求和功能来确定,确保在不同状态下的输出能够满足系统的要求。

在有限状态机设计中,可以使用硬件描述语言(HardwareDescription Language,简称HDL)来实现系统的控制逻辑。

常见的HDL语言包括VHDL和Verilog。

通过使用HDL,可以将有限状态机的设计转化为硬件电路的实现,从而在芯片级别上实现系统的功能。

有限状态机设计在EDA技术中起到了至关重要的作用。

它可以帮助工程师更好地理解和描述系统的行为,从而优化和改进设计。

同时,有限状态机设计可以提高设计的灵活性和可重用性,使得设计更易于维护和扩展。

总之,有限状态机设计是EDA技术中的关键技术之一、它通过定义状态集合、状态转移关系和输出逻辑,帮助工程师实现系统的控制逻辑。

有限状态机和时序逻辑电路

有限状态机和时序逻辑电路是数字电路设计中重要的概念。

有限状态机是一种模型,用于描述系统在不同状态下的行为。

它由状态集、转移函数和输出函数组成。

时序逻辑电路是一种电路,它的输出不仅取决于当前输入,还取决于之前输入的历史。

这些电路通常用于计数器、时序控制器等应用中。

在有限状态机中,状态是有限的,每个状态都有对应的行为和输出。

通过转移函数,状态可以从一个状态转移到另一个状态。

输出函数负责在每个状态中输出相应的值或信号。

有限状态机可以用于控制系统、序列检测等应用中。

时序逻辑电路是一种与时间有关的电路。

在这种电路中,输出不仅取决于当前输入,还取决于过去的输入。

这些电路可以用于计数器、时序控制器、存储器等应用中。

时序逻辑电路通常包括时钟信号、寄存器、计数器等元件。

总之,有限状态机和时序逻辑电路是数字电路设计中不可或缺的概念。

它们可以用于控制系统、序列检测、计数器、时序控制器等应用中。

熟悉这些概念对于数字电路设计师来说非常重要。

- 1 -。

实验八利用有限状态机进行时序逻辑的设计实验目的1.掌握利用有限状态机实现一般时序逻辑分析的方法;2.进掌握用V erilog编写的有限状态机的标准模板。

实验内容1.学习V erilog HDL 设计课件。

2.设计一个串行数据检测器。

要求是:连续4个或4个以上为1时输出为1,其他输入情况下为0。

实验原理参考V erilog HDL 学习课件。

在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在V erilogHDL硬件描述语言中,这种设计方法得到进一步的发展。

通过V erilog HDL 提供的语句,可以直观地设计出更为复杂的时序逻辑的电路。

关于有限状态机的设计方法在教材中已经作了较为下面是一个简单指令译码电路的设计示例。

该详细的阐述,在此就不赘述了。

下例是一个简单的状态机设计,功能是检测一个5位二进制序列“10010”。

考虑到序列重叠的可能,有限状态机共提供了8个状态(包括初始状态IDLE)。

模块源代码://----------文件名seqdet.v----------------module seqdet(x,z,clk,rst,state);input x,clk,rst;output z;output[2:0] state;reg[2:0] state;wire z;parameter IDLE=`d0,A='d1,B='d2,C='d3,D='d4,E='d5,F='d6,G='d7;assign z=(state==E&&x==0)?1:0;always @(posedge clk) if(! rst)beginstate<=IDLE;endelsecasex(state)IDLE:if(x==1)begin state<=A;endA:if(x==0)beginstate<=B;endB:if(x==0)beginstate<=C;endelsebeginstate<=F;endC: if(x==1)beginstate<=D;endelsebegnstate<=G;endD:if(x==0)beginstate<=E;endelsebeginstate<=A;endE:if(x==0)beginstate<=C;endelsebeginstate<=A;endF:if(x==1)beginstate<=A;endelsebeginstate<=B;endG:if(x==1)beginstate<=F;enddefault:state=IDLE;endcaseendmodule实验步骤1.在教师的指导下,学习V erilog HDL课件。

第8章有限状态机设计技术有限状态机及其设计技术是实用数字系统设计中的重要组成部分,也是实现高效率、高可靠和高速控制逻辑系统的重要途径。

广义而论,只要是涉及触发器的电路,无论电路大小,都能归结为状态机。

因此,对于数字系统设计工程师,面对的只要是时序电路设计,状态机的概念则是必须贯穿于整个设计始终的最基本的设计思想和设计方法论;只有从电路状态的角度去考虑,才能从根本上把握可靠,高效的时序逻辑的设计关键。

在现代数字系统设计中,状态机的设计对系统的高速性能、高可靠性、稳定性都具有决定性的作用。

读者对于此章的学习必须给于高度的关注。

有限状态机应用广泛,特别是对那些操作和控制流程非常明确的系统设计,在数字通信领域、自动化控制领域、CPU设计领域以及家电设计领域都拥有重要的和不可或缺的地位。

尽管到目前为止,有限状态机的设计理论并没有增加多少新的内容,然而面对先进的EDA工具、日益发展的大规模集成电路技术和强大的硬件描述语言,有限状态机在其具体的设计和优化技术以及实现方法上却有了许多新的内容和新的实现方法。

本章重点介绍用Verilog设计不同类型有限状态机的方法,同时考虑EDA工具和设计实现中许多必须重点关注的问题,如优化、毛刺的处理及编码方式等方面的问题。

8.1 Verilog状态机的一般形式就理论而言,任何时序模型都可以归结为一个状态机。

如只含一个D触发器的二分频电路或一个普通的4位二进制计数器都可算作一个状态机;前者是两状态型状态机,后者是16状态型状态机,都属于一般状态机的特殊形式。

但这些并非出自明确的自觉的设计目的和合理的状态机设计方案而导致的时序模块,未必能成为一高速、高效、稳定、控制流畅、修改便捷和功能目标明确的真正意义上的状态机。

基于现代数字系统设计技术自觉意义上的状态机的HDL表述形态和表述风格具有一定的典型性和格律化。

正是据此,现代EDA的综合器能从不同表述形态的HDL程序中轻易地萃取出(Extract)状态机设计,并加以多侧面多目标和多种形式的优化;甚至还能能动地改变、脱离甚至不遵从设计程序文字上的表述,而按照综合器自己的方式去优化状态机的设计。