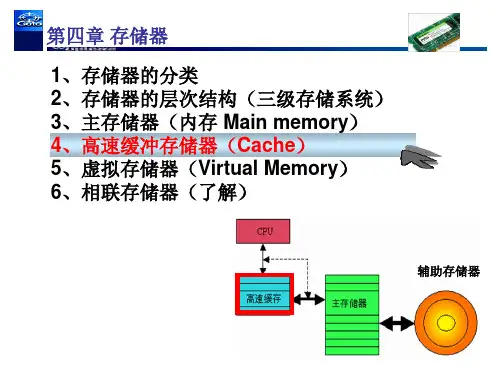

高速缓冲存储器

- 格式:ppt

- 大小:2.24 MB

- 文档页数:5

高速缓冲存储器名词解释高速缓冲存储器(CacheMemory)是计算机系统中用来加快访问速度的一种临时存储器。

它可以被看作是内存系统中一层虚拟存储器,能够有效地把系统从内存、磁盘等设备中获取的数据以及未来所需要的数据暂存到cache memory中。

简言之,cache memory是一种可用来为CPU加速数据访问速度的存储器,是由CPU直接访问的一种高速存储器。

高速缓冲存储器由三个部分组成:cache级(cache level)、cache 缓存行(cache line)和cache单元(cache cell)。

cache是一组缓存行的集合,是 cache memory最小单元。

cache是由一组相连接的 cache line成。

cache line括一组相同大小的 cache元,每个单元根据它的作用可分为三类:索引(index)、标记(tag)、数据(data)。

cache可以将源数据分成多个子集,并将其中一部分存储到cache memory 中,以便快速访问。

cache据地址映射(address mapping)原理,将一段内存区域缩小,便于数据的快速访问。

当 CPU求某条指令时,它会首先检查 cache 中是否已经缓存了这条指令,如果缓存中有,就可以从 cache 中取出该指令,省去了访问主存的时间,这样就提高了 CPU运算速度。

除此之外,高速缓冲存储器还利用了多级缓存(multi-level cache)技术,把cache memory分为多级,从而提高了 cache memory 命中率。

在这种技术下,如果一级缓存(L1 cache)中没有找到所要访问的数据,则会再到二级缓存(L2 cache)中查找。

如果L2 cache中也没有相应的数据,则会再去其他更高级的缓存中查找,直至主存中的数据被访问到。

多级缓存的出现大大提高了 cache memory性能,大大提升了整个系统的访问效率,从而使CPU能更加高效地运行程序。

3.7 高速缓冲存储器高速缓冲存储器的功能是提高CPU数据输入/输出的速率,突破所谓的存储器瓶颈问题,即CPU与存储系统间数据传送带宽限制。

高速缓冲存储器能以极高的速率进行数据的访问,但因其价格高昂,所以只在CPU和主存之间添加少量的Cache,利用程序的局部性原理来进行工作。

3.7.1 程序访问的局部性原理程序访问的局部性有两个方面的含义:时间局部性和空间局部性。

时间局部性是指最近的访问项(指令/数据)很可能在不久的将来再次被访问(往往会引起对最近使用区域的集中访问),而空间局部性是指一个进程访问的各项地址彼此很近。

换句话说,就是最近的、未来要用的指令和数据大多局限于正在用的指令和数据,或是存放在与这些指令和数据位置上邻近的单元中。

这样,就可以把目前常用或将要用到的信息预先放在存取速度最快的存储器中,从而使CPU的访问速度大大提高。

依据局部性原理,把主存储器中访问概率高的内容存放在Cache中,当CPU需要读取数据时,首先在Cache中查找是否有所需内容,如果有则直接从Cache中读取;若没有再从主存中读取该数据,然后同时送往Cache和CPU。

如果CPU需要访问的内容大多都能在Cache中找到(称为命中),则可以大大提高系统性能。

3.7.2 Cache的基本工作原理如图3-13所示给出了Cache的基本结构。

Cache和主存都被分成若干个大小相等的块,每块由若干字节组成。

由于Cache的容量远小于主存的容量,所以Cache的块数要远少于主存的块数,它保存的信息只是主存中最活跃的若干块的副本。

用主存地址的块号字段访问Cache标记,并将取出的标记和主存地址的标记字段相比较,若相等,说明访问Cac he有效,称Cache命中,若不相等,说明访问Cache无效,称Cache不命中或失效,而此时需要从主存中将该块取出至Cache中。

当CPU发出读请求时,如果Cache命中,就直接对Cac he进行读操作,与主存无关;如果Cache不命中,则仍需访问主存,并把该块信息一次从主存调入Cache内。

高速缓冲存储器cache的原理高速缓冲存储器(Cache)原理简介什么是高速缓冲存储器•高速缓冲存储器(Cache)是计算机体系结构中一种用于提高数据传输速度的存储器层次结构。

•它位于处理器和主存储器之间,作为一个中间层,存储处理器频繁使用的数据,以提供更快的访问速度。

高速缓冲存储器的工作原理1.局部性原理–高速缓冲存储器的设计基于计算机程序的局部性原理。

–局部性原理包括时间局部性和空间局部性两个方面。

–时间局部性指的是在一段时间内,CPU对某些数据的访问很频繁。

–空间局部性指的是当访问某个地址时,很可能在不久的将来还会访问附近的地址。

2.缓存工作原理–高速缓冲存储器通过存储最近使用的数据来加速访问速度。

–缓存采用一种称为缓存行的数据块单位,将主存储器中的数据缓存在缓存中。

–缓存行的大小一般为2^n字节,其中n为缓存行地址的位数。

–当CPU需要从主存储器中读取数据时,首先会检查缓存中是否有对应的缓存行。

–如果有,称为缓存命中;如果没有,称为缓存未命中。

3.缓存命中–当缓存命中时,CPU可以直接从缓存中读取数据,避免了对主存储器的访问,大大提高了访问速度。

–同时,缓存还可以缓存下一条指令,提前加载到缓存中,以等待CPU的执行。

4.缓存未命中–当缓存未命中时,需要从主存储器中读取数据,此时会引起一定的延迟。

–缓存未命中会触发缓存替换算法,将最近最少使用的缓存行替换出去,腾出空间存放新的缓存行。

5.缓存替换算法–常见的缓存替换算法有最近最久未使用(LRU)、先进先出(FIFO)和随机替换等。

–这些算法会根据缓存行的使用频率等因素来进行替换决策。

–替换算法的选择往往取决于不同的应用场景和硬件架构。

高速缓冲存储器的优势与应用•高速缓冲存储器极大地提高了计算机的性能和效率。

•它可以减少CPU对主存储器的访问次数,缩短了数据传输的时间。

•高速缓冲存储器被广泛应用于各种计算机硬件架构中,包括个人电脑、服务器和嵌入式系统等。

高速缓冲存储器cache程序的访问局部性程序的访问局部性定义在较短时间间隔内,程序产生的地址往往聚集在很小的一段地址空间内。

具体体现有两方面:时间局部性:被访问的某一存储单元,在一个较短的时间间隔内可能被再次访问;空间局部性:被访问的存储单元的邻近单元在一个较短的时间间隔内,可能也会被访问。

产生访问局部性的原因程序是由指令和数据组成的。

指令在主存中是按序存放的,存储单元是连续的,地址也是连续的,循环结构程序段或函数等子程序段再较短时间间隔内可能被重复执行,因此,指令的访问具有明显的局部化特性;数据在主存中的也是按序连续存放的,尤其是数组元素,常常被按序重复访问,因此,数据的访问也具有明显的局部化特性。

命中(Hit):若CPU访问单元所在的块在cache中,则称为命中。

命中的概率称为命中率(Hit Rate),是命中次数与访问总次数之比。

命中时,CPU在cache直接存取信息,所用的时间开销为cache的访问时间,称为命中时间(Hit Time)。

缺失(Miss):若CPU访问单元所在的块不在cache中,则称为不命中或缺失,缺失的概率称为缺失率(Miss Rate),是缺失次数与访问总次数之比。

缺失时,需要从主存读取一个主存块送cache,同时将所需信息送CPU,所用的时间开销为主存访问时间和cache访问时间之和。

通常将从主存读入一个主存块到cache的时间称为缺失损失(Miss Penalty)。

CPU在cache—主存层次的平均访问时间为。

由于程序访问的局部性特定,cache的命中率可以达到很高,接近于1,因此,即使Miss Penalty 远远大于Hit Time,但最终的平均访问时间仍可接近cache的访问时间。

cache工作流程程序执行中过程中,需要从主存取指令或读数据时,先检查cache是否命中,若命中,则直接从cache中读取信息送CPU进行运算,而不用访问主存储器;若缺失,则将访问地址内的数据送CPU进行运算,同时将当前访问的主存块复制到cache中。

简述高速缓冲存储器的工作原理

高速缓冲存储器(Cache)是位于计算机处理器和主存之间的一种存储器,其工作原理是通过预先将主存中的数据和指令复制到缓存中,并将最近访问过的数据和指令保存在缓存中。

当处理器需要读取数据或指令时,首先会检查缓存中是否存在需要的数据或指令。

如果存在,则可以直接从缓存中获取,从而加快读取速度;如果不存在,则需要从主存中获取,并将其复制到缓存中以备将来使用。

缓存的工作原理主要包括以下几个步骤:

1. 读取请求:当处理器需要读取数据或指令时,首先会发送读取请求给缓存。

2. 检查缓存:缓存会检查自身是否包含所需的数据或指令。

如果命中(hit),则直接从缓存中读取;如果未命中(miss),则进入下一步。

3. 访问主存:当缓存未命中时,会发送请求给主存,从主存中读取所需的数据或指令。

4. 更新缓存:主存返回数据或指令后,将其复制到缓存中,并更新缓存的标记信息。

5. 返回数据:最后,缓存将数据或指令返回给处理器。

通过将最常用的数据和指令保存在缓存中,可以减少处理器对主存的访问次数,从而提高计算机的性能。

高速缓存采用了较快的存储介质和更接近处理器的位置,以便更快地访问数据和指令。

同时,缓存采用了更小的容量,以节省成本,并且使用

了一些替换算法来选择替换缓存中的数据,以便能够存储更多的热点数据。

高速缓冲存储器cache的作用高速缓冲存储器(cache)是计算机系统中的一种重要组成部分,它的作用可以用来提高数据访问速度、降低数据延迟,从而提升整个系统的性能。

在计算机系统中,CPU(中央处理器)和内存之间的数据交换是非常频繁的,而高速缓存存储器的作用就是在CPU和内存之间起到一个缓冲的作用,加快数据传输的速度。

高速缓存存储器通过存储最常用的数据,将这些数据暂时保存在CPU附近,以便下次访问时可以更快地获取。

这样,当CPU需要访问某个数据时,它首先会在高速缓存中进行查找,如果找到了需要的数据,就可以直接从缓存中读取,而不需要再次访问内存。

由于高速缓存存储器的访问速度比内存快得多,因此可以大大减少CPU等待数据的时间,从而提高计算机的整体运行速度。

高速缓存存储器还可以通过预取数据的方式来提高数据访问速度。

当CPU访问某个数据时,高速缓存存储器会根据程序的局部性原理,主动将该数据所在的连续内存块中的数据一并加载到缓存中。

这样,在CPU访问下一个数据时,它已经在高速缓存中了,无需再次从内存中读取。

通过预取数据,可以减少CPU等待数据的时间,提高计算机的整体性能。

高速缓存存储器还可以通过缓存一致性协议来提高系统的性能和数据的一致性。

在多核处理器系统中,每个核都有自己的高速缓存,而它们之间又需要共享数据。

为了保证数据的一致性,高速缓存存储器会使用一种协议来保证每个核对共享数据的操作都是正确的。

这种协议可以在不同核之间进行数据的同步和通信,从而保证数据的一致性。

通过缓存一致性协议,可以提高系统的性能和数据的可靠性。

高速缓存存储器还有一种非常重要的作用,即减少对内存的访问次数。

由于内存的访问速度相对较慢,因此每次访问内存都需要耗费较多的时间。

而高速缓存存储器的访问速度比内存快得多,因此可以将CPU对内存的访问次数减少到最低限度。

通过减少对内存的访问次数,可以大大提高计算机系统的性能,降低数据访问的延迟。

高速缓存存储器在计算机系统中起到了至关重要的作用。

高速缓冲存储器cache的作用高速缓冲存储器(Cache)是计算机中一种特殊的存储器,其作用是提高计算机的运行速度和效率。

它位于CPU和主存之间,作为CPU与主存之间的缓冲区域,用来存放最近被CPU频繁访问的数据和指令。

Cache的作用主要有以下几个方面:1. 提高数据访问速度:Cache采用了更快的存取速度和更短的访问时间。

由于CPU频繁访问Cache,而Cache又位于CPU旁边,因此数据可以更快地被CPU获取到,从而提高了计算机系统的整体运行速度。

2. 减轻主存压力:主存的访问速度相对较慢,而CPU的运行速度相对较快,这就导致了CPU频繁等待主存的情况。

通过引入Cache 作为中间缓冲区域,可以将CPU需要的数据和指令预先存放在Cache中,当CPU需要时,直接从Cache中获取,减轻了对主存的访问压力。

3. 提高命中率:Cache是根据局部性原理设计的,即程序访问的数据和指令往往具有一定的局部性。

Cache通过将近期被CPU频繁访问的数据和指令存放在Cache中,提高了命中率,即CPU在Cache中找到需要的数据和指令的概率增加,从而减少了访问主存的次数,提高了系统的效率。

4. 缓解存储器层次结构之间的速度不匹配:计算机系统中,存储器的层次结构是由快速但容量较小的Cache、速度适中但容量较大的主存和速度较慢但容量最大的辅助存储器组成。

Cache的引入可以缓解存储器层次结构之间的速度不匹配问题,通过Cache将较慢的主存和辅助存储器的访问速度与CPU相匹配,提高了整个存储器层次结构的效率。

5. 提高系统吞吐量:通过提高命中率、减轻主存压力和提高数据访问速度,Cache可以提高系统的吞吐量。

吞吐量是指单位时间内完成的任务数量,Cache的引入可以减少CPU等待数据和指令的时间,从而提高了系统每单位时间内处理任务的数量,进而提高了系统的吞吐量。

高速缓冲存储器Cache在计算机系统中起到了至关重要的作用。