高速缓冲存储器

- 格式:ppt

- 大小:348.00 KB

- 文档页数:57

高速缓冲存储器名词解释高速缓冲存储器(CacheMemory)是计算机系统中用来加快访问速度的一种临时存储器。

它可以被看作是内存系统中一层虚拟存储器,能够有效地把系统从内存、磁盘等设备中获取的数据以及未来所需要的数据暂存到cache memory中。

简言之,cache memory是一种可用来为CPU加速数据访问速度的存储器,是由CPU直接访问的一种高速存储器。

高速缓冲存储器由三个部分组成:cache级(cache level)、cache 缓存行(cache line)和cache单元(cache cell)。

cache是一组缓存行的集合,是 cache memory最小单元。

cache是由一组相连接的 cache line成。

cache line括一组相同大小的 cache元,每个单元根据它的作用可分为三类:索引(index)、标记(tag)、数据(data)。

cache可以将源数据分成多个子集,并将其中一部分存储到cache memory 中,以便快速访问。

cache据地址映射(address mapping)原理,将一段内存区域缩小,便于数据的快速访问。

当 CPU求某条指令时,它会首先检查 cache 中是否已经缓存了这条指令,如果缓存中有,就可以从 cache 中取出该指令,省去了访问主存的时间,这样就提高了 CPU运算速度。

除此之外,高速缓冲存储器还利用了多级缓存(multi-level cache)技术,把cache memory分为多级,从而提高了 cache memory 命中率。

在这种技术下,如果一级缓存(L1 cache)中没有找到所要访问的数据,则会再到二级缓存(L2 cache)中查找。

如果L2 cache中也没有相应的数据,则会再去其他更高级的缓存中查找,直至主存中的数据被访问到。

多级缓存的出现大大提高了 cache memory性能,大大提升了整个系统的访问效率,从而使CPU能更加高效地运行程序。

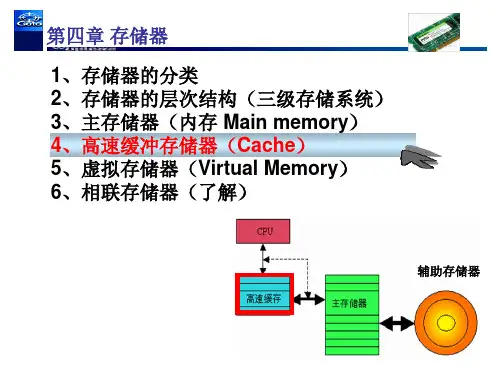

3.7 高速缓冲存储器高速缓冲存储器的功能是提高CPU数据输入/输出的速率,突破所谓的存储器瓶颈问题,即CPU与存储系统间数据传送带宽限制。

高速缓冲存储器能以极高的速率进行数据的访问,但因其价格高昂,所以只在CPU和主存之间添加少量的Cache,利用程序的局部性原理来进行工作。

3.7.1 程序访问的局部性原理程序访问的局部性有两个方面的含义:时间局部性和空间局部性。

时间局部性是指最近的访问项(指令/数据)很可能在不久的将来再次被访问(往往会引起对最近使用区域的集中访问),而空间局部性是指一个进程访问的各项地址彼此很近。

换句话说,就是最近的、未来要用的指令和数据大多局限于正在用的指令和数据,或是存放在与这些指令和数据位置上邻近的单元中。

这样,就可以把目前常用或将要用到的信息预先放在存取速度最快的存储器中,从而使CPU的访问速度大大提高。

依据局部性原理,把主存储器中访问概率高的内容存放在Cache中,当CPU需要读取数据时,首先在Cache中查找是否有所需内容,如果有则直接从Cache中读取;若没有再从主存中读取该数据,然后同时送往Cache和CPU。

如果CPU需要访问的内容大多都能在Cache中找到(称为命中),则可以大大提高系统性能。

3.7.2 Cache的基本工作原理如图3-13所示给出了Cache的基本结构。

Cache和主存都被分成若干个大小相等的块,每块由若干字节组成。

由于Cache的容量远小于主存的容量,所以Cache的块数要远少于主存的块数,它保存的信息只是主存中最活跃的若干块的副本。

用主存地址的块号字段访问Cache标记,并将取出的标记和主存地址的标记字段相比较,若相等,说明访问Cac he有效,称Cache命中,若不相等,说明访问Cache无效,称Cache不命中或失效,而此时需要从主存中将该块取出至Cache中。

当CPU发出读请求时,如果Cache命中,就直接对Cac he进行读操作,与主存无关;如果Cache不命中,则仍需访问主存,并把该块信息一次从主存调入Cache内。

高速缓冲存储器cache的原理高速缓冲存储器(Cache)原理简介什么是高速缓冲存储器•高速缓冲存储器(Cache)是计算机体系结构中一种用于提高数据传输速度的存储器层次结构。

•它位于处理器和主存储器之间,作为一个中间层,存储处理器频繁使用的数据,以提供更快的访问速度。

高速缓冲存储器的工作原理1.局部性原理–高速缓冲存储器的设计基于计算机程序的局部性原理。

–局部性原理包括时间局部性和空间局部性两个方面。

–时间局部性指的是在一段时间内,CPU对某些数据的访问很频繁。

–空间局部性指的是当访问某个地址时,很可能在不久的将来还会访问附近的地址。

2.缓存工作原理–高速缓冲存储器通过存储最近使用的数据来加速访问速度。

–缓存采用一种称为缓存行的数据块单位,将主存储器中的数据缓存在缓存中。

–缓存行的大小一般为2^n字节,其中n为缓存行地址的位数。

–当CPU需要从主存储器中读取数据时,首先会检查缓存中是否有对应的缓存行。

–如果有,称为缓存命中;如果没有,称为缓存未命中。

3.缓存命中–当缓存命中时,CPU可以直接从缓存中读取数据,避免了对主存储器的访问,大大提高了访问速度。

–同时,缓存还可以缓存下一条指令,提前加载到缓存中,以等待CPU的执行。

4.缓存未命中–当缓存未命中时,需要从主存储器中读取数据,此时会引起一定的延迟。

–缓存未命中会触发缓存替换算法,将最近最少使用的缓存行替换出去,腾出空间存放新的缓存行。

5.缓存替换算法–常见的缓存替换算法有最近最久未使用(LRU)、先进先出(FIFO)和随机替换等。

–这些算法会根据缓存行的使用频率等因素来进行替换决策。

–替换算法的选择往往取决于不同的应用场景和硬件架构。

高速缓冲存储器的优势与应用•高速缓冲存储器极大地提高了计算机的性能和效率。

•它可以减少CPU对主存储器的访问次数,缩短了数据传输的时间。

•高速缓冲存储器被广泛应用于各种计算机硬件架构中,包括个人电脑、服务器和嵌入式系统等。

高速缓冲存储器cache程序的访问局部性程序的访问局部性定义在较短时间间隔内,程序产生的地址往往聚集在很小的一段地址空间内。

具体体现有两方面:时间局部性:被访问的某一存储单元,在一个较短的时间间隔内可能被再次访问;空间局部性:被访问的存储单元的邻近单元在一个较短的时间间隔内,可能也会被访问。

产生访问局部性的原因程序是由指令和数据组成的。

指令在主存中是按序存放的,存储单元是连续的,地址也是连续的,循环结构程序段或函数等子程序段再较短时间间隔内可能被重复执行,因此,指令的访问具有明显的局部化特性;数据在主存中的也是按序连续存放的,尤其是数组元素,常常被按序重复访问,因此,数据的访问也具有明显的局部化特性。

命中(Hit):若CPU访问单元所在的块在cache中,则称为命中。

命中的概率称为命中率(Hit Rate),是命中次数与访问总次数之比。

命中时,CPU在cache直接存取信息,所用的时间开销为cache的访问时间,称为命中时间(Hit Time)。

缺失(Miss):若CPU访问单元所在的块不在cache中,则称为不命中或缺失,缺失的概率称为缺失率(Miss Rate),是缺失次数与访问总次数之比。

缺失时,需要从主存读取一个主存块送cache,同时将所需信息送CPU,所用的时间开销为主存访问时间和cache访问时间之和。

通常将从主存读入一个主存块到cache的时间称为缺失损失(Miss Penalty)。

CPU在cache—主存层次的平均访问时间为。

由于程序访问的局部性特定,cache的命中率可以达到很高,接近于1,因此,即使Miss Penalty 远远大于Hit Time,但最终的平均访问时间仍可接近cache的访问时间。

cache工作流程程序执行中过程中,需要从主存取指令或读数据时,先检查cache是否命中,若命中,则直接从cache中读取信息送CPU进行运算,而不用访问主存储器;若缺失,则将访问地址内的数据送CPU进行运算,同时将当前访问的主存块复制到cache中。

高速缓冲存储器Cache简介○王军评估计算机的主要性能指标之一是运行速度。

计算机的程序是在C PU中执行的,而平时程序和数据则存放在存储器中。

存储器分为外部存储器(如软盘、硬盘、磁带等)和内部存储器。

外部存储器容量大,速度慢,内部存储器容量小,速度快。

内存的使用在一定程度上解决了高速C PU和慢速存储设备之间速度上的矛盾。

但C PU和内存之间仍然存在速度上不匹配的矛盾。

为充分利用C PU的运行速度。

在C PU和内存之间又引入了高速缓冲存储器(C ac he)。

一、Cache的基本概念高速缓冲存储器Ca che是位于C PU和主存储器之间容量小而速度快的存储器,通常由SR AM(静态R A M)组成。

随着微电子技术和计算机技术的发展,CPU的工作频率越来越高,DR AM(动态R A M)可以用最低的价格和最小的体积提供更大的存储器空间,但是DR AM的速度难以满足C PU 的要求,因而访问系统存储器时都要插入等待周期,这对高速C PU来说是一种极大的浪费。

采用C ache技术是一种现实的解决问题的方法。

S R AM可以提供最高的总线性能。

由S R AM组成的C ac he即是把主存储器看作是高速存储器而设置的小容量局部存储器,这种高速存储器是面向C PU工作的存储器,存储C PU常用的数据和代码,Ca che的有效性是利用了程序对存储器的访问在时间和空间上具有局部区域性的特性,即对大多数程序来说,在某个时间片内会集中重复地访问某一个特定的区域。

C ac he通常由相联存储器实现。

相联存储器的每一个存储块都具有额外的存储信息,称为标签(T a g)。

当访问相联存储器时,将地址和每一个标签同时进行比较,从而对标签FRA M E E t h er n et—I IFRA M E E t h er n et—SNA PN e t W ar e DO S Requ es t erFI R ST N E TW O RK D RI V E=FN ET W A R E PR O TO CO L=N D S BI N D此时假设使用N E2000网卡,中断号为5,端口地址为300。

高速缓冲存储器cache10计科一班1010311110 韩家君高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM,一般而言它不像系统主记忆体那样使用DRAM技术,而使用昂贵但较快速的SRAM技术,也有快取记忆体的名称。

它是位于CPU与内存之间的临时存储器,比主存储器体积小但速度快,用于保有从主存储器得到指令的副本——很可能在下一步为处理器所需——的专用缓冲器。

在Cache中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从Cache中调用,从而加快读取速度。

由此可见,在CPU中加入Cache是一种高效的解决方案,这样整个内存储器(Cache+内存)就变成了既有Cache的高速度,又有内存的大容量的存储系统了。

Cache对CPU的性能影响很大,主要是因为CPU的数据交换顺序和CPU与Ca che间的带宽引起的。

高速缓存的基本概念在计算机存储系统的层次结构中,介于中央处理器和主存储器之间的高速小容量存储器。

它和主存储器一起构成一级的存储器。

高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。

某些机器甚至有二级三级缓存,每级缓存比前一级缓存速度慢且容量大。

而这时,一开始的高速小容量存储器就被人称为一级缓存。

高速缓存的组成结构高速缓冲存储器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU的速度。

主要由大部分组成:Cache存储体:存放由主存调入的指令与数据块。

地址转换部件:建立目录表以实现主存地址到缓存地址的转换。

替换部件:在缓存满时按一定策略进行数据块替换,并修改地址转换部件。

高速缓存的作用介绍在计算机技术发展过程中,主存储器存取速度一直比中央处理器操作速度慢得多,使中央处理器的高速处理能力不能充分发挥,整个计算机系统的工作效率受到影响。