一种带三级预放大的高速高精度CMOS比较器

- 格式:pdf

- 大小:883.94 KB

- 文档页数:5

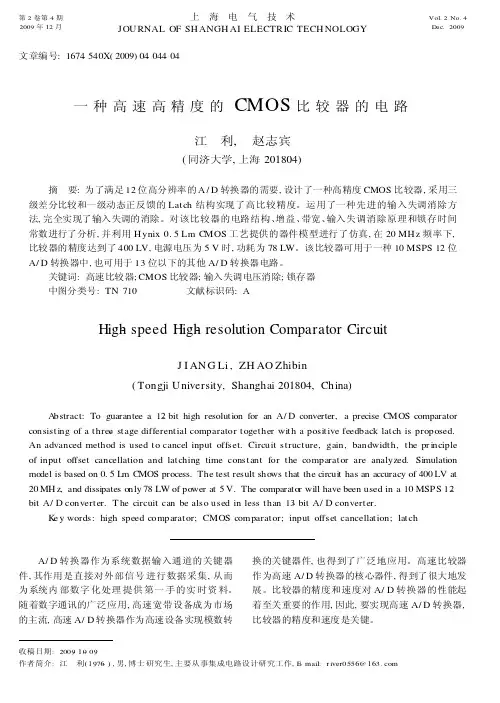

高速高精度比较器的设计冯奕翔;李哲英【期刊名称】《北京联合大学学报(自然科学版)》【年(卷),期】2011(025)003【摘要】With the analysis of preamplifier latch comparator,a high speed and high resolution comparator used for 12 bit and 1 MS/s SAR ADC was designed.The prototype was designed in 0.5 μm CMOS CSMC process.Based on the Hspice simulation tool,a new way to measure the offsets of preamplifier and latch was proposed.With improvements of existing offset calibration method,the offsets of preamplifier and latch are lower than before.The Cadence Spectre simulation results show that its speed can reach 20 MHz and the resolution is 0.8 mV.%根据预放大锁存快速比较理论,设计了一种应用于12 bit、1 MS/s逐次转换型模数转换器的比较器。

采用上华0.5μm CMOS工艺,基于Hspice仿真工具,提出了测量预放大器和锁存器的失调电压的新方法。

对已有失调校准技术进行改进,进一步降低了预放大器和锁存器的失调电压,显著提高了比较器的精度。

采用Cadence Spectre进行仿真,结果表明,在5 V单电源电压、20 MHz时钟频率时,分辨率可以达到0.8 mV,满足12 bit SAR ADC的精度要求。

28卷 第6期2011年6月微电子学与计算机MICROELECT RONICS &COM PUTE RV ol .28 N o .6June 2011收稿日期:2010-08-20;修回日期:2010-11-01基金项目:福建省自然科学基金重点项目(2007J0003);福建省自然科学基金(2009J05143);福建省新世纪优秀人才支持计划项目(XSJRC2007-26)应用于14bit SA R ADC 的高精度比较器的设计陈幼青,何明华(福州大学物理与信息工程学院,福建福州350000)摘 要:基于预防大锁存理论,设计了一款带有三级前置运算放大器和latch 再生电路的高精度比较器.为了实现高精度,采用了输入失调储存(IOS )和输出失调储存(O OS )级联的消失调方法,有效降低了比较器的输入失调电压.传统的比较器动态失调测试方法非常耗时,为此采用新的带负反馈网络的动态失调测试电路,从而大大提高了比较器的设计和仿真效率.Hhnec CZ 6H (0.35μm )工艺下,仿真表明,比较器能够分辨的最小信号为33.2μV ,满足14bit SA R AD C 对比较器的性能要求.关键词:SA R ;比较器;动态失调测试电路中图分类号:T N432 文献标识码:A 文章编号:1000-7180(2011)06-0109-04Design of High -esolution Comparator Applied in 14bit SAR ADCCHEN You -qing ,H E M ing -hua(College o f Phy sics and Info rmatio n Engineering ,Fuzhou Unive rsity ,F uzhou 350000,China )A bstract :Based on preamplifie r -la tch theo ry ,a high -re so lutio n co mpa rato r w ith three pre -amplifier s and a la tch is presented .In or der to achieve hig h -resolution ,bo th IO S and OO S offset cancella tion technique is used ,w hich suc -cessf ully decreases the input offset vo ltag e .T he traditio nal dy namic o ffset test me tho d is time co nsuming ,so a new dy namic o ffse t te st bench containing a negative feedback loop is adopted ,w hich efficiently speeds up the desig n and simulatio n .T he simulatio n r esults show that comparato r can distinguish 33.2μV under hhnec CZ6H (0.35μm )process .It is suitable fo r the 14bit SA R ADC .Key words :SA R ;comparato r ;dy namic o ffse t te st bench1 引言SA R 型ADC 具有中等速度、中等精度、低功耗、低成本等综合优势[1-2],在工业测控仪器、医疗成像设备、安防安检系统等中低速数据采集和信号处理系统中具有广泛的应用,此外,还可作为ADC IP 核广泛应用于SoC 中[3].比较器是SA R ADC 的关键模块,它在很大程度上直接影响了AD 转换器的各项性能参数,如速度、精度、功耗等.对于12bit 以上的SA R 型ADC ,除了要进行数字校准之外,对比较器的结构设计、输入失调电压处理提出了更大的挑战.14bit SAR ADC 要求比较器的分辨率达到16bit 以上.为了达到16bit 的比较精度,同时满足整个ADC 200kS /s 的速度要求,比较器采用了带三级前置运算放大器和latch 再生电路的比较器结构,同时采用输入失调储存和输出失调储存级联的消失调技术.2 比较器的电路结构和输入失调电压处理传统的比较器有运放结构的开环比较器和latch 锁存再生的闭环比较器.运放结构的比较器具有有精度较高、失调电压较小等优点[4],对小信号响应速度快,但对于大信号响应速度慢,输出电压与时微电子学与计算机2011年间成负指数关系.Latch 比较器对小信号响应慢,但由于使用了正反馈,对大信号响应速度比较快,输出电压与时间成正指数关系,但它的失调电压较大,容易受噪声干扰,对于14bit 的SA R 型ADC ,比较器单独使用运放结构的比较器或者latch 锁存比较器,都无法达到要求,因此需要将两种比较器结构级联,即预放大锁存比较器结构[5-6].预放大级对输入信号逐级放大,当信号被放大到Latch 再生电路能够有效识别的幅度时,Latch 电路再通过正反馈将信号迅速放大到数字电路能够有效识别的幅度.此外,比较器输入端与latch 再生电路通过前置运放进行隔离,有效降低了latch 再生电路回程噪声的影响[7].对于高精度A DC ,比较器通常要进行消失调处理.latch 级的失调电压一般在50~100mV ,运放的失调电压大约为5~20mV .latch 级的失调电压除以预防大的增益后,等效到比较器输入端的失调电压变得很小.因此,对于此种电路结构,主要是要消除运放的失调电压的影响.常用的失调电压消除方法有两种,一种是输入失调储存(IOS ),一种是输出失调储存(OOS )[6].IOS 是将失调电压储存在输入耦合电容上,OOS 是将失调电压储存在输出耦合电容上.Latch 级的失调电压通常比较大,常常要求前面预放大级的增益足够大,但是IOS 的速度相对比较慢,而OOS 中的预放大级增益不能太大,否则电容上的电压饱和后无法反映失调电压的真实大小.鉴于此,同时考虑速度问题,采用三级前置运放,这样可以将增益分配到各个运放,每个运放的增益都不需要太大[8],同时采用输入失调存储和输出失调存储级联的办法消除输入失调电压的影响,如图1所示.图1 比较器的结构图1中,op1、o p2、op3是三个前置运算放大器,增益大小分别设为A 1,A 2和A 3;C 1和C 2是失调校准电容.失调校准时,开关组S1断开,S2、S3、S4开关组闭合,此时比较器输入共模电平,op1的差分输入是V os1,差分输出是V o1;op2的差分输入是V os2和V o2,差分输出是V o2;o p3的差分输入是V os3和V o3,差分输出是V o3,那么,V o1=V os1(-A 1)(1)(V o2+V os2)(-A 2)=V o2(2)(V o3+V os3)(-A 3)=V o3(3)正常工作时,开关组S2、S3、S4断开,S1闭合,op1的差分输入是V os1和需要比较的信号V i ,差分输出为V o1′;op2的差分输入是V os2和V i2,差分输出是V o2′;o p3的差分输入是V os3和V i3,输出是V o3′;此时第一级到第三级的增益变为A 1′,A 2′,A 3′.那么,V o1′=(V os1+V i )(-A 1′)(4)V o2′=(V os2+V i2)(-A 2′)(5)V o3′=(V os3+V i3)(-A 3′)(6)由于正常工作的时候,op2和op3的输入是高阻节点,因此C 1和C 2上的电荷保持不变,因此有,V o1-V o2=V o1′-V i2(7)V o2-V o3=V o2′-V i3(8)由以上八个式子可求得ΔV os3=V i3+V os3-V i A 1′A 2′=(A 1′-A 1)A 2′V os1+A 2′-A 21+A 2V os2+11+A 3V os3(9)对于整个比较器系统,关注的是消失调处理后第三级运放输入端的残余输入失调电压,由上式可知,由于增益变化使得第一和第二级运放的输入失调电压未消除干净.考虑latch 级的失调电压和开关注入到电容上的失调电荷(设开关注入到C 1和C 2上的失调电荷分别为ΔQ 2、ΔQ 3),将残余输入失调电压等效到第一级运放的输入端,可得ΔV os ,eq =A 1′-A 1A 1′V os1+A 2′-A 2(1+A 2)A 1′A 2′V os2+1(1+A 3)A 1′A 2′V os3+V osL A 1′A 2′A 3′+ΔQ 2A 1′C 1+ΔQ 3A 1′A 2′C 2(10)由上式可知,暂不考虑增益变化的影响,消失调处理后,比较器残余的等效输入失调电压主要受第三级运放、la tch 的失调电压和开关注入到电容上的失调电荷的影响.对于第二级运放,既有输入失调存储,又有输出失调存储.级联处理后,第二级运放的输入失调电压被消除干净,而第三级运放和latch 级的失调电压除以增益A 1′A 2′A 3′,等效到输入端失调电压变得很小.考虑DAC 输入到比较器的最后一次比较信号110 第6期陈幼青,等:应用于14bit SA R ADC 的高精度比较器的设计的幅度,若与消失调处理时加的共模电平相差比较大,第二级运放由于增益变化造成的残余失调电压除以分母的增益,值很小,可以忽略不计.但是,第一级运放由于增益变化造成的残余失调电压对于高精度比较器来说,是最致命的影响因素,要求第一级运放运放的版图设计高度对称,并且使用大尺寸管子,减小失配,或者处理DAC 的输出信号幅度,减小增益变化的影响.3 比较器的电路设计SA R ADC 的参考电压为2.5V ,对比较器精度的要求为16bit ,那么,1/2LSB ≈38μV ,latch 级的失调电压大约为50~100m V ,设latch 失调电压100mV ,并考虑余量设计,要达到相应的比较精度,将前置运放的总增益设为80dB ,因为第一运放要对小信号进行快速响应,带宽设计比较大,但增益比较小,设为20dB ,后两级都为30dB ,并考虑latch 再生时产生的回程噪声,第二、三级采用casco de 结构,由于中间隔离了两个运放,回程噪声对第一级运放的影响很小,且考虑DAC 的输出信号幅度,第一级运放就不采用cascode 结构.运放都采用了带弱正反馈的电路结构,输出端增加了过驱动恢复开关,如图2所示,其中图(a )是第一级运放结构,图(b )是第二、三级运放结构.图2 前置运算放大器的电路结构图3是latch 再生电路和输出波形整形电路.La tch 再生电路是两个反相器首尾连接的电路结构,并通过时钟控制来实现采样和再生两个工作状态.Latch 采样时,开关S3和S4断开,S1和S2闭合,预防大级输出的信号输入到latch 再生电路的输入节点上,再生锁存时,S1和S2打开,S3和S4闭合,latch 电路迅速锁存再生,然后通过钟控SR锁存器和反相器进行输出波形整形.图3 latch 再生电路和钟控S R 锁存器4 比较器的输入失调电压仿真和结果分析比较器的工作过程可分为消失调处理和正常比较两个阶段,比较器的输入失调电压包括静态失调电压,如管子的阈值电压失配造成的DC 失调,以及动态失调电压,如开关电荷注入等,因此,无法像传统的运放结构比较器那样进行DC 扫描,从而得到输入失调电压.这种动态比较器的输入失调电压通常只能通过瞬态仿真,一次又一次的尝试,看比较器能够分辨的最小信号为多少,这种逐次逼近的测试方法,在多个corner 仿真和参数扫描时,工作量非常大,仿真效率很低.为了提高仿真效率,采用带负反馈网络的动态失调测试电路.图4是测试电路原理图.差分放大器将比较器的输出信号“0”和“1”信号转为“-1”和“1”信号,从而改变积分器的积分方向,即,积分器的输出信号的斜率的正负,积分器的输出信号加到比较器的负端,差分放大器和积分器构成了负反馈网络,通过负反馈使整个测试系统最终达到平衡状态.这样,只要仿真一次就可以获得比较器的输入失调电压.平衡时,积分器的输出信号必然穿越让比较器输出发生翻转的实际阈值电压,此时,积分器输出信号与比较器的正端输入信号的差值的平均值,就是比较器的等效输入失调电压.比较器的失调电压是由于电路元件的失配造成的,这种失配通常是随机的,在流片前,无法测出真正的失调电压,因此,动态失调电压测试前,可以先用M onte carlo 方法将运放的DC 失调电压范围测出来,然后系统失调仿真时,通过人为加等效的直流电压源模拟前置运放和latch 的失调电压.图5是比较器在M OS 工艺的co rner 为ss ,电容为tt mip ,直流电压源变化10%,即5.5V ,温度为-40℃情况下的的比较器输入失调电压仿真结果,该情况是多个corner 仿真、电源电压和温度参数扫描最坏的一111微电子学与计算机2011年种情况,由图示可知,该情况下比较器消失调处理后残余的等效输入失调电压为33.2μV ,满足精度要求.图4 钟控比较器动态失调测试电路图5 比较器输入失调电压仿真结果5 结束语通过采用三级前置运算放大器和latch 再生电路的比较器结构以及输入失调储存和输出失调储存级联的消失调技术,实现了高精度要求.带负反馈网络的动态失调电压测试电路有效提高了设计和仿真效率.仿真表明,比较器能够分辨的最小信号为33.2μV ,满足14bit SAR ADC 对比较器的精度要求,但是比较器的速度只有30M H z ,可以进一步优化设计,实现高速高精度,扩大比较器的应用范围.参考文献:[1]裴晓敏.8通道10b 的R -C 混合式SA R A DC 的设计[J ].现代电子技术,2008(9):83-85.[2]陈娟娟,钟德刚,徐静平.用于便携式设备的12位低功耗SA R A /D 转换器[J ].微电子学,2008,38(3):401.[3]Lo ng Sha nli ,W u Jianhui ,Xia Xiao juan ,et al .A 1.8-V 3.1mW succe ssiv e approx imation A DC in system -on -chip [J ].A nalog Integ ra ted Circuits a nd Sig nal P ro -cessing ,2008,56(3):205-2011.[4]冯楚华,陶建中,于宗光.一种用于数字功放的低功耗宽输入电压比较器[J ].微电子学与计算机,2008(11):109-112.[5]殷湛,郭立,杨吉庆.一种用于流水线A DC 的高速电压比较器[J ].微电子学与计算机,2006(2):182-184.[6]孙彤,李冬梅.一种0.2-mV 20-M H z 600-μW 比较器[J ].微电子学,2007,37(2):270-272.[7]李亮,臧佳锋,徐振,等.高速低功耗钟控比较器的设计[J ].半导体技术,2008,33(1):11-13.[8]林武平,郭良权,于宗光.新型高速低功耗动态比较器[J ].半导体技术,2008,33(12):1119-1120.作者简介:陈幼青 女,(1983-),硕士研究生.研究方向为模拟集成电路设计.何明华 男,(1971-),博士,教授.研究方向为嵌入式系统与系统级芯片设计.(上接第108页)[7]鲁云平,宋军,姚雪梅.基于免疫原理的网络入侵检测算法改进[J ].计算机科学,2008,35(9):116-119.[8]蔡涛,鞠时光,仲巍,等.面向存储安全系统的新型人工免疫算法[J ].计算机科学.2008,35(8):60-63.[9]陈云芳,王汝传.基于免疫算法的分类器设计[J ].计算机科学,2008,35(12):133-135.[10]陈君波,叶庆卫,周宇,等.一种新的混合变异粒子群算法[J ].计算机工程与应用,2007,43(7):59-60.作者简介:许小润 女,(1982-),硕士.研究方向为数字图像处理、模式识别.吴贵芳 男,(1978-),博士,副教授.研究方向为数字图像处理、模式识别.张庆华 男,(1964-),硕士,高级工程师.研究方向为机器视觉.112。

---------------------------------------------------------------范文最新推荐------------------------------------------------------ ADC中高速比较器的设计+文献综述摘要模数转换器(ADC)作为模拟电路和数字电路之间的转换电路,是众多电子类产品的重要模块。

随着视频、通讯等技术的迅速发展,高速、中分辨率ADC 的需求日益增长。

比较器作为ADC的关键模块,其速度、功耗等性能对整个转换电路的速度和功耗都有着至关重要的影响。

本论文基于预放大再生理论,采用SMIC 1.2V 0.065μm CMOS工艺,设计了一种适用于SAR ADC 的高速低功耗比较器电路,并进行了版图设计。

该比较器由前臵预放大级、锁存级和输出级构成。

前臵放大器的引入提高了比较器的速度,并降低了锁存器的失调电压。

同时采用均衡补偿技术,有效地抑制了回馈噪声。

电路的仿真均是在Cadence环境中进行。

仿真结果显示,在1.2V电源电压条件下,当时钟频率为1GHz1 / 22时,比较器功耗为0.3936mW,失调电压在-0.3mV到0.1mV之间。

比较器能够满足SAR ADC的性能要求。

8668关键词CMOS比较器预放大正反馈锁存器回馈噪声毕业设计说明书(论文)外文摘要TitleDesign of high speed low power comparator for ADCsAbstractAnalog-to-digital converters (ADCs) are important building blocks in many electronic products. The requirements for high-speed, medium-resolution ADC keep growing with the rapid development of video and communication technology. The speed and power consumption of the ADC is critically affected by the speed, power consumption and other properties of the comparator, which is a key module of the ADC.---------------------------------------------------------------范文最新推荐------------------------------------------------------The thesis is based on pre-amplification and regeneration theories. The high speed low power comparator is designed for SAR ADCs. And it's designed in the SMIC 0.065μm CMOS process with a supply voltage of 1.2V. The comparator is formed with a pre-amplifier stage, a latch stage and an output stage. The speed is improved and the offset voltage is reduced both by the pre-amplifier, and the kickback noise is inhibited by the neutralization technique.一般地,电子类产品的控制信号与处理信号是数字信号,而现实世界存在的以及电子产品间的通信信号为连续变化的模拟信号,这就需要将模拟信号转换为可以被处理的数字信号。

CMOS高性能运算放大器探究与设计引言:随着科技的不息进步和应用的广泛推广,运算放大器(Operational Amplifier,简称Op-Amp)作为一种重要的模拟电路器件,得到了广泛的关注和应用。

CMOS (Complementary Metal-Oxide-Semiconductor)技术由于其功耗低、集成度高等优势,被广泛应用于运算放大器的探究和设计中。

本文将介绍CMOS高性能运算放大器的探究与设计,主要包括运算放大器的基本原理、运算放大器的基本电路结构、CMOS技术的特点和优势、CMOS高性能运算放大器的设计方法和优化技术等方面。

一、运算放大器的基本原理运算放大器是一种特殊的差动放大器,它能够实现电压放大、电流放大、功率放大等功能。

运算放大器有两个输入端,一个非反相输入端和一个反相输入端;有一个输出端和一个电源端,电源端一般有正电源和负电源两个。

在抱负状况下,运算放大器具有无限的增益、无限的输入阻抗和零的输出阻抗。

但实际状况下,由于运算放大器的内部结构等因素的限制,无法完全满足抱负的条件。

因此,在运算放大器的设计中,需要思量如何提高增益、输入阻抗和输出阻抗等性能指标。

二、运算放大器的基本电路结构运算放大器的基本电路结构由差动放大器、电压放大器和输出级组成。

差动放大器用于实现输入信号的差分放大,电压放大器用于实现信号的放大,输出级用于驱动负载电阻。

差动放大器由两个晶体管组成,一个晶体管作为非反相输入端,另一个晶体管作为反相输入端。

通过调整两个晶体管的尺寸比例,可以实现不同的放大倍数。

电压放大器由级联的共源放大器组成,通过逐级放大,实现信号的放大。

输出级由差分放大器和输出级筛选电路组成,通过差分放大器将信号转化为可驱动负载电阻的电流信号,再经过输出级筛选电路,将电流信号转化为电压信号。

三、CMOS技术的特点和优势CMOS技术是一种基于金属-氧化物-半导体(MOS)结构的半导体制造技术。

与传统的bipolar技术相比,CMOS技术具有以下特点和优势:(1)功耗低:CMOS电路在静态状态下几乎不消耗电流,功耗分外低,适合于低功耗应用的场合。

《CMOS高性能运算放大器研究与设计》篇一一、引言随着微电子技术的快速发展,CMOS(互补金属氧化物半导体)技术已成为现代集成电路设计的主流技术。

运算放大器(Op-Amp)作为电子系统中的关键组件,其性能的优劣直接影响到整个系统的性能。

因此,对CMOS高性能运算放大器的研究与设计具有重要的实际应用价值。

本文将重点研究CMOS高性能运算放大器的设计原理、性能优化以及实际应用。

二、CMOS运算放大器的基本原理CMOS运算放大器是一种利用CMOS工艺制造的模拟电路器件,具有高精度、低噪声、低功耗等优点。

其基本原理是通过差分输入、差分输出以及电压增益等方式实现信号的放大和处理。

CMOS运算放大器的核心部分是差分对管和反馈网络,通过合理的电路设计和参数优化,可以实现高性能的运算放大器。

三、CMOS高性能运算放大器的设计1. 电路结构设计:CMOS高性能运算放大器的电路结构设计是关键。

在设计中,需要考虑差分对管的匹配性、反馈网络的稳定性以及噪声的抑制等因素。

常用的电路结构包括折叠式共源共栅结构、套筒式结构等。

这些结构在实现高电压增益的同时,还需要考虑功耗、噪声等性能指标的优化。

2. 参数优化:在CMOS高性能运算放大器的设计中,参数优化是必不可少的环节。

通过对差分对管的尺寸、偏置电流、反馈网络的电阻值等参数进行优化,可以提高运算放大器的性能。

此外,还需要考虑电路的匹配性、温度稳定性等因素,以确保运算放大器在不同条件下的性能稳定性。

3. 工艺选择:CMOS工艺的选择对运算放大器的性能有着重要影响。

在设计中,需要根据实际需求选择合适的工艺,如特征尺寸、阈值电压等。

同时,还需要考虑工艺的成熟度、生产成本等因素。

四、性能优化1. 增益与带宽:为了提高CMOS高性能运算放大器的性能,需要优化其增益和带宽。

通过合理的电路设计和参数优化,可以提高运算放大器的增益,同时保证足够的带宽以满足实际应用需求。

2. 噪声抑制:噪声是影响CMOS运算放大器性能的重要因素之一。

总结几种比较器的特点及应用一、引言比较器是电子电路中常用的一种器件,它可以将两个或多个信号进行比较,输出相应的信号。

在电路设计中,比较器被广泛应用于模拟信号处理、数字电路设计、传感器测量等领域。

本文将总结几种常见的比较器的特点及应用。

二、基本原理比较器是一种基本的模拟电路元件,其主要功能是将两个输入信号进行比较,并输出相应的高低电平。

比较器通常由一个差分放大器和一个输出级组成。

当输入信号差异足够大时,差分放大器输出高低电平不同的信号,经过输出级放大后输出到外部电路。

三、基本分类根据其工作原理和结构特点,比较器可以分为多种类型。

以下是几种常见的分类方式:1. 模拟比较器和数字比较器:模拟比较器主要用于模拟信号处理领域,数字比较器则主要用于数字电路设计和计算机系统中。

2. 开环比较器和闭环比较器:开环比较器只有一个输入端和一个输出端,闭环比较器则具有反馈回路。

3. 瞬态响应比较器和稳态响应比较器:瞬态响应比较器主要用于处理高速信号,稳态响应比较器则主要用于处理低速信号。

四、常见的比较器类型及其特点1. LM339型比较器LM339型是一种典型的四路开环比较器,具有广泛的应用领域。

它可以接受多种输入电压,输出电平为低电平。

其特点是功耗低、响应时间快、输出电流大等。

2. LM311型比较器LM311型是一种高速开环比较器,具有高精度和可靠性等特点。

它可以接受大范围的输入电压,并输出相应的高低电平。

3. LM393型比较器LM393型是一种典型的双路开环比较器,具有广泛的应用领域。

它可以接受多种输入电压,输出电平为低电平。

其特点是功耗低、响应时间快、输出电流大等。

4. TLC3702型比较器TLC3702型是一种高精度CMOS双路开环比较器,具有低功耗和高速度等特点。

它可以接受大范围的输入电压,并输出相应的高低电平。

五、应用领域比较器在电子电路中有着广泛的应用领域,以下是几个常见的应用场景:1. 传感器测量:比较器可以将传感器输出信号与参考电平进行比较,从而实现对物理量的测量和控制。

一种高速CMOS预放大锁存比较器

张奉江;张红;张正番

【期刊名称】《重庆邮电大学学报:自然科学版》

【年(卷),期】2007(019)B06

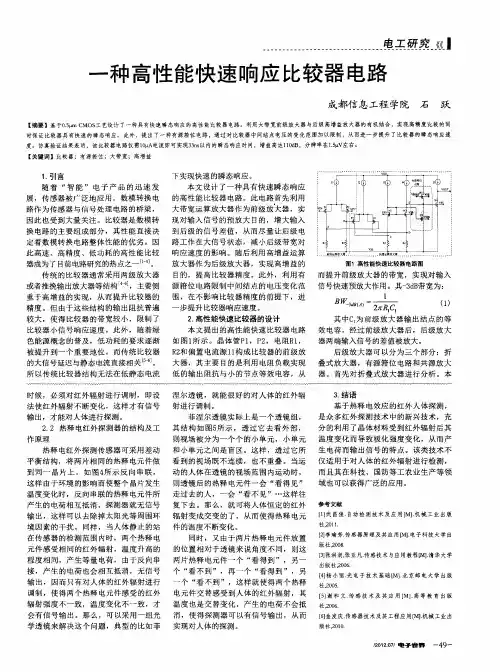

【摘要】介绍了一种适合于高速模数转换器(ADCs)的预放大一锁存(preamplifier-latch)CMOS比较器。

此电路结构包括一个预放大器、锁存比较器和输出缓冲器。

在预放大器和正反馈锁存比较器之间加入分离电路,以此来减少回扫(kickback)噪声对电路的影响。

采用0.35μm标准CMOS工艺库,在Cadence环境下进行仿真,该比较器在时钟频率为500MHz,采样频率为

40MHz的时候,可以达到30μV的精度,功耗大约为0.6mw。

【总页数】4页(P66-68,85)

【作者】张奉江;张红;张正番

【作者单位】重庆邮电大学,重庆400065;中国电子科技集团公司第二十四研究所模拟集成电路国家重点实验室,重庆400060

【正文语种】中文

【中图分类】TN432

【相关文献】

1.一种高速CMOS预放大锁存比较器 [J], 张奉江;张红;张正璠

2.高速CMOS锁存比较器的设计 [J], 赵海亮;刘诺;周长胜;马勋

3.高速低功耗CMOS动态锁存比较器的设计 [J], 李靖坤;杨骁;陈国晏;娄付军;邱伟

彬

4.高速CMOS预放大-锁存比较器设计 [J], 宁宁;于奇;王向展;任雪刚;李竞春;唐林;梅丁蕾;杨谟华

5.新型高速低功耗CMOS预放大锁存比较器 [J], 杨赟秀;罗静芳;宁宁;于奇;王向展;刘源;吴霜毅;杨谟华

因版权原因,仅展示原文概要,查看原文内容请购买。