5-1时序逻辑电路的分析

- 格式:ppt

- 大小:214.00 KB

- 文档页数:14

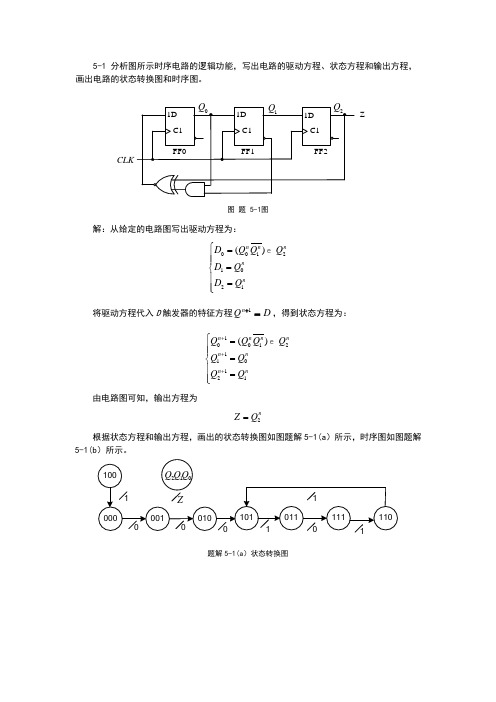

5-1 分析图所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n n nn D Q Q Q D Q D Q ⎧=⎪⎪=⎨⎪=⎪⎩e 将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n nn n Q Q Q Q Q Q Q Q +++⎧=⎪⎪=⎨⎪=⎪⎩e 由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ⎧=⎪⎨==+⎪⎩将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++⎧=⎪⎨==+⎪⎩电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图(a)所示,其输入波形如图 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

X(a) 电路图1234CLK5678X(b)输入波形 图 题 5-3图解:电路的驱动方程、状态方程和输出方程分别为:00101100011011011, ,n n n n n n n n n nJ X K X J XQ K XQ X Q XQ XQ XQ Q XQ XQ XQ Y XQ ++⎧==⎪⎨==⎪⎩⎧=+=⎪⎨⎪=+=+⎩= 根据状态方程和输出方程,可分别做出1110,n n Q Q ++和Y 的卡诺图,如表5-1所示。

5 . 1 异步时序逻辑电路模型(一)异步时序逻辑电路的分类异步时序电路可以从不同的角度进行分类。

1•冲异步时序电路和电平异步时序电路输入信号有脉冲信号和电平信号两种。

所谓电平信号是以电平的高低来表示信号;而脉冲信号是以脉冲的有无来表示信号。

根据输入信号的不同,异步时序电路又分脉脉冲时序电路和电平异步时序电路两种。

如果加到异步时序电路的输入为脉冲,则称为脉冲异步时序电路;反之,如果输入信号为电平.则称为电平异步时序电路。

2.米勒电路和莫尔电路根据输出与输入的不同关系,异步时序电路有米勒电路和莫尔电路两种类型。

假如电路的输出状态不仅与输入状态有关,还与二次状态有关,这样的异步时序电路称米勒电路;如果电路的输出状态仅与二次状态有关,而与输入状态无关,这样的异步时序电路称为莫尔电路。

(二)异步时序逻辑电路的一般结构异步时序电路由组合电路和存储电路两部分组成。

脉冲异步时序电路的存储电路常采用触发器,它可以是时钟控制触发器,也可以是基本R-S触发器。

在使用时钟控制触发器时,触发器不被统一的时钟脉冲同步,每个触发器的时钟端作为一个独立的输入端。

电平异步时序电路的存储电路采用延迟元件,它可以是外加的延迟元件,也可以利用反馈回路的附加延迟。

脉冲异步时序电路与同步时序电路的主要差别是电路的状态改变方式不同,前者在输入信号的控制下改变状态,而后者却在同一时钟脉冲控制下改变状态。

这一差别导致了脉冲异步时序电路和同步时序电路在分析和设计方法上都有若干差别。

一、5 . 2 脉冲异步时序逻辑电路脉冲异步时序电路状态的改变直接依赖于输入脉冲,即每来一个输入脉冲,电路状态发生一次变化。

由于触发器没有公共的时钟脉冲来同步,电路状态的转换将不可预测。

为了使脉冲异步时序电路可靠工作,对脉冲异步时序电路的输入信号应作如下规定:(1)不允许在两个(或两个以上)输入端同时加输入脉冲;(2)第二个输入脉冲的到来,必须在第一个输入脉冲所引起的整个电路的响应完全结束之后。

时序逻辑电路的分析方法时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后得出它的功能。

同步时序逻辑电路的分析方法同步时序逻辑电路的主要特点:在同步时序逻辑电路中,山于所有触发器都山同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可以不考虑时钟条件。

1、基本分析步骤1)写方程式:输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。

驱动方程:各触发器输入端的逻辑表达式。

状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。

2)列状态转换真值表:将电路现态的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。

如现态的起始值已给定时,则从给定值开始计算。

如没有给定时,则可设定一个现态起始值依次进行计算。

3)逻辑功能的说明:根据状态转换真值表来说明电路的逻辑功能。

4)画状态转换图和时序图:状态转换图:是指电路山现态转换到次态的示意图。

时序图:是在时钟脉冲CP作用下,各触发器状态变化的波形图。

5)检验电路能否自启动关于电路的自启动问题和检验方法,在下例中得到说明。

11222、 分析举例例、试分析下图所示电路的逻辑功能,并画出状态转换图和时序图。

解:山上图所示电路可看出,时钟脉冲CP 加在每个触发器的时钟脉冲输入 端上。

因此,它是一个同步时序逻辑电路,时钟方程可以不写。

①写方程式:输出方程:Y = Qo 31驱动方程:业=Q^Qa"' %= Qo"芒态方豎 _ ,Q 严1= %囲+%& =1Q?+1Q O -=Q^01小詁0? + %酉=Q 7Q 0-㊉Q「Q^i 二爲 Q?+兀 Q? = Qi'Qo'Q?^ 而 Qf②列状态转换真值表:状态转换真值表的作法是:从第一个现态“000”开始,代入状态方程,得次态为“001”,代入输出方程,得输出为"0” O把得出的次态"001"作为下一轮计算的“现态”,继续计算下一轮的次态值和输出值。

思考题与习题题解5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。

(2)构成一异步2n进制加法计数器需要n 个触发器,一般将每个触发器接成计数或T’型触发器。

计数脉冲输入端相连,高位触发器的CP端与邻低位Q端相连。

(3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4个时钟脉冲CP后可串行输出4位数码。

(4)要组成模15计数器,至少需要采用 4 个触发器。

5-2判断题(1)异步时序电路的各级触发器类型不同。

(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

(×)(3)具有N个独立的状态,计满N个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。

(√)(4)计数器的模是指构成计数器的触发器的个数。

(×)5-3单项选择题(1)下列电路中,不属于组合逻辑电路的是(D)。

A.编码器B.译码器C.数据选择器D.计数器(2)同步时序电路和异步时序电路比较,其差异在于后者( B)。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关(3)在下列逻辑电路中,不是组合逻辑电路的有( D)。

A.译码器B.编码器C.全加器D.寄存器(4)某移位寄存器的时钟脉冲频率为完成该操作需要(B)时间。

100KHz,欲将存放在该寄存器中的数左移8位,A.10μSB.80μSC.100μSD.800ms(5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要(C )个触发器。

A.6B.7C.8D.10(6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。

A.10B.15C.32D.32768(7)一位8421BCD 码计数器至少需要(B)个触发器。

5-1 分析图所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n nn n D Q Q Q D Q D Q ⎧=⎪⎪=⎨⎪=⎪⎩将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n n n n Q Q Q Q Q Q Q Q +++⎧=⎪⎪=⎨⎪=⎪⎩由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ⎧=⎪⎨==+⎪⎩将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++⎧=⎪⎨==+⎪⎩电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图(a)所示,其输入波形如图 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

X(a) 电路图1234CLK5678X(b)输入波形 图 题 5-3图解:电路的驱动方程、状态方程和输出方程分别为:00101100011011011, ,n n n n n n n n n nJ X K X J XQ K XQ X Q XQ XQ XQ Q XQ XQ XQ Y XQ ++⎧==⎪⎨==⎪⎩⎧=+=⎪⎨⎪=+=+⎩= 根据状态方程和输出方程,可分别做出1110,n n Q Q ++和Y 的卡诺图,如表5-1所示。