基于Encounter的自动布局布线

- 格式:ppt

- 大小:1.20 MB

- 文档页数:24

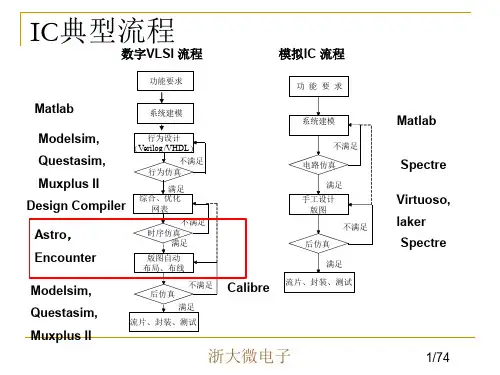

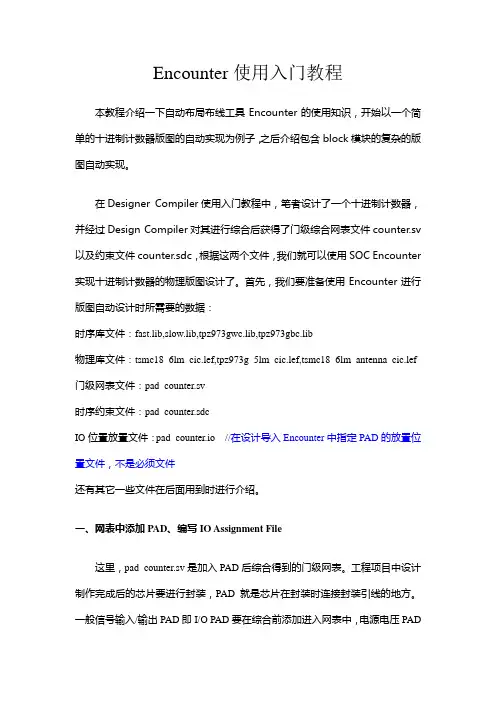

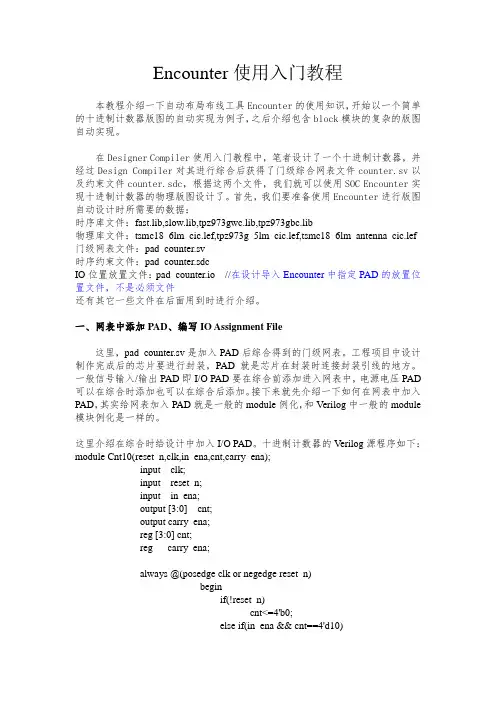

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv 以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter 实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD 可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

CADENCEPCB设计布局与布线CADENCEPCB设计工具是电子工程师在进行PCB电路板设计时经常使用的软件。

其强大的功能使得设计师可以进行布局和布线,确保电路板的性能和可靠性。

下面将详细介绍CADENCEPCB设计的布局和布线过程。

首先是布局过程。

布局是指在PCB上放置电子元器件和确定它们之间的物理布置。

布局的目标是优化电路板的性能、减小电磁干扰并提供良好的散热。

以下是CADENCEPCB设计中的布局步骤:1.确定布局约束:首先,设计师需要根据电路的要求和特定的应用环境,确定布局的约束条件,如电源分配、信号完整性、热管理等。

这些约束条件将指导接下来的布局和布线过程。

2.放置电子元器件:根据电路图和设计要求,将电子元器件在PCB上进行合理的放置。

重要的因素包括元器件之间的物理距离,信号和电源线的长度和走向,以及避免冲突和干扰的布局。

3.优化布局:在放置元器件之后,设计师需要优化布局,以确保信号完整性。

这包括优化电源和地平面的布置,减小信号线的长度和交叉,并提供良好的散热条件等。

4.电源和地平面设计:在布局过程中,需要合理设计电源和地平面,以提供足够的电源稳定性和地电流供应。

这需要将电源和地线走线得当,并采用合适的电容和电感等元件进行滤波和终端处理。

接下来是布线过程。

布线是指设计师将电子元器件之间的连线进行优化和优化,以确保信号的完整性、最小化电磁干扰并满足设计约束条件。

以下是CADENCEPCB设计中的布线步骤:1.设计路由规则:在进行布线之前,设计师需要制定一个路由规则,包括最小线宽和线间距、阻抗控制、信号类型和电源线与地线的关系等。

这些规则将指导后续的布线过程。

2.自动布线:CADENCEPCB设计工具提供了自动布线工具,可以根据预先设定的规则和优化目标,自动生成布线方案。

设计师可以根据需要进行调整和优化。

3.手动布线:对于一些复杂的板线、高速信号或特殊需求,手动布线是必要的。

对于这些情况,设计师需要手动布线,根据设计约束和优化目标,确定线路的走向和走线方式,并避免冲突和干扰。

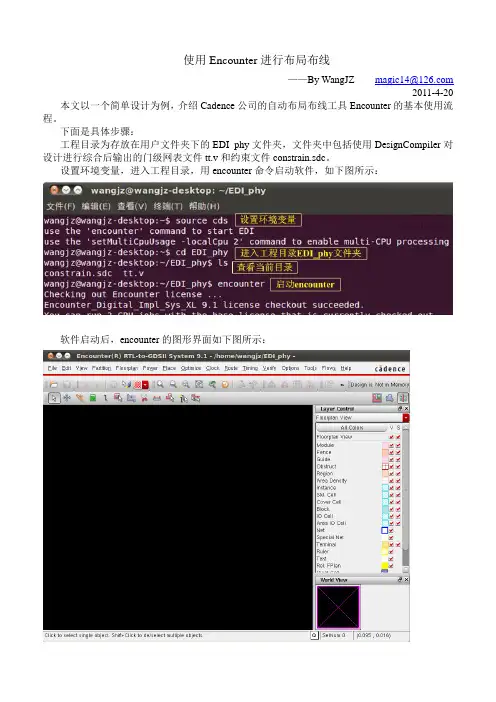

使用Encounter进行布局布线——By WangJZ magic14@2011-4-20 本文以一个简单设计为例,介绍Cadence公司的自动布局布线工具Encounter的基本使用流程。

下面是具体步骤:工程目录为存放在用户文件夹下的EDI_phy文件夹,文件夹中包括使用DesignCompiler对设计进行综合后输出的门级网表文件tt.v和约束文件constrain.sdc。

设置环境变量,进入工程目录,用encounter命令启动软件,如下图所示:软件启动后,encounter的图形界面如下图所示:导入设计文件,如下所示。

其他选项可暂时不填,保持默认设置,点击确认按钮。

成功导入设计文件后,Encounter视图如下所示:定义设计的尺寸、长宽比等信息,如下所示:完成后如下图所示,Core区和IO边缘有10um的距离。

添加全局连线,此处主要是电源和地的全局连线,分别把VDD的pin、net和高电平连接到全局连线VDD,把VSS的pin、net和低电平连接到全局连线VSS,如下所示:添加电源环,如下所示:填入电源环的宽度、距离、使用的金属层等信息,点击确认后,电源环添加到Core区和IO 边缘之间的空间,如下所示:添加core区中标准单元的电源连线,如下所示:添加电源连线后,视图如下所示:放置标准单元,然后切换到版图视图,可看到标准单元放置后的效果,如下所示:接着进行时钟树综合,可使用手动编写的时钟树配置文件或者用软件自动生配置文件进行时钟树综合。

此处采用软件自动生成配置文件的方式,如下所示:时钟树综合的同时会进行版图的初始布线。

完成时钟树综合后,进行版图的详细布线,如下所示:详细布线采用默认设置即可,完成详细布线后效果图如下:如果只是进行Encounter的学习,到此处即可保存并输出结果。

如果是要进行实际的流片生产,还需对各层进行填充,包括标准单元填充和各个金属层的填充,以保证满足生产所需的密度。

集成电路设计中的自动布局布线方法研究在集成电路的设计过程中,自动布局布线是必不可少的一步。

它的目标是将电路中的各个组件合理地布局在芯片的表面,并通过导线将它们连接起来,以实现电路的功能。

自动布局布线方法的研究可以提高电路的性能、减小面积、降低功耗,对于集成电路的设计具有重要的意义。

自动布局布线方法的研究主要包括两个方面,即自动布局和自动布线。

自动布局是指在给定的芯片面积内,将电路中的各个组件按照一定的规则自动布置在芯片上,使得它们之间的距离适当,并且不产生电路冲突。

自动布线是指根据布局结果,自动地在芯片的表面上生成导线网络,使得电路中的各个组件之间能够正确地互连。

在自动布局的研究中,通常采用的方法是通过建立电路的等效模型,将布局问题转化为数学优化问题。

具体来说,可以使用基于禁忌搜索、模拟退火等启发式算法来求解布局问题。

另外,还可以利用迁移学习、强化学习等机器学习方法,通过训练模型来优化布局结果。

在自动布线的研究中,常常使用的方法是通过建立网络流模型,将布线问题转化为最小费用流、最大流等经典问题。

然后,可以采用广度优先搜索、深度优先搜索等算法来求解布线问题。

此外,还可以使用并行计算、多目标优化等技术,提高布线的效率和质量。

自动布局布线方法的研究不仅需要考虑电路的性能,还需满足芯片的制造工艺要求。

因此,在布局布线的过程中,需要考虑到电路的延迟、功耗、面积等指标,并且要遵守芯片制造的规则。

例如,可以利用线性规划等数学方法来求解布局布线问题中的多目标优化问题,以平衡不同指标的要求。

自动布局布线方法的研究还要考虑到不同工艺、不同电路结构之间的差异性。

因此,对于不同类型的电路,需要采用不同的布局布线方法。

例如,对于数字电路,可以采用网格化布局方法,将电路中的组件和导线都放置在网格交叉点上。

而对于模拟电路,可以采用层次化布局方法,将电路中的组件和导线分别放置在不同的层次上。

总的来说,自动布局布线方法的研究对于集成电路的设计具有重要的意义。

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件以及约束文件,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:,,,物理库文件:,,门级网表文件:时序约束文件:IO位置放置文件:eset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),t(top_cnt),.carry _ena(top_carry_ena)); AD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));(PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为973g,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

基于umc18工艺的SOC Encounter数字版图设计流程V1.0 2014-02-28记录:张亮目录一、文件的准备 (3)1.1库文件的准备 (3)1.2根据设计准备所需文件 (3)二、运行软件 (3)三、版图设计流程 (4)3.1 Design_import (4)3.2 Global Net Connection (6)3.3 FloorPlan (7)3.4 Add Power Rings (8)3.5 Add Stripes (9)3.6 Placement Blockage (11)3.7 Placement (11)3.8 IO Filling (13)3.9 Special Route (SRoute) (13)3.10 Pre–CTS Optimization (15)3.11 Creat clock tree spec (16)3.12 Clock Tree Synthesis (18)3.13 Post–CTS Optimization (18)3.14 Trail Routing (20)3.15 Nano Routing (21)3.16 Add Filling (22)3.17 Post–Route Optimization (22)3.18 生成SDF 时序文件 (24)3.19 Verify connectivity (24)3.20 Verify Geometry (25)3.21 Export Files (26)四、DRC校验 (27)4.1库文件的准备 (27)4.2 根据设计准备所需文件 (28)4.3 修改库文件路径 (28)4.4 启动calibre (29)4.5 encourage 打开查看报告 (29)五、LVS校验 (31)5.1库文件的准备 (31)5.2 根据设计准备所需文件 (32)5.3 生成.spi文件 (32)5.4 启动LVS (32)5.5 查看报告 (32)一、文件的准备1.1库文件的准备对于SOC Encounter而言,后端设计所需的主要有由Foundry厂所提供的标准单元和I/O Pad的库文件,它包括物理库、时序库,分别以.lef、.tlf(或者.lib)的形式给出,其中I/O Pad 的相关库文件只有在做有Pad的版图时才需要。

使用Encounter进行布局布线——By WangJZ magic14@2011-4-20 本文以一个简单设计为例,介绍Cadence公司的自动布局布线工具Encounter的基本使用流程。

下面是具体步骤:工程目录为存放在用户文件夹下的EDI_phy文件夹,文件夹中包括使用DesignCompiler对设计进行综合后输出的门级网表文件tt.v和约束文件constrain.sdc。

设置环境变量,进入工程目录,用encounter命令启动软件,如下图所示:软件启动后,encounter的图形界面如下图所示:导入设计文件,如下所示。

其他选项可暂时不填,保持默认设置,点击确认按钮。

成功导入设计文件后,Encounter视图如下所示:定义设计的尺寸、长宽比等信息,如下所示:完成后如下图所示,Core区和IO边缘有10um的距离。

添加全局连线,此处主要是电源和地的全局连线,分别把VDD的pin、net和高电平连接到全局连线VDD,把VSS的pin、net和低电平连接到全局连线VSS,如下所示:添加电源环,如下所示:填入电源环的宽度、距离、使用的金属层等信息,点击确认后,电源环添加到Core区和IO 边缘之间的空间,如下所示:添加core区中标准单元的电源连线,如下所示:添加电源连线后,视图如下所示:放置标准单元,然后切换到版图视图,可看到标准单元放置后的效果,如下所示:接着进行时钟树综合,可使用手动编写的时钟树配置文件或者用软件自动生配置文件进行时钟树综合。

此处采用软件自动生成配置文件的方式,如下所示:时钟树综合的同时会进行版图的初始布线。

完成时钟树综合后,进行版图的详细布线,如下所示:详细布线采用默认设置即可,完成详细布线后效果图如下:如果只是进行Encounter的学习,到此处即可保存并输出结果。

如果是要进行实际的流片生产,还需对各层进行填充,包括标准单元填充和各个金属层的填充,以保证满足生产所需的密度。