摄像头寄存器

- 格式:docx

- 大小:1.05 MB

- 文档页数:23

红绿灯摄像头的工作原理是什么?大家都清楚:红绿灯上面或对面排列的摄像机是用于拍摄闯红灯的,你留意看一下停红灯时停车线旁边的地面都有个四方格,那里切开后在里面装了地感线圈,红灯时系统就会启动,如果车辆越过停车线,地感线圈感应到,监控录像就会自动另外保存车辆越线时的图片。

没有测速功能!但不代表说红绿灯路口没有排列式摄像机就没抓拍闯红灯,有些地方远处的球型摄像机也照样可以抓拍到违章。

所以请开车的朋友们在哪都要遵守交通法规。

监控拍摄:1、电子眼采用感应线来感应路面上的汽车传来的压力,通过传感器将信号采集到中央处理器,送寄存器暂存(该数据在一个红灯周期内有效);2、在同一个时间间隔内(红灯周期内),如果同时产生两个脉冲信号,即视为“有效”,简单的说,就是如果当时红灯,你的头轮子过线了,而后轮子没出线,则只产生了一个脉冲,在没有连续的两个脉冲时,不拍照;3、有些情况是:有的人开车前轮过线了,怕被拍到,于是他又倒一下车,回到线内,结果还是被照了,什么原因?就是因为一前一后的,产生了“一对”脉冲信号(这一对脉冲是在同一个红灯周期内产生的),我就是因为这样被排了n次,郁闷;4、黄灯亮时,拍照系统延时2s后启动;红灯亮时,系统已经启动;绿灯将要亮时,提前2s 关闭系统,主要是为了防止误拍。

所以很多出租车司机都知道,差不多就可以走了,一样没事就这个道理。

但是建议大家不这样做,因为时机比较难把握哟。

后期处理:当图像被下载传输指挥中心以后,就需要对图像进行登记、编号、公告,再传输到中心计算机数据库,以备各种机关调用。

系统特点:车辆捕获率-----100%(不包括二轮摩托车等)。

识别时间-----约1秒(肯定比你的反应要快的多) 。

车牌识别率-----白天95%以上,晚上90%以上(比较高啊)。

适用车速------5-180Km/h (如果你开190你就可以尽管逃之夭夭了,呵、、)1、违章电视抓拍的原理有两种方式,一种是地下埋设感应线圈,横杆上架设数码相机,用于对闯红灯的抓拍,另一种是架设摄像机,用于对超速、闯红灯、违章停车等进行实时录相。

camera硬件结构及原理**Camera基本结构及原理****备忘**:⽂末⽀持⼀波,感谢鞠躬⼀、学习⽬的本模块主要是了解⼀个摄像头模组的基本组成,每个组成部分的主要作⽤是什么,同时掌握⼀些基本术语。

⼆、必知必会1)画出⼀个摄像头的基本构成⽰意图2)说出每个模块的作⽤3)说出Camera成像原理4)总结Camera结构及原理相关的⼀些基本术语:SensorIC、Module、CCD、CMOS、像素、pixel size,光圈,焦距,VCM、BSI等。

三、Camera成像原理⼿机中的Camera是⼀个整体的模组,感光sensor(芯⽚)为核⼼器件,其他组成期间包括镜头、FPC、对焦马达、eeprom等。

其中sensor通过I2C控制,数据通过MIPI传输。

⽬前主要使⽤raw sensor,输出raw数据。

图3.1 camera结构共组原理摄像头模组:全程Camera CompactModule,常称Module基本⼯作原理:景物通过镜头⽣成光学图像投射到图像传感器表⾯上,然后转为电信号,经过A/D转换后变为数字图像信号,再将数字图像信号输出到⼿机的图像处理芯⽚中。

图3.2 Camera处理流程四、Camera组成器件图4.1 camera特写图图4.2 camera 组成图4.1、镜头(Lens)镜头是将拍摄景物在传感器上成像的器件,它通常由⼏⽚透镜组成。

从材质上看,摄像头的镜头可分为塑胶透镜和玻璃透镜。

图4.1.1 镜头镜头有两个较为重要的参数:光圈和焦距。

光圈是安装在镜头上控制通过镜头到达传感器的光线多少的装置,除了控制通光量,光圈还具有控制景深的功能,光圈越⼤,景深越⼩,平时在拍⼈像时背景朦胧效果就是⼩景深的⼀种体现。

景深是指在摄影机镜头前能够取得清晰图像的成像所测定的被摄物体前后距离范围。

图4.1.2光圈⼤⼩⽰意图数值越⼩,光圈越⼤,进光量越多,画⾯⽐较亮,焦平⾯越窄,主体背景虚化越⼤;值越⼤,光圈越⼩,进光量越少,画⾯⽐较暗,焦平⾯越宽,主体前后越清晰。

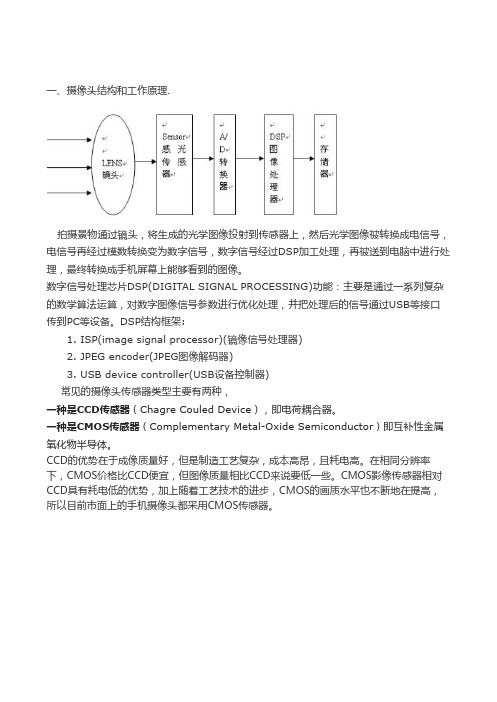

一、摄像头结构和工作原理.拍摄景物通过镜头,将生成的光学图像投射到传感器上,然后光学图像被转换成电信号,电信号再经过模数转换变为数字信号,数字信号经过DSP加工处理,再被送到电脑中进行处理,最终转换成手机屏幕上能够看到的图像。

数字信号处理芯片DSP(DIGITAL SIGNAL PROCESSING)功能:主要是通过一系列复杂的数学算法运算,对数字图像信号参数进行优化处理,并把处理后的信号通过USB等接口传到PC等设备。

DSP结构框架:1. ISP(image signal processor)(镜像信号处理器)2. JPEG encoder(JPEG图像解码器)3. USB device controller(USB设备控制器)常见的摄像头传感器类型主要有两种,一种是CCD传感器(Chagre Couled Device),即电荷耦合器。

一种是CMOS传感器(Complementary MetalOxide Semiconductor)即互补性金属氧化物半导体。

CCD的优势在于成像质量好,但是制造工艺复杂,成本高昂,且耗电高。

在相同分辨率下,CMOS价格比CCD便宜,但图像质量相比CCD来说要低一些。

CMOS影像传感器相对CCD具有耗电低的优势,加上随着工艺技术的进步,CMOS的画质水平也不断地在提高,所以目前市面上的手机摄像头都采用CMOS传感器。

手机摄像头的简单结构滤光片有两大功用: 1.滤除红外线。

滤除对可见光有干扰的红外光,使成像效果更清晰。

2.修整进来的光线。

感光芯片由感光体(CELL)构成,最好的光线是直射进来,但为了怕干扰到邻近感光体,就需要对光线加以修整,因此那片滤光片不是玻璃,而是石英片,利用石英的物理偏光特性,把进来的光线,保留直射部份,反射掉斜射部份,避免去影响旁边的感光点.二、相关参数和名词1、常见图像格式1.1 RGB格式:传统的红绿蓝格式,比如RGB565,RGB888,其16bit数据格式为5bit R + 6bit G + 5bit B。

宁波舜宇车载光学技术有限公司USB3.0数据采集系统FPGA+USB3.0韩斌2017/6/9USB3.0数据采集系统用户手册批准:审核:作成:日期一、USB协议概述关于USB的协议在《IFLabs USB3.0核心板开发手册V1.4》介绍的很详细,接下来主要介绍我在此间所学的一些总结和概括。

每个USB设备都可以包含一个或多个配置,不同的配置使设备表现出不同的功能组合,配置由多个接口组成。

在USB 协议中,接口代表一个基本的功能,一个功能复杂的USB设备可以具有多个接口, 而接口是端点的汇集。

端点的作用类似于寄存器。

每个端点在设备内部有唯一的端点号。

主机和设备通讯需要通过端点作为媒介。

端点的特点是单向性(即在某一时间只读或只写)。

设备的逻辑结构和组织结构见下图所示:PC机识别USB设备通过设备枚举来实现,而设备枚举首要步骤就是获取设备描述符。

在每一个USB设备内部,包含了固定格式的数据,通过这些数据,USB主机就可以获取USB 设备的类型、生产厂商等信息。

这些固定格式的数据,我们称之为USB设备描述符。

标准的USB设备有5种USB描述符:设备描述符、配置描述符、接口描述符、端点描述符合字符串描述符。

USB数据通讯模型的传输有四种传输方式,分为中断传输、批量传输、同步传输、控制传输。

如下就是控制传输的模型图:USB四个传输方式一般又分为三个事务:IN事务、OUT事务和SETUP事务,见下图所示:事务又分为令牌包(setup)、数据包(data)、握手包(ACK)、特殊包,如下图所示:一个包分为同步域(SYNC),标识域(PID),地址域(ADDR),端点域(ENDP),帧号域(FRAM),数据域(DATA)和校验域(CRC),见下图所示:USB正常工作之前,第一件事就是设备枚举,目的就是让主机认得这个USB设备,并且为这个设备配置资源,建立好主机与设备之间的数据传输通道。

设备枚举分为如下8个步骤:1,获取设备描述符2,复位3,设置地址4,再次获取设备描述符5,获取配置描述符6,获取端点、配置描述符7,获取字符串描述符8,选择设备配置二、CYUSB3014的SDK概述2.1介绍CYUSB3014的开发支持包由Cypress支持和提供,取名为FX3 SDK。

FPGA配置OV5640摄像头及RGB图像数据采集 本⽂设计思想采⽤明德扬⾄简设计法。

在做摄像头数据采集处理之前,需要配置OV5640传感器内部寄存器使其按要求正常⼯作,详细内容请参见《OV5640⾃动对焦照相模组应⽤指南》。

⾸先要关注OV5640的上电时序: 主控制器控制RESET PWDN两个信号按上电时序要求变化,之后允许ov_config模块配置内部寄存器。

这⾥始终将PWDN拉低。

实验中将摄像头分辨率设置为720p,即1280*720 ,帧率为30fps,图像输出格式是RGB565。

此时摄像头输⼊时钟XCLK频率24MHz,输出像素时钟PCLK为84MHz。

由于实验使⽤的是OV5640双⽬摄像头模组,且XCLK由外部24MHz晶振给出,故ov_config模块整体结构及端⼝定义如下: setup模块构造上电时序,两个reg_config分别配置⼀个OV5640摄像头。

SCCB_interface⼦模块负责SCCB协议读写寄存器数据。

由于OV5640摄像头内部寄存器地址为16位,因此写寄存器地址阶段分⾼低字节两次写⼊。

datasheet中给出了OV5640的SCCB ID地址(写),故读ID地址为0X79。

SCCB时序图及AC characteristics如下: SCCB时钟SIOC⽀持最⼤频率为400KHz,⼀般选100KHz即可。

以下是本⼈设计的SCCB接⼝读写时序状态机,写操作:IDLE START WRI_ID WRI_REG WRI_DATA STOP 对应三相写,读操作:IDLE START WRI_ID WRI_REG STOP START WRI_ID RD_DATA STOP对应两相写和两相读。

上代码:SCCB读写模块:1 `timescale 1ns / 1ps234module sccb_interface(5input clk,6input rst_n,78input wr_en,9input rd_en,10input [8-1:0] id_addr,11input [16-1:0] reg_addr,12input [8-1:0] wr_data,13output reg [8-1:0] rd_data,14output reg rd_vld,15output rdy,1617output reg sio_c,18output reg sio_out_en,19output reg sio_out,20input sio_in21 );2223parameter CYC = 500;242526localparam IDLE = 0 ;27localparam START = 1 ;28localparam WRI_ID = 2 ;29localparam WRI_REG = 3 ;30localparam WRI_DATA = 4;31localparam RD_DATA = 5;32localparam STOP = 6 ;3334//计数器35reg [ (9-1):0] div_cnt ;36wire add_div_cnt ;37wire end_div_cnt ;38reg [ (5-1):0] bit_cnt ;39wire add_bit_cnt ;40wire end_bit_cnt ;41reg [5-1:0] N;42 (*DONT_TOUCH = "TRUE"*)reg [7-1:0] state_c,state_n;43wire idle2start,start2wri_id,wri_id2wri_reg,wri_id2rd_data, wri_reg2wri_data,wri_reg2stop,wri_data2stop,rd_data2stop,stop2start,stop2idle; 44wire [18-1:0] regaddr;45reg [16-1:0] reg_addr_tmp;46reg [8-1:0] wr_data_tmp;47wire [9-1:0] idaddr_nc;48reg [8-1:0] id_addr_tmp;49reg rd_oper,rd_flag;50wire [9-1:0] wdata_nc;51wire [8-1:0] id_rwCtrl;525354assign rdy = state_c == IDLE && !wr_en && !rd_en;5556always @(posedge clk or negedge rst_n) begin57if (rst_n==0) begin58 div_cnt <= 0;59end60else if(add_div_cnt) begin61if(end_div_cnt)62 div_cnt <= 0;63else64 div_cnt <= div_cnt+1 ;65end66end67assign add_div_cnt = (state_c != IDLE);68assign end_div_cnt = add_div_cnt && div_cnt == (CYC)-1 ;//5000ns,200KHZ6970always @(posedge clk or negedge rst_n) begin71if (rst_n==0) begin72 bit_cnt <= 0;73end74else if(add_bit_cnt) begin75if(end_bit_cnt)76 bit_cnt <= 0;77else78 bit_cnt <= bit_cnt+1 ;79end80end81assign add_bit_cnt = (end_div_cnt);82assign end_bit_cnt = add_bit_cnt && bit_cnt == (N)-1 ;8384always@(*)begin85case(state_c)86 START: N = 1;87 WRI_REG: N = 18; //(8+1)*2 = 1888 WRI_ID,WRI_DATA,RD_DATA:N = 9;//8+189 STOP: N = 2;90default:;91endcase92end9394//FSM:IDLE START WRI_ID WRI_REG STOP95always @(posedge clk or negedge rst_n) begin96if (rst_n==0) begin97 state_c <= IDLE ;98end99else begin100 state_c <= state_n;101end102end103//write:IDLE START WRI_ID WRI_REG WRI_DATA STOP IDLE...104//read: IDLE START WRI_ID WRI_REG STOP START WRI_ID RD_DATA STOP IDLE (105)106always @(*) begin107case(state_c)108 IDLE :begin//0109if(idle2start)110 state_n = START ;111else112 state_n = state_c ;113end114 START :begin//1115if(start2wri_id)116 state_n = WRI_ID ;117else118 state_n = state_c ;119end120 WRI_ID :begin//2121if(wri_id2wri_reg)122 state_n = WRI_REG ;123else if(wri_id2rd_data)124 state_n = RD_DATA;125else126 state_n = state_c ;127end128 WRI_REG :begin//3129if(wri_reg2wri_data)130 state_n = WRI_DATA;131else if(wri_reg2stop)132 state_n = STOP ;133else134 state_n = state_c ;135end136 WRI_DATA:begin//4137if(wri_data2stop)138 state_n = STOP;139else140 state_n = state_c;141end142 RD_DATA:begin//5143if(rd_data2stop)144 state_n = STOP;145else146 state_n = state_c;147end148 STOP :begin//6149if(stop2start)150 state_n = START;151else if(stop2idle)152 state_n = IDLE ;153else154 state_n = state_c ;155end156default : state_n = IDLE ;157endcase158end159160assign idle2start = state_c==IDLE && (wr_en || rd_en);161assign start2wri_id = state_c==START && (end_bit_cnt);162assign wri_id2wri_reg = state_c==WRI_ID && (end_bit_cnt && !rd_oper);163assign wri_id2rd_data = state_c==WRI_ID && (end_bit_cnt && rd_oper);164assign wri_reg2wri_data = state_c==WRI_REG && (end_bit_cnt && !rd_flag);165assign wri_reg2stop = state_c==WRI_REG && (end_bit_cnt && rd_flag);166assign wri_data2stop = state_c==WRI_DATA && (end_bit_cnt);167assign rd_data2stop = state_c==RD_DATA && (end_bit_cnt);168assign stop2start = state_c==STOP && (end_bit_cnt && rd_flag && !rd_oper); 169assign stop2idle = state_c==STOP && (end_bit_cnt && (!rd_flag || rd_oper)); 170171always @(posedge clk or negedge rst_n)begin172if(rst_n==1'b0)begin173 rd_oper <= 0;174end175else if(stop2start)begin176 rd_oper <= 1;177end178else if(rd_oper && stop2idle)179 rd_oper <= 0;180end181182always @(posedge clk or negedge rst_n)begin183if(rst_n==1'b0)begin184 rd_flag <= 0;185end186else if(idle2start && rd_en)begin187 rd_flag <= 1;188end189else if(stop2idle)190 rd_flag <= 0;191end192193//SCCB时钟194always @(posedge clk or negedge rst_n)begin195if(rst_n==1'b0)196 sio_c <= 1'b1;197else if(add_div_cnt && div_cnt == CYC/4-1)198 sio_c <= 1;199else if(add_div_cnt && div_cnt == CYC/4+CYC/2-1)200 sio_c <= 0;201else if(state_c == IDLE)202 sio_c <= 1;//空闲状态sioc为1203end204205always @(posedge clk or negedge rst_n)begin206if(rst_n==1'b0)begin207 sio_out <= 1;208end209else if(state_c == START && div_cnt == CYC/2-1)210 sio_out <= 0;//开始条件211else if(state_c == WRI_ID)212 sio_out <= idaddr_nc[9-1-bit_cnt];213else if(wri_reg2stop || wri_data2stop || rd_data2stop)214 sio_out <= 0;215else if(state_c == WRI_REG)216 sio_out <= regaddr[18-1-bit_cnt];217else if(state_c == WRI_DATA)218 sio_out <= wdata_nc[9-1-bit_cnt];219else if(state_c == RD_DATA && bit_cnt == 9-1)220 sio_out <= 1;//NACK221else if(state_c == STOP && div_cnt == CYC/2-1 && bit_cnt == 0)222 sio_out <= 1;//结束条件223end224225assign idaddr_nc = {id_rwCtrl,1'b1};226assign regaddr = {reg_addr_tmp[15:8],1'b1,reg_addr_tmp[7:0],1'b1};227assign wdata_nc = {wr_data_tmp,1'b1};228229assign id_rwCtrl = rd_oper ? {id_addr[7:1],1'b1} : id_addr;230231always @(posedge clk or negedge rst_n)begin232if(rst_n==1'b0)begin233 reg_addr_tmp <= 0;234 wr_data_tmp <= 0;235end236else if(wr_en || rd_en)begin237 reg_addr_tmp <= reg_addr;238 wr_data_tmp <= wr_data;239end240end241242243always @(posedge clk or negedge rst_n)begin244if(rst_n==1'b0)begin245 sio_out_en <= 0;246end247else begin248case(state_c)249 START,STOP:begin250 sio_out_en <= 1;251end252 WRI_ID,WRI_DATA:begin253if(bit_cnt != 9-1)254 sio_out_en <= 1;255else256 sio_out_en <= 0;257end258 WRI_REG:begin259if(bit_cnt != 9-1 && bit_cnt != 18-1)260 sio_out_en <= 1;261else262 sio_out_en <= 0;263end264 RD_DATA:begin265if(bit_cnt == 9-1)266 sio_out_en <= 1;267else268 sio_out_en <= 0;269end270default:sio_out_en <= 0;271endcase272end273end274275//read data276always @(posedge clk or negedge rst_n)begin277if(rst_n==1'b0)begin278 rd_data <= 0;279end280else if(state_c == RD_DATA && bit_cnt != 9-1 && div_cnt == CYC/2-1)begin 281 rd_data[8-1-bit_cnt] <= sio_in;282end283end284285always @(posedge clk or negedge rst_n)begin286if(rst_n==1'b0)begin287 rd_vld <= 0;288end289else if(rd_data2stop)begin290 rd_vld <= 1;291end292else293 rd_vld <= 0;294end295296297endmodulesccb_interface寄存器配置模块:1 `timescale 1ns / 1ps234module reg_config(5input clk,6input rst_n,78input en,9output finish,1011inout sio_d,12output sio_c13 );1415localparam WR_ID = 8'h78;16localparam RW_CTRL = 2'b11;//读17wire sio_out_en;18wire sio_out;19wire sio_in;20reg [9-1:0] reg_cnt;21wire add_reg_cnt,end_reg_cnt;22reg config_flag;23reg [26-1:0] op_reg_data;24wire rdy;25reg wr_en;26reg [16-1:0] reg_addr;27reg [8-1:0] wr_data;28reg config_done;29reg [ (2-1):0] rw_cnt ;30wire add_rw_cnt ;31wire end_rw_cnt ;32reg rd_en;33 (*DONT_TOUCH = "TRUE"*)wire [8-1:0] rd_data;34 (*DONT_TOUCH = "TRUE"*)wire rd_vld;3536 sccb_interface sccb_interface(37 .clk (clk) ,38 .rst_n (rst_n) ,39 .wr_en (wr_en) ,40 .rd_en (rd_en),41 .id_addr (WR_ID) ,42 .reg_addr (reg_addr) ,43 .wr_data (wr_data) ,44 .rd_data (rd_data),45 .rd_vld (rd_vld),46 .rdy (rdy) ,47 .sio_c (sio_c) ,48 .sio_out_en(sio_out_en) ,49 .sio_out (sio_out) ,50 .sio_in (sio_in)51 );5253assign sio_d = sio_out_en ? sio_out : 1'bz;54assign sio_in = sio_d;5556always @(posedge clk or negedge rst_n) begin57if (rst_n==0) begin58 rw_cnt <= 0;59end60else if(add_rw_cnt) begin61if(end_rw_cnt)62 rw_cnt <= 0;63else64 rw_cnt <= rw_cnt+1 ;65end66end67assign add_rw_cnt = (config_flag && rdy);68assign end_rw_cnt = add_rw_cnt && rw_cnt == (2)-1 ;//0 write 1 read 6970always @(posedge clk or negedge rst_n)begin71if(!rst_n)begin72 reg_cnt <= 0;73end74else if(add_reg_cnt)begin75if(end_reg_cnt)76 reg_cnt <= 0;77else78 reg_cnt <= reg_cnt + 1;79end80end8182assign add_reg_cnt = end_rw_cnt;83assign end_reg_cnt = add_reg_cnt && reg_cnt == 261-1;8485//配置指令86always @(posedge clk or negedge rst_n)begin87if(rst_n==1'b0)begin88 wr_en <= 0;89 reg_addr <= 0;90 wr_data <= 0;91end92else if(add_rw_cnt && rw_cnt == 0)begin93 wr_en <= op_reg_data[25];94 reg_addr <= op_reg_data[23:8];95 wr_data <= op_reg_data[7:0];96end97else if(end_rw_cnt)begin98 rd_en <= op_reg_data[24];99 reg_addr <= op_reg_data[23:8];100end101else begin102 wr_en <= 0;103 rd_en <= 0;104end105end106107108always @(posedge clk or negedge rst_n)begin109if(rst_n==1'b0)begin110 config_flag <= 0;111end112else if(en && !config_flag && !config_done)begin113 config_flag <= 1;114end115else if(end_reg_cnt)116 config_flag <= 0;117end118119always @(posedge clk or negedge rst_n)begin120if(rst_n==1'b0)begin121 config_done <= 0;122end123else if(end_reg_cnt)begin124 config_done <= 1;125end126end127128assign finish = config_done && rdy;129130always@(*)131begin//op_reg_data [25] wr [24] rd [23:8] reg_addr [7:0] wr_data132case(reg_cnt)133//15fps VGA YUV output // 24MHz input clock, 24MHz PCLK1340:op_reg_data= {RW_CTRL, 24'h310311};// system clock from pad, bit[1]1351:op_reg_data= {RW_CTRL, 24'h300882};// software reset, bit[7]// delay 5ms1362:op_reg_data= {RW_CTRL, 24'h300842};// software power down, bit[6]1373:op_reg_data= {RW_CTRL, 24'h310303};// system clock from PLL, bit[1]1384:op_reg_data= {RW_CTRL, 24'h3017ff};// FREX, Vsync, HREF, PCLK, D[9:6] output enable1395:op_reg_data= {RW_CTRL, 24'h3018ff};// D[5:0], GPIO[1:0] output enable1406:op_reg_data= {RW_CTRL, 24'h30341A};// MIPI 10-bit1417:op_reg_data= {RW_CTRL, 24'h303713};// PLL root divider, bit[4], PLL pre-divider, bit[3:0]1428:op_reg_data= {RW_CTRL, 24'h310801};// PCLK root divider, bit[5:4], SCLK2x root divider, bit[3:2] // SCLK root divider, bit[1:0] 1439:op_reg_data= {RW_CTRL, 24'h363036};14410:op_reg_data= {RW_CTRL, 24'h36310e};14511:op_reg_data= {RW_CTRL, 24'h3632e2};14612:op_reg_data= {RW_CTRL, 24'h363312};14713:op_reg_data= {RW_CTRL, 24'h3621e0};14814:op_reg_data= {RW_CTRL, 24'h3704a0};14915:op_reg_data= {RW_CTRL, 24'h37035a};15016:op_reg_data= {RW_CTRL, 24'h371578};15117:op_reg_data= {RW_CTRL, 24'h371701};15218:op_reg_data= {RW_CTRL, 24'h370b60};15319:op_reg_data= {RW_CTRL, 24'h37051a};15420:op_reg_data= {RW_CTRL, 24'h390502};15521:op_reg_data= {RW_CTRL, 24'h390610};15622:op_reg_data= {RW_CTRL, 24'h39010a};15723:op_reg_data= {RW_CTRL, 24'h373112};15824:op_reg_data= {RW_CTRL, 24'h360008};// VCM control15925:op_reg_data= {RW_CTRL, 24'h360133};// VCM control16026:op_reg_data= {RW_CTRL, 24'h302d60};// system control16127:op_reg_data= {RW_CTRL, 24'h362052};16228:op_reg_data= {RW_CTRL, 24'h371b20};16329:op_reg_data= {RW_CTRL, 24'h471c50};16430:op_reg_data= {RW_CTRL, 24'h3a1343};// pre-gain = 1.047x16531:op_reg_data= {RW_CTRL, 24'h3a1800};// gain ceiling16632:op_reg_data= {RW_CTRL, 24'h3a19f8};// gain ceiling = 15.5x16733:op_reg_data= {RW_CTRL, 24'h363513};16834:op_reg_data= {RW_CTRL, 24'h363603};16935:op_reg_data= {RW_CTRL, 24'h363440};17036:op_reg_data= {RW_CTRL, 24'h362201}; // 50/60Hz detection 50/60Hz 灯光条纹过滤17137:op_reg_data= {RW_CTRL, 24'h3c0134};// Band auto, bit[7]17238:op_reg_data= {RW_CTRL, 24'h3c0428};// threshold low sum17339:op_reg_data= {RW_CTRL, 24'h3c0598};// threshold high sum17440:op_reg_data= {RW_CTRL, 24'h3c0600};// light meter 1 threshold[15:8]17541:op_reg_data= {RW_CTRL, 24'h3c0708};// light meter 1 threshold[7:0]17642:op_reg_data= {RW_CTRL, 24'h3c0800};// light meter 2 threshold[15:8]17743:op_reg_data= {RW_CTRL, 24'h3c091c};// light meter 2 threshold[7:0]17844:op_reg_data= {RW_CTRL, 24'h3c0a9c};// sample number[15:8]17945:op_reg_data= {RW_CTRL, 24'h3c0b40};// sample number[7:0]18046:op_reg_data= {RW_CTRL, 24'h381000};// Timing Hoffset[11:8]18147:op_reg_data= {RW_CTRL, 24'h381110};// Timing Hoffset[7:0]18248:op_reg_data= {RW_CTRL, 24'h381200};// Timing Voffset[10:8]18349:op_reg_data= {RW_CTRL, 24'h370864};18450:op_reg_data= {RW_CTRL, 24'h400102};// BLC start from line 218551:op_reg_data= {RW_CTRL, 24'h40051a};// BLC always update18652:op_reg_data= {RW_CTRL, 24'h300000};// enable blocks18753:op_reg_data= {RW_CTRL, 24'h3004ff};// enable clocks18854:op_reg_data= {RW_CTRL, 24'h300e58};// MIPI power down, DVP enable18955:op_reg_data= {RW_CTRL, 24'h302e00};19056:op_reg_data= {RW_CTRL, 24'h430060};// RGB56519157:op_reg_data= {RW_CTRL, 24'h501f01};// ISP RGB19258:op_reg_data= {RW_CTRL, 24'h440e00};19359:op_reg_data= {RW_CTRL, 24'h5000a7}; // Lenc on, raw gamma on, BPC on, WPC on, CIP on // AEC target ⾃动曝光控制19460:op_reg_data= {RW_CTRL, 24'h3a0f30};// stable range in high19561:op_reg_data= {RW_CTRL, 24'h3a1028};// stable range in low19662:op_reg_data= {RW_CTRL, 24'h3a1b30};// stable range out high19763:op_reg_data= {RW_CTRL, 24'h3a1e26};// stable range out low19864:op_reg_data= {RW_CTRL, 24'h3a1160};// fast zone high19965:op_reg_data= {RW_CTRL, 24'h3a1f14};// fast zone low// Lens correction for ? 镜头补偿20066:op_reg_data= {RW_CTRL, 24'h580023};20167:op_reg_data= {RW_CTRL, 24'h580114};20268:op_reg_data= {RW_CTRL, 24'h58020f};20369:op_reg_data= {RW_CTRL, 24'h58030f};20470:op_reg_data= {RW_CTRL, 24'h580412};20571:op_reg_data= {RW_CTRL, 24'h580526};20672:op_reg_data= {RW_CTRL, 24'h58060c};20773:op_reg_data= {RW_CTRL, 24'h580708};20874:op_reg_data= {RW_CTRL, 24'h580805};20975:op_reg_data= {RW_CTRL, 24'h580905};21076:op_reg_data= {RW_CTRL, 24'h580a08};21177:op_reg_data= {RW_CTRL, 24'h580b0d};21278:op_reg_data= {RW_CTRL, 24'h580c08};21379:op_reg_data= {RW_CTRL, 24'h580d03};21480:op_reg_data= {RW_CTRL, 24'h580e00};21581:op_reg_data= {RW_CTRL, 24'h580f00};21682:op_reg_data= {RW_CTRL, 24'h581003};21783:op_reg_data= {RW_CTRL, 24'h581109};21884:op_reg_data= {RW_CTRL, 24'h581207};21985:op_reg_data= {RW_CTRL, 24'h581303};22086:op_reg_data= {RW_CTRL, 24'h581400};22187:op_reg_data= {RW_CTRL, 24'h581501};22288:op_reg_data= {RW_CTRL, 24'h581603};22389:op_reg_data= {RW_CTRL, 24'h581708};22490:op_reg_data= {RW_CTRL, 24'h58180d};22591:op_reg_data= {RW_CTRL, 24'h581908};22692:op_reg_data= {RW_CTRL, 24'h581a05};22793:op_reg_data= {RW_CTRL, 24'h581b06};22894:op_reg_data= {RW_CTRL, 24'h581c08};22995:op_reg_data= {RW_CTRL, 24'h581d0e};23096:op_reg_data= {RW_CTRL, 24'h581e29};23197:op_reg_data= {RW_CTRL, 24'h581f17};23298:op_reg_data= {RW_CTRL, 24'h582011};23399:op_reg_data= {RW_CTRL, 24'h582111};234100:op_reg_data= {RW_CTRL, 24'h582215};235101:op_reg_data= {RW_CTRL, 24'h582328};236102:op_reg_data= {RW_CTRL, 24'h582446};237103:op_reg_data= {RW_CTRL, 24'h582526};238104:op_reg_data= {RW_CTRL, 24'h582608};239105:op_reg_data= {RW_CTRL, 24'h582726};240106:op_reg_data= {RW_CTRL, 24'h582864};241107:op_reg_data= {RW_CTRL, 24'h582926};242108:op_reg_data= {RW_CTRL, 24'h582a24};243109:op_reg_data= {RW_CTRL, 24'h582b22};244110:op_reg_data= {RW_CTRL, 24'h582c24};245111:op_reg_data= {RW_CTRL, 24'h582d24};246112:op_reg_data= {RW_CTRL, 24'h582e06};247113:op_reg_data= {RW_CTRL, 24'h582f22};248114:op_reg_data= {RW_CTRL, 24'h583040};249115:op_reg_data= {RW_CTRL, 24'h583142};250116:op_reg_data= {RW_CTRL, 24'h583224};251117:op_reg_data= {RW_CTRL, 24'h583326};252118:op_reg_data= {RW_CTRL, 24'h583424};253119:op_reg_data= {RW_CTRL, 24'h583522};254120:op_reg_data= {RW_CTRL, 24'h583622};255121:op_reg_data= {RW_CTRL, 24'h583726};256122:op_reg_data= {RW_CTRL, 24'h583844};257123:op_reg_data= {RW_CTRL, 24'h583924};258124:op_reg_data= {RW_CTRL, 24'h583a26};259125:op_reg_data= {RW_CTRL, 24'h583b28};260126:op_reg_data= {RW_CTRL, 24'h583c42};261127:op_reg_data= {RW_CTRL, 24'h583dce};// lenc BR offset // AWB ⾃动⽩平衡262128:op_reg_data= {RW_CTRL, 24'h5180ff};// AWB B block263129:op_reg_data= {RW_CTRL, 24'h5181f2};// AWB control264130:op_reg_data= {RW_CTRL, 24'h518200};// [7:4] max local counter, [3:0] max fast counter 265131:op_reg_data= {RW_CTRL, 24'h518314};// AWB advanced266132:op_reg_data= {RW_CTRL, 24'h518425};267133:op_reg_data= {RW_CTRL, 24'h518524};268134:op_reg_data= {RW_CTRL, 24'h518609};269135:op_reg_data= {RW_CTRL, 24'h518709};270136:op_reg_data= {RW_CTRL, 24'h518809};271137:op_reg_data= {RW_CTRL, 24'h518975};272138:op_reg_data= {RW_CTRL, 24'h518a54};273139:op_reg_data= {RW_CTRL, 24'h518be0};274140:op_reg_data= {RW_CTRL, 24'h518cb2};275141:op_reg_data= {RW_CTRL, 24'h518d42};276142:op_reg_data= {RW_CTRL, 24'h518e3d};277143:op_reg_data= {RW_CTRL, 24'h518f56};278144:op_reg_data= {RW_CTRL, 24'h519046};279145:op_reg_data= {RW_CTRL, 24'h5191f8};// AWB top limit280146:op_reg_data= {RW_CTRL, 24'h519204};// AWB bottom limit281147:op_reg_data= {RW_CTRL, 24'h519370};// red limit282148:op_reg_data= {RW_CTRL, 24'h5194f0};// green limit283149:op_reg_data= {RW_CTRL, 24'h5195f0};// blue limit284150:op_reg_data= {RW_CTRL, 24'h519603};// AWB control285151:op_reg_data= {RW_CTRL, 24'h519701};// local limit286152:op_reg_data= {RW_CTRL, 24'h519804};287153:op_reg_data= {RW_CTRL, 24'h519912};288154:op_reg_data= {RW_CTRL, 24'h519a04};289155:op_reg_data= {RW_CTRL, 24'h519b00};290156:op_reg_data= {RW_CTRL, 24'h519c06};291157:op_reg_data= {RW_CTRL, 24'h519d82};292158:op_reg_data= {RW_CTRL, 24'h519e38};// AWB control // Gamma 伽玛曲线293159:op_reg_data= {RW_CTRL, 24'h548001};// Gamma bias plus on, bit[0]294160:op_reg_data= {RW_CTRL, 24'h548108};295161:op_reg_data= {RW_CTRL, 24'h548214};296162:op_reg_data= {RW_CTRL, 24'h548328};297163:op_reg_data= {RW_CTRL, 24'h548451};298164:op_reg_data= {RW_CTRL, 24'h548565};299165:op_reg_data= {RW_CTRL, 24'h548671};300166:op_reg_data= {RW_CTRL, 24'h54877d};301167:op_reg_data= {RW_CTRL, 24'h548887};302168:op_reg_data= {RW_CTRL, 24'h548991};303169:op_reg_data= {RW_CTRL, 24'h548a9a};304170:op_reg_data= {RW_CTRL, 24'h548baa};305171:op_reg_data= {RW_CTRL, 24'h548cb8};306172:op_reg_data= {RW_CTRL, 24'h548dcd};307173:op_reg_data= {RW_CTRL, 24'h548edd};308174:op_reg_data= {RW_CTRL, 24'h548fea};309175:op_reg_data= {RW_CTRL, 24'h54901d};// color matrix ⾊彩矩阵310176:op_reg_data= {RW_CTRL, 24'h53811e};// CMX1 for Y311177:op_reg_data= {RW_CTRL, 24'h53825b};// CMX2 for Y312178:op_reg_data= {RW_CTRL, 24'h538308};// CMX3 for Y313179:op_reg_data= {RW_CTRL, 24'h53840a};// CMX4 for U314180:op_reg_data= {RW_CTRL, 24'h53857e};// CMX5 for U315181:op_reg_data= {RW_CTRL, 24'h538688};// CMX6 for U316182:op_reg_data= {RW_CTRL, 24'h53877c};// CMX7 for V317183:op_reg_data= {RW_CTRL, 24'h53886c};// CMX8 for V318184:op_reg_data= {RW_CTRL, 24'h538910};// CMX9 for V319185:op_reg_data= {RW_CTRL, 24'h538a01};// sign[9]320186:op_reg_data= {RW_CTRL, 24'h538b98}; // sign[8:1] // UV adjust UV⾊彩饱和度调整321187:op_reg_data= {RW_CTRL, 24'h558006};// saturation on, bit[1]322188:op_reg_data= {RW_CTRL, 24'h558340};323189:op_reg_data= {RW_CTRL, 24'h558410};324190:op_reg_data= {RW_CTRL, 24'h558910};325191:op_reg_data= {RW_CTRL, 24'h558a00};326192:op_reg_data= {RW_CTRL, 24'h558bf8};327193:op_reg_data= {RW_CTRL, 24'h501d40};// enable manual offset of contrast// CIP 锐化和降噪328194:op_reg_data= {RW_CTRL, 24'h530008};// CIP sharpen MT threshold 1329195:op_reg_data= {RW_CTRL, 24'h530130};// CIP sharpen MT threshold 2330196:op_reg_data= {RW_CTRL, 24'h530210};// CIP sharpen MT offset 1331197:op_reg_data= {RW_CTRL, 24'h530300};// CIP sharpen MT offset 2332198:op_reg_data= {RW_CTRL, 24'h530408};// CIP DNS threshold 1333199:op_reg_data= {RW_CTRL, 24'h530530};// CIP DNS threshold 2334200:op_reg_data= {RW_CTRL, 24'h530608};// CIP DNS offset 1335201:op_reg_data= {RW_CTRL, 24'h530716};// CIP DNS offset 2336202:op_reg_data= {RW_CTRL, 24'h530908};// CIP sharpen TH threshold 1337203:op_reg_data= {RW_CTRL, 24'h530a30};// CIP sharpen TH threshold 2338204:op_reg_data= {RW_CTRL, 24'h530b04};// CIP sharpen TH offset 1339205:op_reg_data= {RW_CTRL, 24'h530c06};// CIP sharpen TH offset 2340206:op_reg_data= {RW_CTRL, 24'h502500};341207:op_reg_data= {RW_CTRL, 24'h300802}; // wake up from standby, bit[6]342343//set OV5640 to video mode 720p344208:op_reg_data= {RW_CTRL, 24'h303521};// PLL input clock =24Mhz, PCLK =84Mhz345209:op_reg_data= {RW_CTRL, 24'h303669};// PLL346210:op_reg_data= {RW_CTRL, 24'h3c0707}; // lightmeter 1 threshold[7:0]347211:op_reg_data= {RW_CTRL, 24'h382047}; // flip348212:op_reg_data= {RW_CTRL, 24'h382100}; // mirror349213:op_reg_data= {RW_CTRL, 24'h381431}; // timing X inc350214:op_reg_data= {RW_CTRL, 24'h381531}; // timing Y inc351215:op_reg_data= {RW_CTRL, 24'h380000}; // HS352216:op_reg_data= {RW_CTRL, 24'h380100}; // HS353217:op_reg_data= {RW_CTRL, 24'h380200}; // VS354218:op_reg_data= {RW_CTRL, 24'h3803fa}; // VS355219:op_reg_data= {RW_CTRL, 24'h38040a}; // HW (HE)356220:op_reg_data= {RW_CTRL, 24'h38053f}; // HW (HE)357221:op_reg_data= {RW_CTRL, 24'h380606}; // VH (VE)358222:op_reg_data= {RW_CTRL, 24'h3807a9}; // VH (VE)359223:op_reg_data= {RW_CTRL, 24'h380805}; // DVPHO (1280)360224:op_reg_data= {RW_CTRL, 24'h380900}; // DVPHO (1280)361225:op_reg_data= {RW_CTRL, 24'h380a02}; // DVPVO (720)->362226:op_reg_data= {RW_CTRL, 24'h380bd0}; // DVPVO (720)->363227:op_reg_data= {RW_CTRL, 24'h380c07}; // HTS364228:op_reg_data= {RW_CTRL, 24'h380d64}; // HTS365229:op_reg_data= {RW_CTRL, 24'h380e02}; // VTS366230:op_reg_data= {RW_CTRL, 24'h380fe4}; // VTS367231:op_reg_data= {RW_CTRL, 24'h381304}; // timing V offset368232:op_reg_data= {RW_CTRL, 24'h361800};369233:op_reg_data= {RW_CTRL, 24'h361229};370234:op_reg_data= {RW_CTRL, 24'h370952};371235:op_reg_data= {RW_CTRL, 24'h370c03};372236:op_reg_data= {RW_CTRL, 24'h3a0202}; // 60Hz max exposure373237:op_reg_data= {RW_CTRL, 24'h3a03e0}; // 60Hz max exposure374238:op_reg_data= {RW_CTRL, 24'h3a0800}; // B50 step375239:op_reg_data= {RW_CTRL, 24'h3a096f}; // B50 step376240:op_reg_data= {RW_CTRL, 24'h3a0a00}; // B60 step377241:op_reg_data= {RW_CTRL, 24'h3a0b5c}; // B60 step378242:op_reg_data= {RW_CTRL, 24'h3a0e06}; // 50Hz max band379243:op_reg_data= {RW_CTRL, 24'h3a0d08}; // 60Hz max band380244:op_reg_data= {RW_CTRL, 24'h3a1402}; // 50Hz max exposure381245:op_reg_data= {RW_CTRL, 24'h3a15e0}; // 50Hz max exposure382246:op_reg_data= {RW_CTRL, 24'h400402}; // BLC line number383247:op_reg_data= {RW_CTRL, 24'h30021c}; // reset JFIFO, SFIFO, JPG384248:op_reg_data= {RW_CTRL, 24'h3006c3}; // disable clock of JPEG2x, JPEG385249:op_reg_data= {RW_CTRL, 24'h471303}; // JPEG mode 3386250:op_reg_data= {RW_CTRL, 24'h440704}; // Quantization sacle387251:op_reg_data= {RW_CTRL, 24'h460b37};388252:op_reg_data= {RW_CTRL, 24'h460c20};389253:op_reg_data= {RW_CTRL, 24'h483716}; // MIPI global timing390254:op_reg_data= {RW_CTRL, 24'h382404}; // PCLK manual divider391255:op_reg_data= {RW_CTRL, 24'h5001a3}; // SDE on, CMX on, AWB on, scale on392256:op_reg_data= {RW_CTRL, 24'h350300}; // AEC/AGC on393257:op_reg_data= {RW_CTRL, 24'h301602}; //Strobe output enable394258:op_reg_data= {RW_CTRL, 24'h3b070a}; //FREX strobe mode1395//strobe flash and frame exposure396259:op_reg_data={RW_CTRL, 24'h3b0083}; //STROBE CTRL: strobe request ON, Strobe mode: LED3 397260:op_reg_data={RW_CTRL, 24'h3b0000}; //STROBE CTRL: strobe request OFF398399default:op_reg_data={RW_CTRL, 24'h000000};400endcase401end402403404endmodulereg_config上电时序模块:1 `timescale 1ns / 1ps234module setup(5input clk,//50MHZ6input rst_n,7output reg init_en,89output reg ov_pwdn1,10output reg ov_rst_n1,11output reg ov_pwdn2,12output reg ov_rst_n213 );1415parameter MS_CYC = 50_000;1617reg [16-1:0] ms_cnt;18wire add_ms_cnt;19wire end_ms_cnt;20reg [ (5-1):0] wait_cnt ;21wire add_wait_cnt ;22wire end_wait_cnt ;23reg [5-1:0] N;24reg [ (2-1):0] phase_cnt ;25wire add_phase_cnt ;26wire end_phase_cnt ;27reg setup_done;28。

摄像头配置指令模块解析

摄像头配置指令模块的功能:列出了配置ov7670的寄存器的配置方式,包括了配置寄存器的顺序、是否读寄存器、是否写寄存器以及寄存器的地址和写入寄存器的数据。

一、信号意义

二、举例说明

第1行,REG_NUM用来表示要配置的寄存器个数,164表示需要对164个寄存器进行操作。

reg_cnt中的01234等,则表示配置寄存器的顺序。

第4行代码最先配置,然后是第5行至第8行。

add_wdata的结构如下表:

例如第4行,add_wdata的值为{2’b11,16’h1204}。

表示先产生写命令,写数据为8’h04,写地址为8’h12。

然后再产生读命令,读地址为8’h12。

例如第5行,add_wdata的值为{2’b10,16’h40d0}。

表示产生读命令,读地址为8’h40。

例如第6行,add_wdata的值为{2’b01,16’h3a04}。

表示产生写命令,写数据为8’h04,写地址为8’h3a。

例如第7行,add_wdata的值为{2’b00,16’h3dc8}。

表示不产生任何写命令和读命令,跳过。

废话后面说,先直接上OV7670寄存器的配置部分const uint8_t OV7670_Reg[][2]={//Frame Rate Adjustment for 24Mhz input clock//30fps PCLK=24MHz{0x11, 0x80},//软件应用手册上设置的是0x80,例程设置的是0x00{0x6b, 0x0a},//PLL控制,软件应用手册上设置的是0x0a,例程设置的是0x40,将PLL调高的话就会产生花屏{0x2a, 0x00},{0x2b, 0x00},{0x92, 0x00},{0x93, 0x00},{0x3b, 0x0a},//Output format{0x12, 0x14},//QVGA(320*240)、RGB//RGB555/565 option(must set COM7[2] = 1 and COM7[0] = 0){0x40, 0x10},//RGB565,effective only when RGB444[1] is low{0x8c, 0x00},//Special effects - 特效//normal{0x3a, 0x04},{0x67, 0xc0},{0x68, 0x80},//Mirror/VFlip Enable - 水平镜像/竖直翻转使能{0x1e, 0x37},//修改配置值将产生图像显示上下或左右颠倒//Banding Filter Setting for 24Mhz Input Clock - 条纹滤波器//30fps for 60Hz light frequency//{0x13, 0xe7},//banding filer enable//{0x9d, 0x98},//50Hz banding filer//{0x9e, 0x7f},//60Hz banding filer//{0xa5, 0x02},//3 step for 50Hz//{0xab, 0x03},//4 step for 60Hz//{0x3b, 0x02},//select 60Hz banding filer//Simple White Balance - 白平衡//{0x13, 0xe7},//AWB、AGC、AGC Enable and ...//{0x6f, 0x9f},//simple AWB//AWBC - 自动白平衡控制(Automatic white balance control)//{0x43, 0x14},//用户手册里这些寄存器的值都是保留(Reserved),不用设置的呀?//{0x44, 0xf0},//{0x45, 0x34},//{0x46, 0x58},//{0x47, 0x28},//{0x48, 0x3a},//AWB Control//{0x59, 0x88},//用户手册连寄存器都是保留,初始值都没提供//{0x5a, 0x88},//{0x5b, 0x44},//{0x5c, 0x67},//{0x5d, 0x49},//{0x5e, 0x0e},//AWB Control//{0x6c, 0x0a},//{0x6d, 0x55},//{0x6e, 0x11},//{0x6f, 0x9f},//AGC/AEC - Automatic Gain Control自动增益补偿/Automatic exposure Control自动曝光控制//{0x00, 0x00},//{0x14, 0x20},//{0x24, 0x75},//{0x25, 0x63},//{0x26, 0xA5},//AEC algorithm selection - AEC公式选择//{0xaa, 0x94},//基于平均值的AEC算法Average-based AEC algorithm/基于直方图的AEC算法Histogram-based AEC algorithm//基于直方图的AGC/AEC的控制//{0x9f, 0x78},//{0xa0, 0x68},//{0xa6, 0xdf},//{0xa7, 0xdf},//{0xa8, 0xf0},//{0xa9, 0x90},//Fix Gain Control - 固定增益控制//{0x69, 0x5d},//Fix gain for Gr channel/for Gb channel/for R channel/for B channel//Color saturation 颜色饱和度+ 0//{0x4f, 0x80},//{0x50, 0x80},//{0x51, 0x00},//{0x52, 0x22},//{0x53, 0x5e},//{0x54, 0x80},//{0x58, 0x9e},//Brightness - 亮度+ 0//{0x55, 0x00},//Contrast - 对比度+ 0//{0x56, 0x40},//Gamma Curve - 伽马曲线//{0x7a, 0x20},//{0x7b, 0x1c},//{0x7c, 0x28},//{0x7d, 0x3c},//{0x7e, 0x55},//{0x7f, 0x68},//{0x80, 0x76},//{0x81, 0x80},//{0x82, 0x88},//{0x83, 0x8f},//{0x84, 0x96},//{0x85, 0xa3},//{0x86, 0xaf},//{0x87, 0xc4},//{0x88, 0xd7},//{0x89, 0xe8},//Matrix Coefficient - 色彩矩阵系数//{0x4f, 0x80},//{0x50, 0x80},//{0x51, 0x00},//{0x52, 0x22},//{0x53, 0x5e},//{0x54, 0x80},//Lens Correction Option - 镜头补偿选项 //{0x62, 0x00},//{0x63, 0x00},//{0x64, 0x04},//{0x65, 0x20},//{0x66, 0x05},//{0x94, 0x04},//effective only when LCC5[2] is high//{0x95, 0x08},//effective only when LCC5[2] is high//注释这些配置的话,就倾斜显示,并显示多块,这到底是控制什么的?跟时序图有关?{0x17, 0x16},//行频Horizontal Frame开始高八位(低三位在HREF[2:0]){0x18, 0x04},//行频Horizontal Frame结束高八位(低三位在HREF[5:3]){0x19, 0x02},//场频Vertical Frame开始高八位(低二位在VREF[1:0]){0x1a, 0x7b},//场频Vertical Frame结束高八位(低二位在VREF[3:2]){0x32, 0x80},//HREF{0x03, 0x06},//VREF//注释这个配置的话,就显示花屏了{0x15, 0x02},//配置PCLK、HREF、VSYNC相关//Automatic black Level Compensation - 自动黑电平校正{0xb0, 0x84},//调试时注释这项配置时,颜色显示不正常了,红色练绿色,绿色变红色,但用户手册对这寄存器是保留RSVD//{0xb1, 0x0c},//{0xb2, 0x0e},//{0xb3, 0x82},//{0xb8, 0x0a},//SCALING_xx寄存器//{0x70, 0x00},//{0x71, 0x00},//{0x72, 0x11},//{0x73, 0x08},//{0x3e, 0x00},//ADC//{0x37, 0x1d},//ADC控制ADC Control//{0x38, 0x71},//ADC和模拟共模控制ADC and Analog Common Mode Control//{0x39, 0x2a},//ADC偏移控制ADC Offset Control//零杂的寄存器//{0x92, 0x00},//空行低八位Dummy Line low 8 bits//{0xa2, 0x02},//像素时钟延时//{0x0c, 0x0c},//{0x10, 0x00},//{0x0d, 0x01},//{0x0f, 0x4b},//{0x3c, 0x78},//{0x74, 0x19},//用户手册里这几个寄存器都是保留RSVD//{0x0e, 0x61},//{0x16, 0x02},//{0x21, 0x02},//{0x22, 0x91},//{0x29, 0x07},//{0x33, 0x0b},//{0x35, 0x0b},//{0x4d, 0x40},//{0x4e, 0x20},//{0x8d, 0x4f},//{0x8e, 0x00},//{0x8f, 0x00},//{0x90, 0x00},//{0x91, 0x00},//{0x96, 0x00},//{0x9a, 0x80},};刚开始学OV7670摄像头,我想大家跟我一样心里很毛躁吧,一个模块需要你配置100多个寄存器,但用户手册对寄存器的介绍却草草的一笔带过,自己无从下手啊,只能看开发板给的例程和上网找一些大虾的帖子了。

OV7670-CMOS摄像头使用说 明2014.2.10 参赛平台1.OV7670带FIFO 模块1.简介:OV7670带FIFO 模块,是针对慢速的MCU 能够实现图像采集控制推出的带有缓冲存储空间的一种模块。

这种模块增加了一个FIFO (先进先出)存储芯片,同样包含30w 像素的CMOS 图像感光芯片,3.6mm 焦距的镜头和镜头座,板载CMOS 芯片所需要的各种不同电源(电源要求详见芯片的数据文件),板子同时引出控制管脚和数据管脚,方便操作和使用。

图1.OV7670带FIFO模块 2.管脚定义:参赛平台如图,控制传感器所需的管脚定义如下:3V3-----输入电源电压(推荐使用3.3,5V 也可,但不推荐)GDN-----接地点SIO_C---SCCB 接口的控制时钟(注意:部分低级单片机需要上拉控制,和I2C 接口类似)SIO_D---SCCB 接口的串行数据输入(出)端(注意:部分低级单片机需要上拉控制,和I2C 接口类似) VSYNC---帧同步信号(输出信号)HREF----行同步信号(输出信号)PCLK----像素时钟(输出信号)XCLCK---时钟信号(输入信号)D0-D7---数据端口(输出信号)RESTE---复位端口(正常使用拉高)PWDN----功耗选择模式(正常使用拉低)STROBE—拍照闪光控制端口(正常使用可以不需要)FIFO_RCK---FIFO 内存读取时钟控制端FIFO_WR_CTR----FIFO 写控制端(1为允许CMOS 写入到FIFO,0为禁止) FIFO_OE----FIFO 关断控制FIFO_WRST—FIFO 写指针服务端FIFO_RRST—FIFO 读指针复位端 参赛平台图7.FIFO摄像头接口定义3.控制方式说明由于采用了FIFO 做为数据缓冲,数据采集大大简便,用户只需要关心是如何读取即可,不需要关心具体数据是如何采集到的,这样可减小甚至不用关心CMOS 的控制以及时序关系,就能够实现图像的采集。

手机摄像头功能由多个功能模块组成,主要三个部分,采集,加工,显示。

(1)采集部分由感光的sensor完成,通过CAM IF接口与手机芯片内的CAM连接。

(2)CAM对CAM IF数据进行加工,主要是格式转换,特殊效果等。

最终处理出来的一帧数据,存在内存中。

(3)手机的刷新线程,使用手机内部的DMA功能,或者OVERLAY技术,把处理好的camera图像,显示到LCD上。

刷新部分,不在camera框架范围内,后面只做简单讨论。

图1:Camera典型硬件模块图2 Sensor简介Sensor是对图像的采集系统,通常采用的是ov系列的芯片。

如ov2655等。

通常包含两路接口:(1)控制总线:Sensor也是一个智能嵌入式系统,一般通过I2C总线与手机芯片通信。

手机可以通过I2C读写Sensor的寄存器,改变Sensor的参数,从而改变其工作方式。

(2)数据总线:Sensor通过CAM IF接口与CAM联系。

图2:sensor硬件连接图由图可知,sensor工作的条件需要:(1)电压供应,一般模拟电压,数字电压。

(2)工作时钟,通常为24M HZ的正弦波。

一般为手机芯片产生(3)SDA,SCL,i2c总线连接,sensor通常为从设备。

(4)standby控制线,手机芯片通过这条GPIO控制线,控制sensor的工作是否开启。

(5)Sensor输出给手机芯片的接口,CAM IF接口:(6)并行数据线,通常8位,10位。

分辨率高的sensor数据线需要更多。

(7)提供给手机芯片内集成的camera模块的PCLK,HCLK,VCLK.(像素同步信号,行同步信号,帧同步信号)。

Sensor通常产出稳定频率的数据图像流,手机芯片可以通过I2C总线接口,修改寄存器,改变帧频率。

也可以改变sensor的输出流的格式,通常采用yuv422格式。

3 CAM简介CAM就是将Sensor采集过来的数据,转换相应格式,及其他加工,最后存放到内存中。

寄存器00:AGC 增益控制Register 01 - rw: Blue gain controlRegister 02 - rw: Red gain controlRegister 03 - rw: 饱和度控制Register 04 & 05 - w: Reserved Register Register 06 - rw: 亮度控制Register 07 - rw: Angalog锐度控制Register [08] ~ [0B] - w: Reserved.Register 0C - rw:背景白平衡控制-蓝色通道Register 0D - rw: 背景白平衡控制–红色通道Register 0E ~ 0F- rw: ReservedRegister 10 - rw: 自动曝光控制寄存器Register 11 - rw: 时钟速率控制Register 12 - rw: Common control A Register 13 - rw: Common control B Register 14- rw: Common control C Register 15- rw: Common control D Register 16 - rw: Frame DropRegister 17 - rw: 水平窗口启动Register 18 - rw: 水平窗口结束Register 19- rw: 垂直窗口启动Register 1A- rw: 垂直窗口结束Register 1B- rw: 像素转换Register 1C- r: 制造ID高字节Register 1D- r: 制造ID低字节Register 1E ~ 1F- rw: ReservedRegister 20- rw: Common control ERegister 21- rw: Y通道偏移调整Register 22- rw: U通道偏移调整Register 23- rw: 晶体电流控制。

Register 24- rw: AEW 自动曝光白色像素比Register 25- rw: AEC自动曝光黑色像素比Register 26 - rw: Common control F Register 27 - rw: Common control G Register 28 - rw: Common control H Register 29 - rw: Common control IRegister [2A] - rw: 帧速率调整寄存器1 Register [2B] - rw: 帧速率调整寄存器2 Register [2C] - rw: Black Expanding Register Register [2D] - rw: Common Control J Register [2E]- rw: V 通道偏移调整Register 2F ~ 5F - w: ReservedRegister 60- rw: 信号处理Control A Register 61- rw: 信号处理Control BRegister 62- rw: RGB Gamma ControlRegister 63- rw: ReservedRegister 64- rw: Y Gamma ControlRegister 65- rw: 信号处理Control CRegister 66- rw: AWB 过程控制Register 67- rw: 颜色空间选择Register 68- rw: 信号处理Control DRegister 69- rw: 模拟锐度Register 6A- rw: 垂直边缘增强控制Register 6B-6E rw: ReservedRegister 6F - rw: 偶/奇噪声补偿控制Register 70 - rw: Common Control KRegister 71 - rw: Common Control JRegister 72- rw:水平同步第一边移Register 73 - rw: 水平同步第二边移Register 74 - rw: Common Control MRegister 75 - rw: Common Control NRegister 76 - rw: Common Control ORegister 77-7B - rw: ReservedRegister 7C - rw: Field Average Level Storage寄存器00:AGC 增益控制AGC<5:0> -增益设置为整个图像通道计算公式为:Gain = (AGC<3:0>/16+1)*(AGC<4>+1)*(AGC<5>+1); range (1x ~ 7.75x), AGC<5> and AGC<4> control SA2.寄存器3:饱和度控制SAT<7:0>-saturation adjustment(饱和度调整) for the UV channel based on the default setting;范围(-4dB〜+6dB)。

如果SAT<7:0>>[80],增加;若SAT<7:0><[80],减少Register 06- rw:亮度控制BRT<7:0> -亮度调整为Y/ RGB的基础上的默认设置通道;范围(-200mV的〜+200mv)。

如果BRT<7:0>>[80],亮度增加;如果BRT<7:0><[80],亮度减少。

该寄存器是自动/手动控制。

如果寄存器2D bit4 = 1,这个寄存器由芯片控制自动,如果写这个寄存器的值,这个值将被更新内部电路。

只有当2D bit4 =0,这个寄存器可以设置为任意值Register 07 - rw: Angalog锐度控制SHP<7:4> - Sharpness Threshold. 锐度阈值。

SHP<3:0> - Sharpness Magnitude. 锐度震级。

Register 0C - rw:白平衡控制背景-蓝色通道。

ABLU<4:0> -白平衡背景蓝色成分比例的调整。

调整分辨率0.625%,总范围为(20%- -20%),该寄存器用于抵消图像的背景蓝色构成比ABLU<5> -符号位。

如果“1“,降低背景蓝色的成份比例,“0“蓝色成分的比例增加Register 10 - rw:自动曝光控制寄存器AEC<7:0> -曝光时间设定,计算公式为隔行扫描:T EXPOSURE = T LINE x AEC(7:0);逐行扫描:T EXPOSURE = T LINE x AEC(7:0)x2;T LINE = Frame Time / 525if use 27MHz, T LINE = 63.5 uS范围:[00] - [7F] for Interlaced; [00] - [FF] for Progressive Scan.*只有当设置为手动设置模式时,这个寄存器设置才是有效的(寄存器13 bit0=0)如果13 bit0=1。

()如果寄存器13 bit0 =0,或寄存器29 bit7 = 1,寄存器将保持最后一个值不变(无论是从SCCB或AEC算法的结果输入)。

*在改变这个设置后,到达预期的曝光设置通常需要不少于两个场的时间Register 11 - rw:时钟速率控制CLK<5:0> -系统时钟预分频器; 这个寄存器定义芯片的像素时钟速率,公式为:(16 Bit mode) PCLK = (CLK_input / (( CLK<5:0> + 1) * 2))(8 Bit mode) PCLK = (CLK_input / ( CLK<5:0> + 1))SYN<7:6> -SYN7 = 0, SYN6 = 0: HSYNC negative, CHSYNC negative, VSYNC positive edge;SYN7 = 0, SYN6 = 1:.HSYNC negative, CHSYNC negative, VSYNC negative;SYN7 = 1, SYN6 = 0: HSYNC positive, CHSYNC negative, VSYNC positive.SYN7 = 1, SYN6 = 1: HSYNC negative, CHSYNC positive, VSYNC positive.*这项改变的效果是立竿见影的,但是,它通常需要对图像约两个场达到稳定状态COMA7–“1“软启动芯片复位,复位发生后,该芯片初始化为默认状态,所有的寄存器包括SCCB的内容设置为默认,此位是自复位后清除。

COMA6 - “1” selects mirror imageCOMA5 - “1” 使能AGC. “0” –停止AGC并且设置寄存器[00] 为初始值. 只在自动模式下起作用。

COMA4 -“1”选择8位数字输出格式Y U Y V Y U Y V ...COMA3 - “1” selects raw data signal as video data output, “0” selects YCrCb as video data output.COMA2 - “1”使能自动白平衡,“0” AWB stop and AWB register [01] and [02] value is held at last updated value.COMA1 - “1”选择彩条测试模式输出COMA0 - “1” select precise A/D Black Level Compensation (BLC) line method. “0” use standard black levelcompensation to do A/D BLC field method which is more stablebut less precise.COMB7 - Reserved.COMB6 - Reserved.COMB5 - “1”选择8位数据模式,Y/CrCb and RGB,“0”选择16位数据模式,数据go to both Y<7:0> bus and UV<7:0> bus.COMB4 - “0”使能数字输出CCIR601格式。