Silvaco器件仿真ppt课件

- 格式:ppt

- 大小:3.11 MB

- 文档页数:10

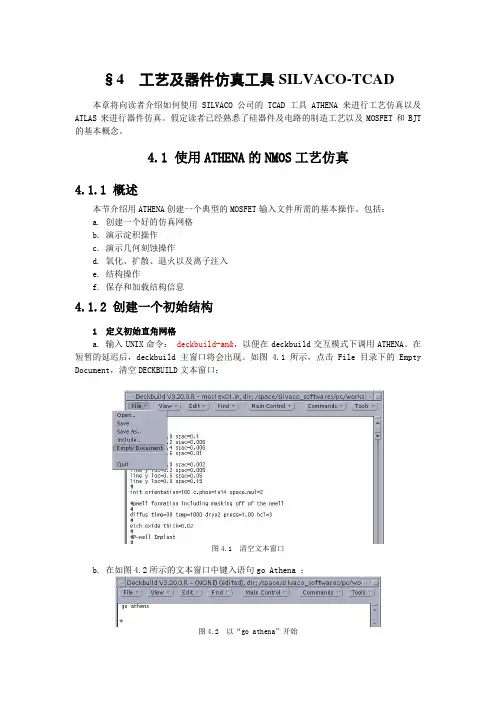

§4 工艺及器件仿真工具SILVACO-TCAD本章将向读者介绍如何使用SILVACO公司的TCAD工具ATHENA来进行工艺仿真以及ATLAS来进行器件仿真。

假定读者已经熟悉了硅器件及电路的制造工艺以及MOSFET和BJT 的基本概念。

4.1 使用ATHENA的NMOS工艺仿真4.1.1 概述本节介绍用ATHENA创建一个典型的MOSFET输入文件所需的基本操作。

包括:a. 创建一个好的仿真网格b. 演示淀积操作c. 演示几何刻蚀操作d. 氧化、扩散、退火以及离子注入e. 结构操作f. 保存和加载结构信息4.1.2 创建一个初始结构1 定义初始直角网格a. 输入UNIX命令:deckbuild-an&,以便在deckbuild交互模式下调用ATHENA。

在短暂的延迟后,deckbuild主窗口将会出现。

如图4.1所示,点击File目录下的Empty Document,清空DECKBUILD文本窗口;图4.1 清空文本窗口b. 在如图4.2所示的文本窗口中键入语句go Athena ;图4.2 以“go athena”开始接下来要明确网格。

网格中的结点数对仿真的精确度和所需时间有着直接的影响。

仿真结构中存在离子注入或者形成PN结的区域应该划分更加细致的网格。

c. 为了定义网格,选择Mesh Define菜单项,如图4.3所示。

下面将以在0.6μm×0.8μm 的方形区域内创建非均匀网格为例介绍网格定义的方法。

图4.3 调用ATHENA网格定义菜单2 在0.6μm×0.8μm的方形区域内创建非均匀网格a. 在网格定义菜单中,Direction(方向)栏缺省为X;点击Location(位置)栏并输入值0;点击Spacing(间隔)栏并输入值0.1;b. 在Comment(注释)栏,键入“Non-Uniform Grid(0.6um x 0.8um)”,如图4.4所示;c. 点击insert键,参数将会出现在滚动条菜单中;图4.4 定义网格参数图 4.5 点击Insert键后d. 继续插入X方向的网格线,将第二和第三条X方向的网格线分别设为0.2和0.6,间距均为0.01。

器件仿真软件模块ATLAS2D 硅器件仿真器S-Pisces/Device3DS-Pisces 是一个2D 器件仿真器,应用于合并了漂流扩散和能量平衡传输方程的硅化技术。

它拥有大量的可用物理模型集合,包括表面/体积迁移率、复合、碰撞电离和隧道模型等。

典型的应用包括MOS ,双极和BiCMOS 技术。

所有物理模型的性能已被扩展到深亚微米器件、SOI 器件和非易失性存贮器结构等。

它也可计算所有可测量的电学参数。

对于MOS 技术,这些参数包括门极和漏极特性,亚阈值漏电,衬底电流和穿通电压。

而双极技术则可预测Gummel 图和饱和曲线。

其他可计算的特性包括击穿行为、纽结和突返效应、CMOS 闩锁效应、低温和高温操作、AC参数和本征开关时间。

完全MOS 特性表征右图描述的是寄生双极造成的击穿曲线中的突返效应的仿真。

右图显示使用能量平衡和经典的漂移扩散计算的MOSFET 中的衬底电流。

使用能量平衡模型计算的行为更好地吻合测量的行为,因为它包括过冲电压到和非局部碰撞电离。

上面两图显示了分别针对不同的VGS 和VBS 的ID-VD 和ID-VGS 仿真的数据。

这些特性可直接加载到UTMOST ,并提取出等效的BSIM3或BSIM4 Spice 模型。

因此在任何可用的晶片制造之前即可表征新的工艺。

上图显示0.3µmMOSFET 中的电子温度分布。

碰撞电离率是基于载流子温度,而不是局部电场。

因此产生非局部效应。

左图显示的LDD MOSFET 结构是在ATHENA 工艺仿真器中仿真的,其最终结构可直接输入到ATLAS 中。

漏极电压14.5V 用于漏极接触,图上也添加了电场轮廓线。

完全双极特性表征S-Pisces仿真双极器件性能的各个方面。

如下图所示的复杂结构可从ATHENA中载入。

DC特性如Gummel图, b f vs. I c 和 I c vs. VCE均可被轻松仿真。

通过使用S-Pisces的时域模式可执行本征开关瞬态速度。

4.1.10多晶硅栅的淀积淀积可以用来产生多层结构。

共形淀积是最简单的淀积方式,并且在各种淀积层形状要求不是非常严格的情况下使用。

NMOS工艺中,多晶硅层的厚度约为2000 Å,因此可以使用共形多晶硅淀积来完成。

为了完成共形淀积,从ATHENA Commands菜单中依次选择Process、Deposit和Deposit…菜单项。

ATHENA Deposit菜单如图4.30所示;a.在Deposit菜单中,淀积类型默认为Conformal;在Material菜单中选择Polysilicon,并将它的厚度值设为0.2;在Grid specification参数中,点击Total number of layers并将其值设为10。

(在一个淀积层中设定几个网格层通常是非常有用的。

在这里,我们需要10个网格层用来仿真杂质在多晶硅层中的传输。

)在Comment一栏中添加注释Conformal Polysilicon Deposition,并点击WRITE键;b.下面这几行将会出现在文本窗口中:#Conformal Polysilicon Deposition图4.30 ATHENA 淀积菜单deposit polysilicon thick=0.2 divisions=10c.点击DECKBUILD控制栏上的Cont键继续进行A THENA仿真;d.还是通过DECKBUILD Tools菜单的Plot和Plot structure…来绘制当前结构图。

创建后的三层结构如图4.31所示。

图4.31 多晶硅层的共形淀积4.1.11简单的几何图形刻蚀接下来就是多晶硅的栅极定义。

这里我们将多晶硅栅极的左边边缘定为x=0.35μm,中心定为x=0.6μm。

因此,多晶硅应从左边x=0.35μm开始进行刻蚀,如图4.32所示。

图4.32 ATHENA Etch菜单a.在DECKBUILD Commands菜单中依次选择Process、Etch和Etch…。