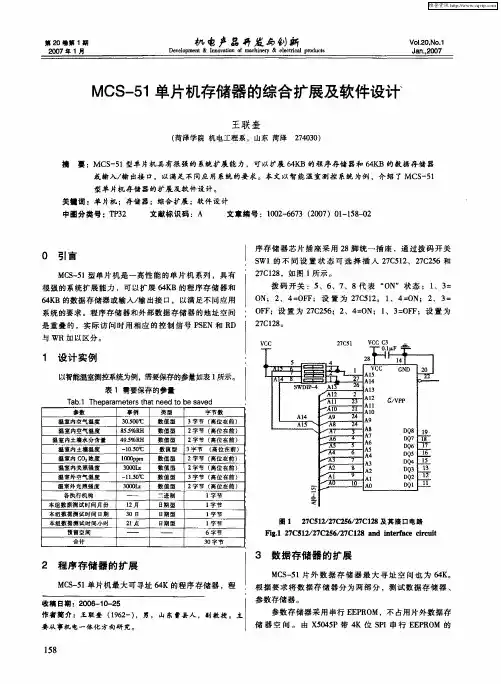

51单片机大容量数据存储器的扩展

- 格式:doc

- 大小:79.90 KB

- 文档页数:13

第八章MCS-51单片机存储器的扩展第一节MCS-51单片机存储器的概述(一)学习要求1、熟悉MCS-51 单片机的系统总线及系统总线扩展结构2、掌握常用的片选方法:线选法和全地址译码法。

(二)内容提要1、三总线的扩展方法单片机内资源少,容量小,在进行较复杂过程的控制时,它自身的功能远远不能满足需要。

为此,应扩展其功能。

MCS-51单片机的扩展性能较强,根据需要,可扩展。

三总线是指地址总线、数据总线、控制总线。

1)地址总线MCS-51 单片机地址总线宽度为16 位,寻址范围为64K。

地址信号:P0 作为地址线低8 位,P2 口作为地址线高8 位。

2)数据总线MCS-51 单片机的数据总线宽度为8 位。

数据信号:P0 口作为8 位数据口,P0 口在系统进行外部扩展时与低8 位地址总线分时复用。

3)控制总线主要的控制信号有/WR 、/RD 、ALE 、/PSEN 、/EA 等。

2、系统的扩展能力MCS-51 单片机地址总线宽度为16 位,因此它可扩展的程序存储器和数据存储器的最大容量是64K(216)。

1)线选法线选法就是将多余的地址总线(即除去存储容量所占用的地址总线外)中的某一根地址线作为选择某一片存储或某一个功能部件接口芯片的片选信号线。

一定会有一些这样的地址线,否则就不存在所谓的“选片”的问题了。

每一块芯片均需占用一根地址线,这种方法适用于存储容量较小,外扩芯片较少的小系统,其优点是不需地址译码器,硬件节省,成本低。

缺点是外扩器件的数量有限,而且地址空间是不连续的。

2)全地址译码法由于线选法中一根高位地址线只能选通一个部件,每个部件占用了很多重复的地址空间,从而限制了外部扩展部件的数量。

采用译码法的目的是减少各部件所占用的地址空间,以增加扩展部件的数量。

3)译码器级连当组成存储器的芯片较多,不能用线选法片选,又没有大位数译码器时,可采用多个小位数译码器级连的方式进行译码片选.4)译码法与线选法的混合使用译码法与线选法的混合使用时,凡用于译码的地址线就不应再用于线选,反之,已用于线选的地址线就不应再用于译码器的译码输入信号.(三)习题与思考题1. 简要说明MCS-51 单片机的扩展原理。

单片机外部RAM扩展模块MCS-51系列单片机外部RAM为64K,在一些特殊场合下,远不能满足需要,本文就AT89C51讨论MCS-51系列单片机大容量RAM的扩首先介绍128K随机读取RAM HM628128。

HM628128是32脚双列直插式128K静态随机读取RAM,它具有容量大、功耗低、价格便宜、集成度高、速度快、设计和使用方便等特点。

如若在系统中加入掉电保护电路,保护数据有很高的可靠性,可以和EEPROM相媲美。

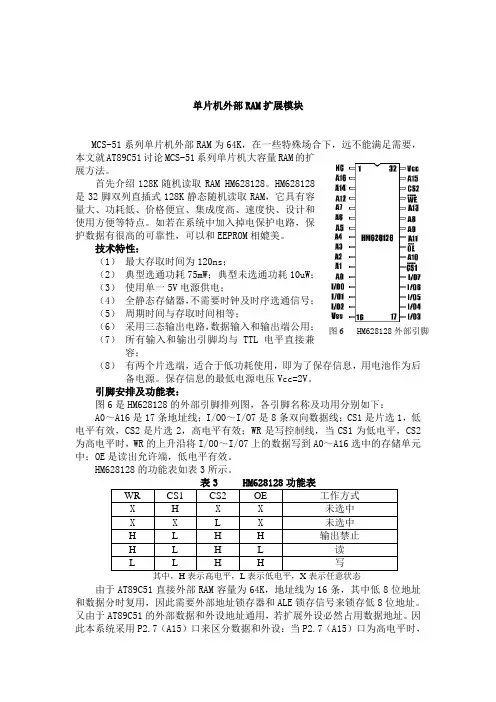

技术特性:(1)最大存取时间为120ns;(2)典型选通功耗75mW;典型未选通功耗10uW;(3)使用单一5V电源供电;(4)全静态存储器,不需要时钟及时序选通信号;(5)周期时间与存取时间相等;(6)采用三态输出电路,数据输入和输出端公用;图6 HM628128外部引脚(7)所有输入和输出引脚均与TTL电平直接兼容;(8)有两个片选端,适合于低功耗使用,即为了保存信息,用电池作为后备电源。

保存信息的最低电源电压Vcc=2V。

引脚安排及功能表:图6是HM628128的外部引脚排列图,各引脚名称及功用分别如下:A0~A16是17条地址线;I/O0~I/O7是8条双向数据线;CS1是片选1,低电平有效,CS2是片选2,高电平有效;WR是写控制线,当CS1为低电平,CS2为高电平时,WR的上升沿将I/O0~I/O7上的数据写到A0~A16选中的存储单元中;OE是读出允许端,低电平有效。

HM628128的功能表如表3所示。

其中,H表示高电平,L表示低电平,X表示任意状态由于AT89C51直接外部RAM容量为64K,地址线为16条,其中低8位地址和数据分时复用,因此需要外部地址锁存器和ALE锁存信号来锁存低8位地址。

又由于AT89C51的外部数据和外设地址通用,若扩展外设必然占用数据地址。

因此本系统采用P2.7(A15)口来区分数据和外设:当P2.7(A15)口为高电平时,选择外部数据;P2.7(A15)口为低电平时,则为外设。

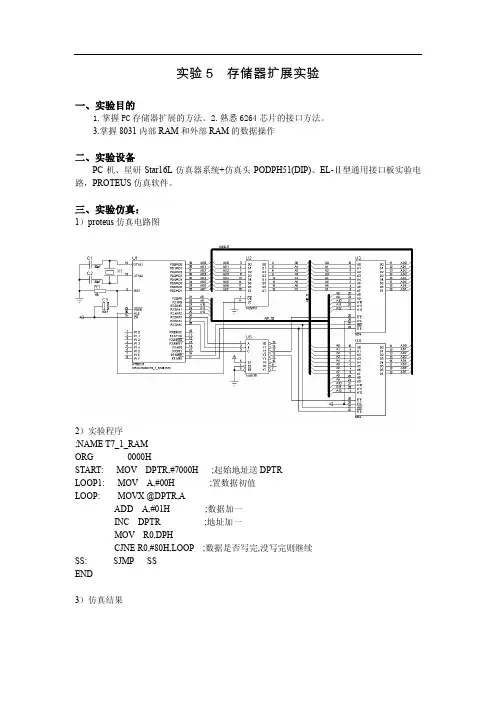

实验5 存储器扩展实验一、实验目的1.掌握PC存储器扩展的方法。

2.熟悉6264芯片的接口方法。

3.掌握8031内部RAM和外部RAM的数据操作二、实验设备PC机、星研Star16L仿真器系统+仿真头PODPH51(DIP)、EL-Ⅱ型通用接口板实验电路,PROTEUS仿真软件。

三、实验仿真:1)proteus仿真电路图2)实验程序;NAME T7_1_RAMORG 0000HSTART: MOV DPTR,#7000H ;起始地址送DPTRLOOP1: MOV A,#00H ;置数据初值LOOP: MOVX @DPTR,AADD A,#01H ;数据加一INC DPTR ;地址加一MOV R0,DPHCJNE R0,#80H,LOOP ;数据是否写完,没写完则继续SS: SJMP SSEND3)仿真结果运行上面的程序,由于设定起始地址为7000,而P2.0~P2.4分别作为地址线A8~A12,P2.5~P2.7分别接74ls138的ABC三个口,且38译码器的Y2接6264-U3的片选口CE,与接6264-U4的片选口CE,所以此时CBA为011,则选择的存储器为U4,将00~FF这组数据分别送到U4的以7000H为起始地址的单元中,并循环放置(即proteus仿真结果中的1000H 地址);若将程序中的起始地址改为5000H,检验是否写完数据的数值#80H改为#60H,则此时CBA为010,此时选择的是U3存储器,结果与选择U4时一样。

证明这些地址都可用,如果不可用,则在写入数据时所有地址单元中的数值保持为FF。

四、实验台操作1)接线实验台已将内部线路接好,可用地址范围为4000~7FFFH2)实验结果实验结果基本与仿真结果一致。

51单片机扩展外部RAM

今天这个是是以前做过的,没做成,扩展ROM的时候失败了~~不过今天主要的就是扩展外部的RAM,这个相对比较简单点,不想外部的ROM还要设置太多的编译器~~

单片机扩展外部RAM

一、扩展总线

1、简介(这种扩展是基于总线扩展的,所以,P0、P2口就已经不可以再做它用了)

1)数据总线宽度为8位,由P0口提供;

2)地址总线宽度为16位,可寻址范围2的16次,也就是64K。

低8位

A7~A0由P0口经地址锁存器提供,高8位A15~A8由P2口提供。

由于P0口是数据、地址分时复用,所以P0口输出的低8位必须用地址锁存器进行锁存;

3)控制总线由RD、WR、PSEN、ALE和EA等信号组成,用于读/写控制、片外RAM选通、地址锁存控制和片内、片外RAM选择。

地址锁存器一般选用带三态输出缓冲输出的8D锁存器74LS373。

2、片外RAM的操作时序

进行RAM的扩展,其扩展方法较为简单容易,这是由单片机的优良扩展性

能解决的。

单片机的地址总线为16位,扩展的片外RAM的做大容量为

64KB,地址为0000H~FFFFH。

1)由于51单片机采用不同的控制信号指令,尽管RAM和ROM地址是重

叠的,也不会发送混乱。

2)51单片机对片内和片外ROM的访问使用相同的指令,两者的选择是由。

51 单片机片外扩展RAM

一.概述

普通51 单片机可以片外扩展ROM 和RAM 各64K 字节的空间,在实际应用中很少扩展外部ROM,一般都是扩展RAM,因为普通51 单片机的内部RAM 实在太少,只有128-256 字节,处理数据量较大时往往不

够用。

而片外扩展RAM 需要占用P0 口、P2 口和P3.6、P3.7,消耗了18 个IO 口,导致IO 口又不够用。

为了解决以上矛盾,大容量的51 单片机(增强型51 单片机)应运而生,这种单片机一般内置1K-16K 的RAM 和16K-64K 的ROM,价格也相对昂贵。

在某些情况下,用普通51 单片机通过片外扩展RAM 要比直接使用增强型51 单片机更能节约成本。

所以,学习51 单片机片外扩展RAM 是很有必要的。

二.电路设计

在WSF-51DB 开发板上,扩展了32K RAM(HM62256B),地址锁存芯片用74HC573。

如果片外扩展RAM,P0 口作为数据和地址低字节的复用端口,不需要加上拉排阻,当然,加上拉排阻也没有影响。

需要注。

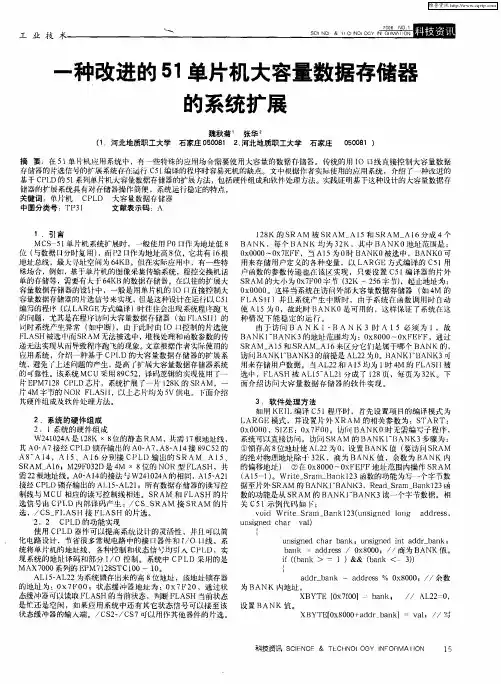

郑州航空工业管理学院《单片机原理与应用》课程设计说明书10 级自动化专业 1006112 班级题目51单片机大容量数据存储器的系统扩展姓名杨向龙学号100611234指导教师王义琴职称讲师二О一三年六月十日目录一、51单片机大容量数据存储器的系统扩展的基本原理 (4)二、设计方案 (4)三、硬件的设计 (5)3.1 系统的硬件构成及功能 (5)3.2硬件的系统组成 (5)3.2.1、W241024A (5)3.2.2、CPLD的功能实现 (5)3.2.3、AT89C52简介 (6)3.2.4、SRAM的功能及其实现 (9)3.3、基本单片机系统大容量数据存储器系统扩展 (9)五、结论 (13)六、参考资料 (13)51单片机大容量数据存储器的系统扩展摘要:在单片机构成的实际测控系统中,仅靠单片机内部资源是不行的,单片机的最小系统也常常不能满足要求,因此,在单片机应用系统硬件设计中首先要解决系统扩展问题。

51单片机有很强的外部扩功能, 传统的用IO口线直接控制大容量数据存储器的片选信号的扩展系统存在运行C51编译的程序时容易死机的缺点。

文中介绍了一种改进的基于CPLD的51系列单片机大容量数据存储器的扩展方法,包括硬件组成和软件处理方法。

关键字:W241024A、CPLD、AT89C52、SRAM一、51单片机大容量数据存储器的系统扩展的基本原理MCS-51 单片机系统扩展时,一般使用P0 口作为地址低8位(与数据口分时复用),而P2口作为地址高8位,它共有16根地址总线,最大寻址空间为64KB。

但在实际应用中,有一些特殊场合,例如,基于单片机的图像采集传输系统,程控交换机话单的存储等,需要有大于64KB 的数据存储器。

二、设计方案在以往的扩展大容量数据存储器的设计中,一般是用单片机的IO口直接控制大容量数据存储器的片选信号来实现,但是这种设计在运行以C51编写的程序(以LARGE 方式编译)时往往会出现系统程序跑飞的问题,尤其是在程序访问大容量数据存储器(如FLASH)的同时系统产生异常(如中断),由于此时由IO 口控制的片选使FLASH 被选中而SRAM 无法被选中,堆栈处理和函数参数的传递无法实现从而导致程序跑飞的现象。

文章介绍一种基于CPLD 的大容量数据存储器的扩展系统,避免了上述问题的产生,提高了扩展大容量数据存储器系统的可靠性。

该系统MCU 采用89C52,译码逻辑的实现使用了一片EPM7128 CPLD 芯片,系统扩展了一片128K 的SRAM,一片4M 字节的NOR FLASH,以上芯片均为5V 供电。

第三节硬件设计3.1 系统的硬件构成及功能W241024A是128K ×8 位的静态RAM,共需17 根地址线,其A0~A7 接经CPLD 锁存输出的A0~A7,A8~A14 接89C52 的A 8 ~ A 1 4 ,A 1 5 、A 1 6 分别接C P L D 输出的S R A M _ A 1 5 、SRAM_A16;M29F032D是4M ×8 位的NOR 型FLASH,共需22 根地址线。

A0~A14 的接法与W241024A 的相同,A15~A21接经CPLD 锁存输出AL15~AL21;所有数据存储器的读写控制线与M C U 相应的读写控制线相连。

S R A M 和F L A S H 的片选信号由C P L D 内部译码产生:/ C S _ S R A M 接S R A M 的片选,/ C S _ F L A S H 接F L A S H 的片选。

3.2硬件的系统组成3.2.1、W241024AW 2 4 1 0 2 4 A 是1 2 8 K x 8 位的静态R A M,共需1 7 根地址线,其A O - A 7 接经 C P L D 锁存输出的 A O - A 7 , A 8 - A 1 4 接8 9 C 5 2 的A 8 - A 1 4 , A 1 5 , A 1 6 分别接C P L D输出的S R A M- A 1 5 , SRAM-A16; M 2 9 F O 3 2 D 是4 M x 8 位的N O R型F L A S H ,共需2 2 根地址线。

A O - A 1 4 的接法与W 2 4 1 0 2 4 A 的相同,A 1 5 - A 2 1接经 C P L D 锁存输出的A L 1 5 - A L 2 1 ; 所有数据存储器的读写控制线与M C U相应的读写控制线相连。

S R A M 和 F L A S H的片选信号由 C P L D内部译码产生: / C S - S R A M 接S R A M 的片选,/ C S - F L A S H接 F L A S H的片选。

3.2.2、CPLD的功能实现CPLD就是复杂可编程逻辑器件复杂可编程逻辑器件(CPLD)。

CPLD提供了非常好的可预测性,因此对于关键的控制应用非常理想。

CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。

其中MC 结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。

由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

使用CPLD 器件可以提高系统设计的灵活性,并且可以简化电路设计,节省很多常规电路中的接口器件和I/O 口线。

系统将单片机的地址线、各种控制和状态信号均引入CPLD,实现系统的地址译码和部分I/O 控制。

系统中C P L D 采用的是MAX7000 系列的EPM7128STC100 -10。

AL15~AL22 为系统锁存出来的高8 位地址,该地址锁存器的地址为:0x7F00;状态缓冲器地址为:0x7F20,通过状态缓冲器可以读取FLASH 的当前状态,判断FLASH 当前状态是忙还是空闲,如果应用系统中还有其它状态信号可以接至该状态缓冲器的输入端。

/CS2~/CS7 可以用作其他器件的片选。

3.2.3、AT89C52简介89C52是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含8Kbytes的可反复擦写的只读程序存储器和256byte的随机数据存储器,器件采用ATMEL公司高密度\非易失性存储技术生产,与标准的51指令系统以8052产品引脚兼容,片内置通用8位中央处理器和FLASH存储单元,功能强大89C52单片机适合于许多较为复杂控制应用场合.主要性能参数:.与MCS-51产品指令和引脚完全兼容.8K字节可重擦写FLASH闪速存储器.1000次擦写周期.全静态操作:0Hz-24 Hz.三级加密程序存储器.256*8字节内部RAM .32个可编程I/O口线.3个16位定时/计数器.8个中断源.可编程串行UART通道.低功耗空闲和掉电模式功能特性概述:AT89C52提供以下标准功能:8K字节FLASH闪存存储器,256字节内部RAM,32个I/O口线,3个16位定时/计数器,一个6向量两极中断结构,一个全双工串行通信口,片内振荡器及时钟电路.同时,AT89C52可降至0 Hz的静态逻辑操作,并支持两种软件可选的节电工作模式:空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

引脚功能说明.vcc:电源电压.GND:地.P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式8个TTL逻辑门电路,对端口P0写“1”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据复用,在访问期间激活内部上拉电阻。

在FLASH编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

.P1口:P1是一个带内部上拉电阻的8位双向I/O口,P1的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。

对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。

作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时输出一个电流。

.P2口:P2是一个带有内部上拉电阻的双向I/O口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。

对端口P2写“1”,通过内部的上拉电阻把端口拉倒高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流。

在访问外部程序存储器或16位地址的外部数据存储器时,P2口送出高8位地址数据。

在访问8位地址的外部数据存储器时,P2口输出P2锁存器的内容。

FLASH编程或校验时,P2亦接收高位地址和一些控制信号。

.P3口:P3口是一组带有内部上拉电阻的双向8位I/O。

P3口输出缓冲级可驱动4个TTL逻辑门电路。

对P3口写“1”时,它们被内部上拉电阻拉高并可作为输入端口。

此时,被外部拉低的P3口将用上拉电阻输出电流。

P3口除了作为一般的I/O线外,更重要的用途是它的第二功能端口引脚第二功能P3.0 RXD(串行输入口)P3.1 TXD(串行口输出口)P3.2 INT0 (外中断0)P3.3 INT1(外中断1)P3.4 T0(定时/计数器0)P3.5 T1(定时/计数器1)P3.6 WR(外部数据存储器写选通)P3.7 RD(外部数据存储器选通).RST:复位输入,当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位。

.ALE/PROG:当访问外部程序存储器或数据存储器时,ALE输出脉冲用于所村地址的8位字节。

一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外时钟或用于定时目的。

要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。

.PSEN:程序储存允许输出是外部程序存储器的读选通信号,当AT89C52由外部程序存储器取指令时,每个机器周期两次有效,即输出两个脉冲。

在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

.EA/VPP外部访问允许。

欲使CPU仅访问外部程序存储器,EA端必须保持低电平。

.XTAL1:振荡器反向放大的及时内部时钟发生器的输入端。

.XTAL2:振荡器反向放大的输出端。

.特殊功能寄存器:在AT89C52片内存储器中,80H-FFH共128个单元为特殊功能寄存器。

AT89C52除了与AT89C51所有的定时/计数器和定时/计数器外,还增加了一个定时/计数器2。

定时/计数器2的控制和状态位位于T2CON T2MOD,寄存器对是定时器2在16位捕捉或16位自动重装方式下捕捉/自动重装载寄存器。