80C51单片机存储器的扩展

- 格式:doc

- 大小:44.50 KB

- 文档页数:5

80C51单片机的并行端口结构80C51共有4个8位的并行I/O口,分别记作P0、P1、P2、P3。

被归入专用寄存器。

I/O端口有串行和并行之分,串行I/O端口一次只能传送一位二进制信息,并行I/O端口一次能传送一组二进制信息。

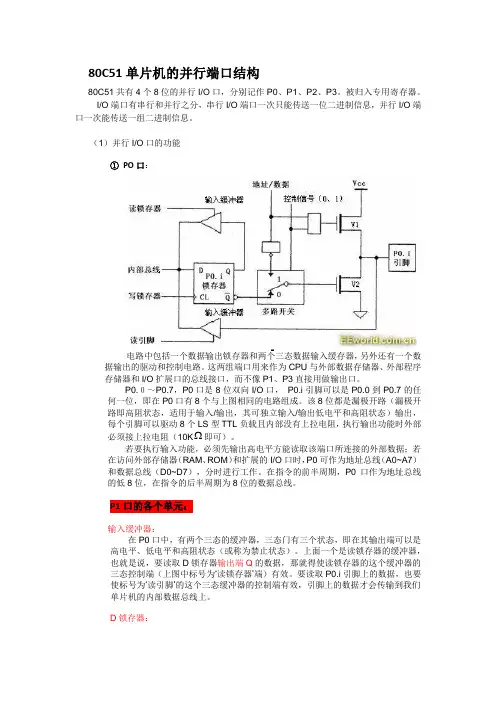

(1)并行I/O口的功能①PO口:电路中包括一个数据输出锁存器和两个三态数据输入缓存器,另外还有一个数据输出的驱动和控制电路。

这两组端口用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口的总线接口,而不像P1、P3直接用做输出口。

P0.0~P0.7,P0口是8位双向I/O口,P0.i引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

该8位都是漏极开路(漏极开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态)输出,每个引脚可以驱动8个LS型TTL负载且内部没有上拉电阻,执行输出功能时外部必须接上拉电阻(10K 即可)。

若要执行输入功能,必须先输出高电平方能读取该端口所连接的外部数据;若在访问外部存储器(RAM、ROM)和扩展的I/O口时,P0可作为地址总线(A0~A7)和数据总线(D0~D7),分时进行工作。

在指令的前半周期,P0口作为地址总线的低8位,在指令的后半周期为8位的数据总线。

P1口的各个单元:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其输出端可以是高电平、低电平和高阻状态(或称为禁止状态)。

上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

要读取P0.i引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:存储器中可以存放电荷,加一个小的存储器的单元,并在它的面前加一个开关,要让这一位输出时,就把开关打开,信号就进入存储器的单元,然后马上关闭开关,这一位的状态就被保存下来,直到下一次命令让它把开关再打开为止,这就是锁存器。

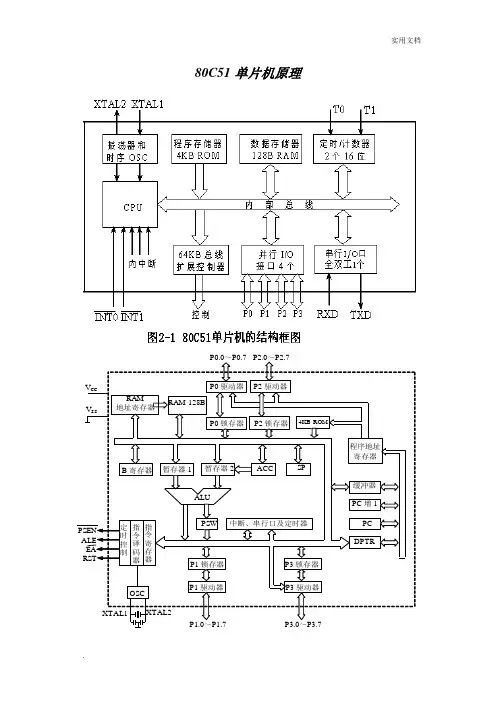

80C51单片机原理RAM地址寄存器 RAM 128B 程序地址寄存器P0驱动器 P2锁存器 P2驱动器P1锁存器 暂存器2 B 寄存器 4KB ROM暂存器1ACC SP P0锁存器 PC PC 增1 缓冲器 P3锁存器 OSC中断、串行口及定时器PSW ALU DPTRP1驱动器 P3驱动器XTAL1XTAL2 P0.0~P0.7 P2.0~P2.7 P3.0~P3.7 P1.0~P1.7 RST ALEV CCV SS定时控制 指令译码器 指令寄存器 PSEN EA表2-1 P3口各引脚与第二功能表PSW 的各位定义见表80C51 P0~P3接口功能简见大多数口线都有双重功能,介绍如下: 1、P0口具有双重功能:(1) 作为通用I/O ,外接I/O 设备。

(2) 作为地址/数据总线。

在有片外扩展存储器的系统 中,低8位地址和数据由P0口分时传送。

PSW 位地址 PS W.7PSW .6PSW .5 PSW .4 PSW .3 PSW .2 PSW .1 PSW .0 位标志CY ACF0RS1RS0OVF1P2、P1口是唯一的单功能口:作为输入/输出口,P1口的每一位都可作为输入/输出口。

3、P2口具有双重功能:(1)作为输入/输出口。

(2)作为高8位地址总线。

在有片外扩展存储器的系统中,高8位地址由P2口传送。

4、P3口具有双重功能:(1)作第一功能使用时,其功能为输入/输出口。

(2)作第二功能使用时,每一位功能定义如表2.1所示。

80C51单片机的4个I/O口都是8位双向口,这些口在结构和特性上是基本相同的,但又各具特点,以下将分别介绍之。

图2-9 P0口某位的结构图2-10 P1口某位的结构图2-11 P2口某位的结构图2-12 P3口某位的结构P0~P3口使用时应注意事项1、如果80C51单片机内部程序存贮器ROM够用,不需要扩展外部存贮器和I/O接口,80C51的四个口均可作I/O口使用。

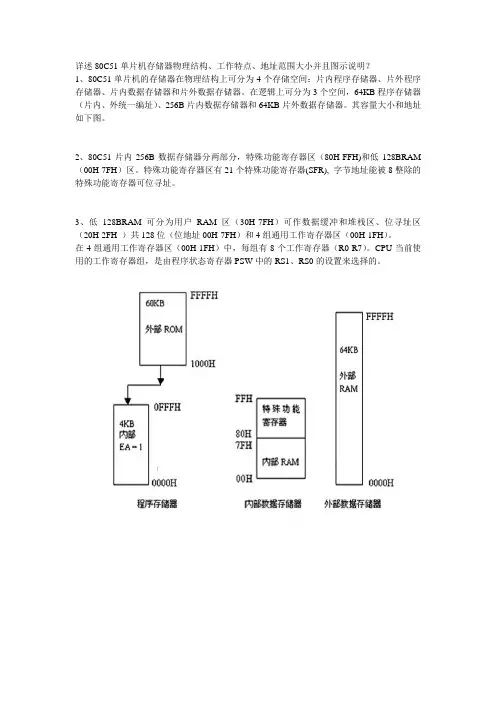

详述80C51单片机存储器物理结构、工作特点、地址范围大小并且图示说明?

1、80C51单片机的存储器在物理结构上可分为4个存储空间:片内程序存储器、片外程序存储器、片内数据存储器和片外数据存储器。

在逻辑上可分为3个空间,64KB程序存储器(片内、外统一编址)、256B片内数据存储器和64KB片外数据存储器。

其容量大小和地址如下图。

2、80C51片内256B数据存储器分两部分,特殊功能寄存器区(80H-FFH)和低128BRAM (00H-7FH)区。

特殊功能寄存器区有21个特殊功能寄存器(SFR),字节地址能被8整除的特殊功能寄存器可位寻址。

3、低128BRAM可分为用户RAM区(30H-7FH)可作数据缓冲和堆栈区、位寻址区(20H-2FH )共128位(位地址00H-7FH)和4组通用工作寄存器区(00H-1FH)。

在4组通用工作寄存器区(00H-1FH)中,每组有8个工作寄存器(R0-R7)。

CPU当前使用的工作寄存器组,是由程序状态寄存器PSW中的RS1、RS0的设置来选择的。

接口技术课程设计说明书设计题目80C51单片机存储器的扩展指导教师:设计者:系别:班级:学号:机械工程学院班学生课程设计题目:80C51单片机存储器的扩展一、课程设计工作日自年月日至年月日二、同组学生:三、课程设计任务要求(包括课题来源、类型、目的和意义、基本要求、完成时间、主要参考资料等)1、目的及意义(1)巩固及深化《单片机原理及应用》课程的理论知识,培养,分析,解决实际问题的能力。

(2)掌握80C51系统的总线构成,能根据题目要求确定设计思路、绘制所需的硬件电路图。

2、主要内容用两片Intel2732为80C51单片机扩展一个8KB的外部程序存储器,要求使用73LS138译码器,地址范围为B000H~CFFFH,请连线并写明扩展步骤。

3、基本要求(1)熟悉各芯片的使用方法和注意事项。

(2)绘制电路原理图(3)答辩4、主要参考资料单片机基础及应用,赵巍,冯娜,马苏常,刘玉山等,清华大学出版社,2009年指导教师签字:教研室主任签字:分析题目:根据题意知用2片Intel2732给80C51单片机扩展8KB的外程序存储器,分配的地址范围为B000H~CFFFH,分别采用线选法和译码法。

2732以HMOS-E(高速NMOS硅栅)工艺制成,24脚双列直插式,为4KB容量,地址线12条A0~A11;,数据线8条D0~D7,远为片选端,低电平有效,OE/VPP是输出允许信号,低电平有效,该引脚在编程时也作为编程电压VPP的输入端。

VCC为十5V电源,GND 为地。

(参考《微型计算机原理及应用》)由于80C51单片机对外没有专用的地址总线(AB),数据总线(DB)和控制总线(CB),那么在进行系统扩展时,首先需要扩展系统的三总线。

1地址总线:(address bus AB)(《参考单片机基础及应用》P81)1)AB的特点地址总线用来传递地址信号,用于外扩展储存单元和I/O端口地址。

地址总线总是单向的,因为地址信号只能从单片机向外传送。

80c51内部RAM空间分配keil编译的时候,在开始时候会清零所有内存.在main之前,所以,只要复位, 内存肯定是0MCS-51单片机的内部数据存储器在物理上和逻辑上都分为两个地址空间,即:数据存储器空间(低128单元),用户可用的;特殊功能寄存器空间(高128单元);这两个空间是相连的,从用户角度而言,低128单元才是真正的数据存储器。

下面我们就来详细的与大家讲解一下:低128单元:片内数据存储器为8位地址,所以最大可寻址的范围为256个单元地址,对片外数据存储器采用间接寻址方式,R0、R1和DPTR都可以做为间接寻址寄存器,R0、R1是8位的寄存器,即R0、R1的寻址范围最大为256个单元,而DPTR是16位地址指针,寻址范围就可达到64KB。

也就是说在寻址片外数据存储器时,寻址范围超过了256B,就不能用R0、R1做为间接寻址寄存器,而必须用DPTR寄存器做为间接寻址寄存器。

1、通用寄存器区(00H-1FH)在00H1FH共32个单元中被均匀地分为四块,每块包含八个8位寄存器,均以R0R7来命名,我们常称这些寄存器为通用寄存器。

这四块中的寄存器都称为R0R7,那么在程序中怎么区分和使用它们呢?聪明的INTEL工程师们又安排了一个寄存器程序状态字寄存器(PSW)来管理它们,CPU只要定义这个寄存的PSW的D3和D4位(RS0和RS1),即可选中这四组通用寄存器。

程序中并不需要用4组,那么其余的可用做一般的数据缓冲器,CPU在复位后,选中第0组工作寄存器。

2、位寻址区(20H-2FH)片内RAM的20H2FH单元为位寻址区,既可作单元用字节寻址,也可对它们的位进行寻址。

位寻址区共有16 个字节,128个位,位地址为00H7FH。

CPU能直接寻址这些位,执行例如置1、清0、求反、转移,传送和逻辑等操作。

我们常称MCS-51具有布尔处理功能,布尔处理的存储空间指的就是这些为寻址区。

3、用户RAM区(30H-。

程设计任务书

机械工程学院学院机制1211 班学生张会利-39号

课程设计题目:

单片ROM扩展

一、课程设计工作日自 2015 年 1 月 19 日至 2015 年 2 月 23 日

二、同组学生:张会利

三、课程设计任务要求(包括课题来源、类型、目的和意义、基本要求、完成时间、主要参考资

料等):

1、目的及意义

(1)巩固和深化《单片机原理及应用》课程的理论知识,培养,分析、解决实际问题的能力。

(2)掌握单片机基本运用技术及汇编语言的基本方法,能根据题目要求确定设计思路、绘制流程图、编制并调试汇编语言程序,得出结果。

2、主要内容

用一片Intel2732为80C51单片机扩展一个4KB的外部程序存储器,要求使用73LS138译码器,地址范围为A000H~AFFFH。

请连线并写明扩展步骤。

3、基本要求

(1)分析题目,写出详细分析过程。

(2)绘制工作流程图。

(3)编制程序,画出硬件线路图。

(4)上机调试程序,运行结果。

(5)编写设计说明书,包括1—4个步骤的内容。

(6)答辩。

4、主要参考资料

单片机基础及应用,赵巍,冯娜,马苏常,刘玉山等,清华大学出版社,2009年指导教师签字:教研室主任签字:

程序设计说明书

(一)芯片简介

1.2732简介:

2732是容量为4k×8位(4KB)。

采用单一+5V供电,最大静态工作电流100mA, 电流35mA出时间最大为250ns. 2732的封装形式为DIP24,管脚如图所示。

●A0~A11 :12条地址线,表示有212个地址单元

●O0~O7 :8条数据线,表示地址单元字长8位

●CE :片选控制输入端,低电平有效

●OE/Vpp :双功能管脚,低电平时,允许2732输出数据

●Vcc :工作电平+5V

●GND :芯片接地端

2.74LS373简介:

74LS373是带三态缓冲输出的8D锁存器,由于单片机的三片总线结构中,数据线与地址线的低8位公用P0口,因此必须用地址所存器将地址信号和数据信号区分开。

74L373的锁存控制端G直接与单片机的锁存控制信号和数据信号ALE相连,在AEL的下降沿锁存低8位地址。

3.74LS138简介:

74LS138有3个“选择输入端”C.B.A.它可以选择8个输出线Y0—Y7,当C.B.A 的信号组合选择到某个输出线时,这个输出线有效,即输出为低电平,74LS138还有3个“使能输入端”(又称为“允许端或控制端”)G1. G2A.G2B, 当其有效时,即G1。

G2A=0. G2B=0时译码器才能工作。

(二)程序说明

1)芯片的选择及确定片数

根据题目容量要求扩展4KB的外部程序存储器。

选择一片Intel2732芯片。

74LS138译码器。

2)分配地址范围。

采用一片2732芯片扩展80C51的片外程序存储空间,分配的地址范围为A000H~AFFFH,如表1表示采用完全译码芯片选择。

即所在地址线全部连接,所以每一个单元只占用唯一一个地址,不存在地址重复问题。

3)连线说明如下:

(1)地址线:单片机扩展片外存储器时,按照分配地址范围连线图所示:地址是由P0和P2口提供的,2732的12条地址线(A0—A11)中。

低八位A0~A7通过所存器74LS373与P0口连接,高4位A8—A11直接与P2.0—P2.3连接,P2口本身有所存功能。

注意,锁存器的所存使能端G必须和单片机的ALE管脚相连。

(2)数据线:2732的8位数据线直接与单片机的P0口相连,因此,P0口使一个分时复用的地址数据线。

(3)控制线:CPU执行2732中存放的程序指令时,取指令阶段就是对2732进行操作。

注意,CPU对EPROM只能进行读操作,不能进行写操作。

CPU对2732的读操作控制都是通过控制线实现的。

2732控制线的连接有以下几条:

CE:Intel2732的片选信号由3-8译码器产生,

OE:接80C51的读选通信号PSEN端,在访问片外程序存储器时,只要PSEN 端出现负脉冲,即可从2732中读出程序。

2732的片选信号由3—8译码器产生。

80C51的P2口的高四位线与3-8译码器片选端连线如下:

P2.7:G1

P2.6:A P2.5:B P2.4:C

Y2:2732的CE

3/8译码器的功能真值表。

G1=1 G2A=0 G2B=0,当选中,P2.4=0 P2.5=1 P2.6=0 P2.7=1时,符合所分配的地址范围。

注意,80C51中在扩展并使用外部程序存储器时,必须使EA接地。

(4)存储器扩展连接图如图所示:

两片2732的扩展连接图

一片2732扩展后地址范围

外部程序存储器扩展小结

通过一周的程序设计的练习,我们巩固和深化《单片机原理及应用》课程的理论知识,分析,解决实际问题的能力。

初步掌握了外部程序扩展设计的思路和方法,了解了73LS138译码器和2732锁存器的使用,掌握了如何设计电路原理图,最重要是提高了我们的动手操作能力。