基于Cadence的IC设计

- 格式:pdf

- 大小:4.97 MB

- 文档页数:252

cmos模拟集成电路设计与仿真实例——基于cadence ic617CMOS(互补金属氧化物半导体)模拟集成电路是现代电子设备中常见的一种设计和制造技术。

在本文中,我们将介绍基于Cadence IC617的CMOS模拟集成电路设计和仿真实例,以便读者了解CMOS电路设计的基本流程和重要步骤。

步骤1:设计电路首先,我们需要确定所设计的电路的功能和性能指标。

例如,我们可以设计一个运算放大器电路来放大输入的电压信号。

然后,我们可以使用Cadence IC617中的设计工具创建原始的电路图。

在Cadence IC617中,我们可以选择所需的电路元件,如MOS管、电容器和电阻器,并将它们放置在电路图中。

然后,我们可以将它们连接起来,以实现所需的电路功能。

在设计电路时,我们需要注意元件的尺寸和位置,以及电路的布局,以确保性能和可靠性。

步骤2:参数化模型完成电路设计后,接下来我们需要为每个元件选择适当的参数化模型。

这些模型是描述元件行为和特性的数学表达式。

例如,我们可以选择MOS管的Spice模型,该模型可以描述其转导和容性特性。

在Cadence IC617中,我们可以通过浏览模型库,选择适合我们电路的元件模型。

然后,我们可以将这些模型与电路元件关联起来,以便在仿真过程中使用。

步骤3:电路布局完成参数化模型的选择后,我们需要进行电路布局。

电路布局是将电路元件实际放置在芯片上的过程。

在Cadence IC617中,我们可以使用布局工具来配置电路元件的位置和尺寸。

在电路布局过程中,我们需要考虑元件之间的互连和布线。

我们可以使用布线工具来连接元件的引脚,并确保布线符合规定的电气规范。

同时,我们还需要遵循布线规则,以确保信号传输的稳定性和可靠性。

步骤4:参数抽取和后仿真完成电路布局后,我们可以进行参数抽取和后仿真。

参数抽取是从电路布局中提取出元件的真实特性和物理参数的过程。

在Cadence IC617中,我们可以使用抽取工具来自动提取电路布局中各个元件的参数。

cadence教程-IC设计工具原理共页课件 (一) CADENCE教程-IC设计工具原理共页课件作为一名IC设计工程师,必须要掌握各种IC设计工具。

Cadence是业内最受欢迎的EDA(电子设计自动化)软件之一,广泛应用于IC和系统级芯片设计。

这篇文章将介绍Cadence教程——IC设计工具原理共页课件,帮助初学者更好地了解这款软件。

一、课程内容该课程共分为六个部分,从IC设计的基础知识开始,逐步深入讲解Cadence软件的使用和原理。

1. IC设计的基础知识该部分主要介绍集成电路的概念、IC设计的基本流程、ASIC和FPGA的区别等内容,帮助学习者更好地了解IC设计的基本知识。

2. Cadence软件的安装和配置该部分教授如何安装、配置Cadence软件,学习者将了解如何正确设置工作目录、环境变量等,以便进行后续的IC设计工作。

3. Cadence软件的基本流程该部分主要介绍Cadence软件的基本使用流程,包括创建项目、编辑电路图、绘制版图、进行仿真等,重要的是学习者将学会如何创建一个完整的设计流程。

4. Cadence软件的高级应用该部分讲解Cadence软件的高级应用,包括使用脚本自动化设计、使用Verilog语言、进行DC分析、进行静态时序分析等内容,让学习者掌握Cadence软件更加深入的应用。

5. Cadence软件的Debug该部分介绍如何使用Cadence软件进行Debug,掌握Debug技巧,帮助学习者快速找到设计中的问题,并进行修复。

6. 基于Cadence软件的实际设计案例该部分介绍基于Cadence软件的实际设计案例,包括ADC设计、FPGA 设计等,帮助学习者更好地理解设计流程,并将所学知识应用到实践中。

通过以上六个部分,这个Cadence课程全面系统的讲解了IC设计软件工具的使用和原理共页,让学习者更好地了解Cadence软件和IC设计的概念和方法。

二、课程特点1.操作实战:一步步教大家如何使用Cadence软件,操作更为透彻,方便学生理解。

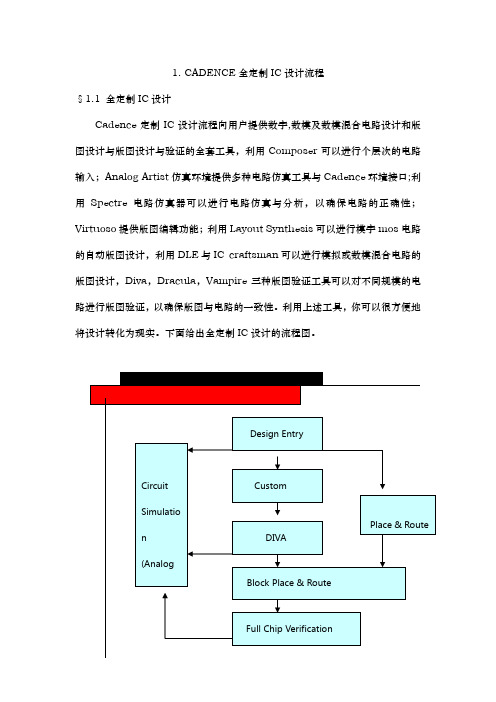

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示: 图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

cadence教程-IC设计工具原理共页课件 (二) - Cadence教程-IC设计工具原理共页课件

1. 什么是Cadence?

Cadence是一家专门从事电子设计自动化软件的公司。

其产品涵盖了芯片设计、系统设计、封装设计和PCB设计等领域。

Cadence的软件被广泛应用于半导体、通信、计算机、消费电子等行业。

2. Cadence的主要产品

Cadence的主要产品包括Virtuoso、Allegro、OrCAD、Sigrity等。

其中,Virtuoso是一款用于模拟、布局和验证芯片的工具;Allegro是

一款用于PCB设计的工具;OrCAD是一款用于电路设计的工具;

Sigrity则是一款用于信号完整性分析的工具。

3. Cadence的应用领域

Cadence的软件被广泛应用于各种电子产品的设计和制造中,如手机、平板电脑、笔记本电脑、服务器、网络设备、汽车电子、医疗设备等。

在半导体行业中,Cadence的软件被用于设计各种芯片,如处理器、存储器、模拟集成电路、射频集成电路等。

4. Cadence的优势

Cadence的软件具有高度的可靠性、灵活性和易用性。

其产品支持多种操作系统,如Windows、Linux、Solaris等。

此外,Cadence还提供了丰富的教程和技术支持,帮助用户更好地使用其软件。

5. Cadence的未来发展

随着电子行业的不断发展,Cadence的软件也在不断升级和改进。

未来,Cadence将继续加强与各大芯片厂商和设备厂商的合作,开发出更加先进和适用的软件,为电子行业的发展做出更大的贡献。

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso 提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE的使用说明Cadence cdsSPICE 也是众多使用SPICE内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb调出Cadence 软件。

出现的主窗口如图2-1-1所示:图 2-1-1Candence主窗口二.在PC机上使用1)将PC机的颜色属性改为256色(这一步必须);2)打开Exceed软件,一般选用xstart软件,以下是使用步骤:start method选择REXEC(TCP-IP),Programm选择Xwindow。

Host选择10.13.71.32 或10.13.71.33。

host type选择sun。

并点击后面的按钮,在弹出菜单中选择command tool。

cmos模拟集成电路设计与仿真实例——基于cadence ic617现如今,随着电子技术的快速发展,集成电路逐渐成为了现代电子产品的核心组成部分。

而在集成电路设计与制造的过程中,模拟集成电路设计显得尤为重要。

CMOS模拟集成电路设计与仿真是其中的重要环节,它是指利用CMOS技术设计和实现各种类型的模拟电路,通过仿真验证电路的性能和可靠性。

在CMOS模拟集成电路设计中,Cadence IC617是一个常用的设计工具。

它提供了一整套完善的设计和仿真环境,可以帮助工程师们高效地进行电路设计和验证。

下面,我们将以基于Cadence IC617的CMOS模拟集成电路设计与仿真为例,详细介绍该过程的步骤和要点。

首先,进行CMOS模拟集成电路设计时,我们需要明确电路的功能和性能要求。

比如,我们可以设计一个放大电路,要求其具有特定的增益和带宽。

或者设计一个滤波电路,要求其具有特定的截止频率和衰减特性。

这些要求将直接影响后续的电路设计和参数选择。

接下来,我们需要进行电路的整体结构设计。

在整体结构设计中,我们需要选择电路的拓扑结构和元件的类型。

对于CMOS模拟集成电路来说,常见的拓扑结构包括共源共栅放大器、共源共漏放大器、共射放大器等。

而元件的类型包括MOS管、电容、电阻等。

通过合理选择和组合这些结构和元件,可以实现所需的电路功能。

接下来,我们需要进行电路的详细设计和参数选择。

在详细设计中,我们需要确定电路的工作点和元件的尺寸。

工作点的选择与电路的静态特性密切相关,而元件的尺寸则决定了电路的动态特性和性能。

在参数选择时,我们需要考虑电路的可靠性和稳定性,而且要与实际的工艺条件相匹配。

完成电路的详细设计后,我们需要进行电路的仿真验证。

在仿真验证中,我们可以使用Cadence IC617提供的仿真工具,对电路进行各种测试和分析。

比如,我们可以使用直流分析进行电路的静态特性分析,使用交流分析进行电路的频率响应分析,使用蒙特卡洛分析进行电路的可靠性分析等。

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso 提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示:图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

第1章 Cadence IC 5.1.41的基本设置本章是Cadence IC 5.1.41是设计的简明入门教程,目的是让读者在刚接触该软件的时候对它的基本功能有一个总体的了解。

本章主要内容如下:[1] 启动Cadence IC前的准备;[2] Command Interpreter Window (CIW, 命令行窗口);[3] Library Manager 设计库管理器;[4] Virtuoso® Schematic Editor电路图编辑器简介;[5] Virtuoso® Analog Design Environment (ADE) 简介。

1.1启动前的准备要在Unix/Linux使用Cadence IC 5.1.41工具应当保证以下的条件:[1] 保证Cadence IC 5.1.41已经由管理员正确地安装在电脑上;并且软件授权密钥已经设置完成。

[2] 在Shell中设置了正确的环境变量。

必须将Cadence IC的安装路径加入Shell环境变量,Cadence IC 5.1.41才能正常运行。

以Cshell 为例,Cadence IC被安装在了/tools/cadence/ic5141,则需要在~/.cshrc文件中加入这样的路径配置语句:setenv ic50 /tools/cadence/ic5141set LD_LIBRARY_PATH=($ic50/tools/lib $ic50/tools/dfII/lib $ic50/tools/tcltk/ tcl8.0/lib $LD_LIBRARY_PATH)set path = ($ic50/tools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path)也可以把路径的设置写在一个单独的配置文件中。

例如,将上面的配置写在配置文件/env/cadence_5141中,则可以在~/.cshrc中加入一行source /env/cadence_51411.1.1启动配置文件:.cdsinit.cdsinit文件是在Cadence IC中启动时运行的SKILL脚本文件。

该文件配置了很多Cadence IC 5.1.41的环境配置,包括使用的文本编辑器、热键设置、仿真器的默认配置等。

如果Cadence IC没有找到.cdsinit文件,软件中的快捷键等功能都不能适用。

Cadence IC搜索.cdsinit文件时,首先会搜索程序的启动路径,然后搜索的是用户的主目录。

例如:在~/project目录下运行icfb&,则首先Cadence IC会尝试载入~/project/.cdsinit。

如果这个文件不存在则会尝试载入~/.cdsinit。

默认配置文件路径:<Cadence工具目录>/tools/dfII/samples/local/cdsinit1.1.2其他配置文件如果需要,在程序的运行目录建立其他的启动配置文件,如.cdsenv、.cdsplotinit、display.drf等。

这些配置文件分别有自己的用途:.cdsenv: 用于设置启动时的环境变量;.cdsplotinit: Cadence IC打印和输出图型的设置;display.drf: 版图编辑器中显示颜色等的配置;这些配置文件的搜索路径首先是程序启动目录。

其次是用户的主目录。

这些配置文件的样本位置如下:.cdsenv: <Cadence 安装目录>/tools/dfII/samples/.cdsenv.cdsplotint: <Cadence 安装目录>/tools/plot/samples/cdsplotinit.sampledisplay.drf: <Cadence 安装目录>/share/cdssetup/dfII/default.drf1.1.3 设置设计库配置文件:cds.lib设计库(library)配置文件放置在Cadence IC程序的运行路径下,比如要在~/project目录下运行Cadence IC,则需要在该目录下建立cds.lib文件。

这个文件设置的是Cadence IC中的设计库的路径。

常用命令格式:z DEFINE格式:DEFINE <库名> <库路径>z INCLUDE格式:INCLUDE <另外一个cds.lib的全路径>z#行注释符,在行首加入则该行无效。

如果cds.lib文件是空文件,则Cadence IC的设计库中就会是空的。

为了添加基本元件库,需要一些基本元件。

可以在cds.lib文件中加入一行:INCLUDE <Cadence安装目录>/share/cdssetup/cds.lib1.2命令行窗口(Command Interpreter Window,CIW)完成上述设置之后,就可以在命令行下运行Cadence IC5.1.41软件:icfb &Cadence IC的命令行窗口(又称为命令解释器,Command Interpreter Window, CIW)就会出现:图1.1 命令行窗口(CIW)该窗口包括几个部分:菜单栏、输出窗口、命令行、鼠标命令、提示1.2.1 命令行窗口(CIW)菜单CIW菜单展开包含以下选项,下面将介绍其中比较重要的一些选项:图1.2 CIW菜单展开内容z FileÆNew建立新的设计库(Design Library)或者设计的CellView;z FileÆimport导入,可以导入的信息包括gds版图、电路图、cdl网表、模型库甚至verilog代码等。

z FileÆOpen打开“Cell”的“View”,根据不同的“View”的类型,Cadence将选择适当的编辑器:例如,如果一个“View”是一个符号(symbol)则Cadence将选择Virtuoso Symbol Editor打开;如果是一个电路图(schematic)则Cadence会选择Virtuoso Schematic Editor来打开;如果是一个版图(layout)则会用Virtuoso Layout Editor打开;如果是Verilog或Verilog A代码则会用文本编辑器打开。

z FileÆExport导出文件。

同样,可以将Cadence设计库导出成各种文件类型。

z FileÆExit退出icfb工作环境。

z ToolsÆLibrary Manager很实用的图形化设计库浏览器,界面如图1.3所示。

后面将详细介绍其中的内容。

图1.3 “Library Manager”界面z ToolsÆLibrary Path Editor图1.4“Library Path Editor”界面这是一个用来修改设计库配置文件(cds.lib)的图形化界面,如图1.4所示。

在这个界面中可以直观地对cds.lib文件进行修改和添加。

z ToolsÆVerilog Integration里面有2个选项分别是Verilog-XL和NC-Verilog,是两种Verilog仿真环境,用于对混合信号电路和数字电路的仿真。

z ToolsÆAnalog Environment该子菜单用于模拟电路仿真,里面的选项包括:Simulation: 打开Virtuoso® Analog Design Environment (ADE)图1.5 “Analog Environment”界面Calculator:用于对仿真结果进行进一步计算的计算器工具Result Browser: 仿真结果浏览器Waveform: 仿真结果绘图程序。

这些工具的使用将在各个章节中介绍。

z ToolsÆTechnology File Manager用于管理设计库和模型库之间的对应关系设置。

图1.6“Technology File Manager”界面z Options该菜单内的选项主要用于配置icfb的环境并保存/载入需要的配置。

该菜单中还提供了用于管理产品秘钥的工具。

1.2.2 CIW中的其他部分输出窗口,如图1.7所示。

主要显示一些操作的输出信息和提示,包括一些状态信息和警告信息、错误提示。

这些提示有助于分析操作中的问题。

命令行:在这一栏中可以运行SKILL语言的命令,利用命令可以对界面上的任何项目进行控制,从电路编辑到仿真过程,都可以用SKILL语言控制。

图1.7 CIW中的输出窗口与命令行CIW中的输出窗口和命令行和在一起实际上就是一个命令界面。

命令语言是SKILL语言。

图形界面只是在命令行基础上的扩展。

在图形界面上的任何操作或者快捷键都是通过命令行来最终实现的。

因而理论上用命令行可以完成一切操作,当然能实际应用中这样做并不方便。

命令行的好处是可以采用语言控制复杂的操作,并且可以进行二次开发,将命令与界面整合起来。

这样就提高了整个软件的可扩展性和易用性,这也是Cadence IC这个软件成功的重要原因。

鼠标命令如图1.8所示。

这一栏显示的是鼠标单击左、中、右键分别会执行的SKILL命令。

图1.8鼠标命令窗口提示栏:这一栏以”>”起头,如图1.9所示,显示的是当前正在Cadence IC程序的功能提示。

图1.9 提示栏窗口以下根据一般设计过程中的使用顺序,对一些常用工具进行详细介绍。

1.3 Library Manager设计库管理器首先介绍的是设计库管理器(Library Manager)。

图1.3中的窗口是设计库管理器的窗口,如果打开平时隐藏的分类(Category)面板和文件(Files)面板则显示界面如图1.10所示。

该界面分为如下几部分:菜单栏、面板显示选项栏、设计库浏览面板和信息,以下将一一介绍。

图1.1 设计库管理器的分类(Category)面板和文件(Files)面板1.3.1 设计库浏览面板设计库浏览面板如图1.10所示。

面板处于设计库浏览器的中部,从左到右共分有4栏,分别为设计库(Library)、类别(Category)、单元(Cell)、显示(View)栏。

右面的3栏中每一栏中显示的都是该栏的左邻栏中选定的项目的展开。

例如:图中的分类栏中显示的就是设计库“analogLib”中的内容,而单元栏中显示的就是分类“Parasitics”包含的内容,同样“View”栏中列出的就是单元“pcapacitor”所包含的内容。

另外,还可以打开“Show Files”选项,显示各个单元和“View”所对应的文件。

也就是图中面板管理器右下角的两栏,标题是“Files in Library”和“Files in Cell”。