第1章 数制与编码

- 格式:ppt

- 大小:817.00 KB

- 文档页数:65

第一章数制与编码1.1 自测练习1.1.1、模拟量数字量1.1.2、(b)1.1.3、(c)1.1.4、(a)是数字量,(b)(c)(d)是模拟量1.2 自测练习1.2.1. 21.2.2. 比特bit1.2.3. 101.2.4. 二进制1.2.5. 十进制1.2.6. (a)1.2.7. (b)1.2.8. (c)1.2.9. (b)1.2.10. (b)1.2.11. (b)1.2.12. (a)1.2.13. (c)1.2.14. (c)1.2.15. (c)1.2.16. 1001001 1.2.17. 111.2.18. 110010 1.2.19. 1101 1.2.20. 8进制1.2.21. (a)1.2.22. 0,1,2,3,4,5,6,71.2.23. 十六进制1.2.24. 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F 1.2.25. (b)1.3 自测练习1.3.1. 1221.3.2. 675.521.3.3. 011111110.011.3.4. 521.3.5. 1BD.A81.3.6. 1110101111.11101.3.7. 38551.3.8. 28.3751.3.9. 100010.111.3.10. 135.6251.3.11. 570.11.3.12. 120.51.3.13. 2659.A1.4 自测练习1.4.1. BCD Binary coded decimal 二—十进制码1.4.2. (a)1.4.3. (b)1.4.4. 8421BCD码,4221BCD码,5421BCD 1.4.5. (a)1.4.6. 011001111001.10001.4.7. 111111101.4.8. 101010001.4.9. 111111011.4.10. 61.051.4.11. 01011001.01110101 1.4.12. 余3码1.4.13. XS31.4.14. XS31.4.15. 1000.10111.4.16. 1001100000111.4.17. 521.4.18. 110101.4.19. 0101111.4.20. (b)1.4.21. ASCII1.4.22. (a)1.4.23. ASCII American Standard Code for Information Interchange美国信息交换标准码EBCDIC Extended Binary Coded Decimal Interchange Code 扩展二-十进制交换吗1.4.24. 10010111.4.25. ASCII1.4.26. (b)1.4.27. (b)1.4.28. 110111011.4.29. -1111.4.30. +231.4.31. -231.4.32. -861.5 自测练习1.5.1 略1.5.2 110111011.5.3 010001011.5.4 11100110 补码形式1.5.5 011111011.5.6 10001000 补码形式1.5.7 11100010 补码形式习题1.1 (a)(d)是数字量,(b)(c)是模拟量,用数字表时(e)是数字量,用模拟表时(e)是模拟量1.2 (a)7, (b)31, (c)127, (d)511, (e)40951.3 (a),(b),(c)(d)522104108×+×+320410910×+×+×26108108×+×+321102105100×+×+×+21+1.4 (a), (b), (c)(d)3212121×+×+984+12+12+×××4311212121×+×+×+212×64212+12+12+12+1××××1212+×2220110327.15310210710110510..=×+×+×+×+×3210-1-221011.0112+02+12+12+02+12=××××××210-18437.448+38+78+48=××××10-1-2163A.1C316+A16+116+C16=××××,,,1.6 (a)11110, (b)100110,(c)110010, (d)10111.7 (a)1001010110000, (b)10010111111.8 110102 = 2610, 1011.0112 = 11.37510,57.6438 = 71.81835937510,76.EB16 = 118. 91796875101.9 1101010010012 = 65118 = D4916,0.100112 = 0.468 = 0.9816,1011111.011012 = 137.328 = 5F.68161.10 168 = 1410,1728 = 12210,61.538 = 49.671875,126.748 = 86.9375101.11 2A16 = 4210 = 1010102 = 528,B2F16 = 286310 = 1011001011112 = 54578,D3.E16= 211.87510 = 11010011.11102 = 323.78,1C3.F916 = 451.9726562510 =111000011.111110012 = 703.76281.12 (a)E, (b)2E, (c)1B3, (d)3491.13 (a)22, (b)110, (c)1053, (d)20631.14 (a)4094, (b)1386, (c)492821.15 (a)23, (b)440, (c)27771.16 198610 = 111110000102 = 00011001100001108421BCD,67.31110 = 1000011.010012 =01100111.0011000100018421BCD, 1.183410 = 1.0010112 = 0001.00011000001101008421BCD ,0.904710 = 0.1110012 = 0000.10010000010001118421BCD1.17 1310 = 000100118421BCD = 01000110XS3 = 1011Gray, 6.2510 = 0110.001001018421BCD =1001.01011000 XS3 = 0101.01Gray,0.12510 = 0000.0001001001018421BCD =0.010*********XS3 = 0.001 Gray1.18 101102 = 11101 Gray,0101102 = 011101 Gray1.19 110110112 = 0010000110018421BCD,45610 = 0100010101108421BCD,1748=0010011101008421BCD,2DA16 = 0111001100008421BCD,101100112421BCD = 010*********BCD,11000011XS3 = 100100008421BCD1.20 0.0000原= 0.0000反= 0.0000补,0.1001原= 0.1001反= 0.1001补,11001原= 10110反= 10111补1.21 010100原= 010100补,101011原= 110101补,110010原= 101110补,100001原= 111111补1.22 1310 = 00001101补,11010 = 01101110补,-2510 = 11100111补,-90 =10100110补1.23 01110000补= 11210,00011111补= 3110,11011001补= -3910,11001000补= -56101.24 1000011 1000001 1010101 1010100 1001001 1001111 1001110 0100001 0100000 1001000 1101001 1100111 1101000 0100000 1010110 1101111 1101100 1110100 1100001 1100111 11001011.25 0100010 1011000 0100000 0111101 0100000 0110010 0110101 0101111 1011001 01000101.26 BEN SMITH1.27 00000110 100001101.28 01110110 10001110第二章逻辑门2.1 自测练习2.1.1. (b)2.1.2. 162.1.3. 32, 6 2.1.4. 与2.1.5. (d)2.1.6. 162.1.7. 32, 6 2.1.8. 或2.1.9. 非2.1.10. 12.2 自测练习2.2.1. FAB=.2.2.2. (b)2.2.3. 高2.2.4. 322.2.5. 16,52.2.6. 12.2.7. 串联2.2.8. (d)2.2.9. 不相同2.2.10. 高2.2.11. 相同2.2.12. (a)2.2.13. (c)2.2.14. 奇2.3 自测练习2.3.1. OC,上拉电阻2.3.2. 0,1,高阻2.3.3. (b)2.3.4. (c)2.3.5. ,FAB=. 高阻2.3.6. 不能2.4 自测练习2.4.1. TTL,CMOS2.4.2. Transisitor Transistor Logic2.4.3. Complementary Metal Oxide Semicoductor2.4.4. 高级肖特基TTL,低功耗和高级低功耗肖特基TTL 2.4.5. 高,强,小2.4.6. (c)2.4.7. (b)2.4.8. (c)2.4.9. 大2.4.10. 强2.4.11. (a)2.4.12. (a)2.4.13. (b)2.4.14. 高级肖特基TTL2.4.15. (c)习题2.1 与,或,与2.2 与门,或门,与门2.3 (a)F=A+B, F=AB (b)F=A+B+C, F=ABC (c)F=A+B+C+D, F=ABCD 2.4 (a)0 (b)1 (c)0 (d)02.5 (a)0 (b)0 (c)1 (d)02.6 (a)1 (b)1 (c)1 (d)12.7 (a)4 (b)8 (c)16 (d)322.8 (a)3 (b)4 (c)5 (d)6ABCF0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 11111112.9 (a)(b)ABCDF1110 1 1 1 0 1 0 0 00 1 0 1 1 0 1 1 0 1 0 1 1 1 0 1 0 0 0 0 1 00 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 111111112.10 YABAC=+ 2.11ABCY0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 11111112.122.13F1 = A(B+C), F2=A+BCA B C F1 F2 0 0 0 0 0 0 0 1 0 0 0 1 0 00 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 1 1 111112.142.15 (a)0 (b)1 (c)1 (d)02.16 (a)1 (b)0 (c)0 (d)12.17 (a)0 (b)02.182.19 CDEF.2.20 CY ABDF.2.21 102.22 402.23 当TTL反相器的输出为3V,输出是高电平,红灯亮。

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

《数字电子技术》目录第1章数制与编码1.1 数字电路基础知识1.1.1 模拟信号与数字信号1.1.2 数字电路的特点1.2 数制1.2.1 十进制数1.2.2 二进制数1.2.3 八进制数1.2.4 十六进制数1.3 数制转换1.3.1 二进制数与八进制数的相互转换1.3.2 二进制数与十六进制数的相互转换1.3.3 十进制数与任意进制数的相互转换1.4 二进制编码1.4.1 加权二进制码1.4.2 不加权的二进制码1.4.3 字母数字码1.4.4 补码1.5带符号二进制数的加减运算1.5.1 加法运算1.5.2 减法运算第2章逻辑门2.1 基本逻辑门2.1.1 与门2.1.2 或门2.1.3 非门2.2 复合逻辑门2.2.1 与非门2.2.2 或非门2.2.3 异或门2.2.4 同或门2.3 其它逻辑门2.3.1 集电极开路逻辑门2.3.2 集电极开路逻辑门的应用2.3.3 三态逻辑门2.4 集成电路逻辑门2.4.1 概述2.4.2 TTL集成电路逻辑门2.4.3 CMOS集成电路逻辑门2.4.4 集成逻辑门的性能参数2.4.5 TTL与CMOS集成电路的接口*第3章逻辑代数基础3.1 概述3.1.1 逻辑函数的基本概念3.1.2 逻辑函数的表示方法3.2 逻辑代数的运算规则3.2.1 逻辑代数的基本定律3.2.2 逻辑代数的基本公式3.2.3 摩根定理3.2.4 逻辑代数的规则3.3 逻辑函数的代数化简法3.3.1 并项化简法3.3.2 吸收化简法3.3.3 配项化简法3.3.4 消去冗余项法3.4 逻辑函数的标准形式3.4.1 最小项与最大项3.4.2 标准与或表达式3.4.3 标准或与表达式3.4.4 两种标准形式的相互转换3.4.5 逻辑函数表达式与真值表的相互转换3.5 逻辑函数的卡诺图化简法3.5.1 卡诺图3.5.2 与或表达式的卡诺图表示3.5.3 与或表达式的卡诺图化简3.5.4 或与表达式的卡诺图化简3.5.5 含无关项逻辑函数的卡诺图化简3.5.6 多输出逻辑函数的化简*第4章组合逻辑电路4.1 组合逻辑电路的分析4.1.1 组合逻辑电路的定义4.1.2 组合逻辑电路的分析步骤4.1.3 组合逻辑电路的分析举例4.2 组合逻辑电路的设计4.2.1 组合逻辑电路的一般设计步骤4.2.2 组合逻辑电路的设计举例4.3 编码器4.3.1 编码器的概念4.3.2 二进制编码器4.3.3 二-十进制编码器4.3.4 编码器应用举例4.4 译码器4.4.1 译码器的概念4.4.2 二进制译码器4.4.3 二-十进制译码器4.4.4 用译码器实现逻辑函数4.4.5 显示译码器4.4.6 译码器应用举例4.5 数据选择器与数据分配器4.5.1 数据选择器4.5.2 用数据选择器实现逻辑函数4.5.3 数据分配器4.5.4 数据选择器应用举例4.6 加法器4.6.1 半加器4.6.2 全加器4.6.3 多位加法器4.6.4 加法器应用举例4.6.5 加法器构成减法运算电路*4.7 比较器4.7.1 1位数值比较器4.7.2 集成数值比较器4.7.3 集成数值比较器应用举例4.8 码组转换电路4.8.1 BCD码之间的相互转换4.8.2 BCD码与二进制码之间的相互转换4.8.3 格雷码与二进制码之间的相互转换4.9 组合逻辑电路的竞争与冒险4.9.1 冒险现象的识别4.9.2 消除冒险现象的方法第5章触发器5.1 RS触发器5.1.1 基本RS触发器5.1.2 钟控RS触发器5.1.3 RS触发器应用举例5.2 D触发器5.2.1 电平触发D触发器5.2.2 边沿D触发器5.3 JK触发器5.3.1 主从JK触发器5.3.2 边沿JK触发器5.4 不同类型触发器的相互转换5.4.1 概述5.4.2 D触发器转换为JK、T和T'触发器5.4.3 JK触发器转换为D触发器第6章寄存器与计数器6.1 寄存器与移位寄存器6.1.1 寄存器6.1.2 移位寄存器6.1.3移位寄存器应用举例6.2 异步N进制计数器6.2.1 异步n位二进制计数器6.2.2 异步非二进制计数器6.3 同步N进制计数器6.3.1 同步n位二进制计数器6.3.2 同步非二进制计数器6.4 集成计数器6.4.1 集成同步二进制计数器6.4.2 集成同步非二进制计数器6.4.3 集成异步二进制计数器6.4.4 集成异步非二进制计数器6.4.5 集成计数器的扩展6.4.6 集成计数器应用举例第7章时序逻辑电路的分析与设计7.1 概述7.1.1 时序逻辑电路的定义7.1.2 时序逻辑电路的结构7.1.3 时序逻辑电路的分类7.2 时序逻辑电路的分析7.2.1时序逻辑电路的分析步骤7.2.2 同步时序逻辑电路分析举例7.2.3 异步时序逻辑电路分析举例7.3 同步时序逻辑电路的设计7.3.1 同步时序逻辑电路的基本设计步骤7.3.2 同步时序逻辑电路设计举例第8章存储器与可编程器件8.1 存储器概述8.1.1 存储器的分类8.1.2 存储器的相关概念8.1.3 存储器的性能指标8.2 RAM8.2.1 RAM分类与结构8.2.2 SRAM8.2.3 DRAM8.3 ROM8.3.1 ROM分类与结构8.3.2 掩膜ROM8.3.3 可编程ROM8.3.4 可编程ROM的应用8.4 快闪存储器(Flash Memory)8.4.1 快闪存储器的电路结构8.4.2 闪存与其它存储器的比较8.5 存储器的扩展8.5.1 存储器的位扩展法8.5.2 存储器的字扩展法8.6 可编程阵列逻辑8.6.1 PAL的电路结构8.6.2 PAL器件举例8.6.3 PAL器件的应用8.7 通用阵列逻辑8.7.1 GAL的性能特点8.7.2 GAL的电路结构8.7.3 OLMC8.7.4 GAL器件的编程与开发8.8 CPLD、FPGA和在系统编程技术8.8.1 数字可编程器件的发展概况8.8.2数字可编程器件的编程语言8.8.3数字可编程器件的应用实例第9章D/A转换器和A/D转换器9.1 概述9.2 D/A转换器9.2.1 D/A转换器的电路结构9.2.2 二进制权电阻网络D/A转换器9.2.3 倒T型电阻网络D/A转换器9.2.4 D/A转换器的主要技术参数9.2.5 集成D/A转换器及应用举例9.3 A/D转换器9.3.1 A/D转换的一般步骤9.3.2 A/D转换器的种类9.3.3 A/D转换器的主要技术参数9.3.4 集成A/D转换器及应用举例第10章脉冲波形的产生与整形电路10.1 概述10.2 多谐振荡器10.2.1 门电路构成的多谐振荡器10.2.2 采用石英晶体的多谐振荡器10.3 单稳态触发器10.3.1 门电路构成的单稳态触发器10.3.2 集成单稳态触发器10.3.3 单稳态触发器的应用10.4 施密特触发器10.4.1 概述10.4.2 施密特触发器的应用10.5 555定时器及其应用10.5.1 电路组成及工作原理10.5.2 555定时器构成施密特触发器10.5.3 555定时器构成单稳态触发器10.5.4 555定时器构成多谐振荡器第11章数字集成电路简介11.1 TTL门电路11.1.1 TTL与非门电路11.1.2 TTL或非门电路11.1.3 TTL与或非门电路11.1.4 集电极开路门电路与三态门电路11.1.5 肖特基TTL与非门电路11.2 CMOS门电路11.2.1 概述11.2.2 CMOS非门电路11.2.3 CMOS与非门电路11.2.4 CMOS或非门电路11.2.5 CMOS门电路的构成规则11.3 数字集成电路的使用。

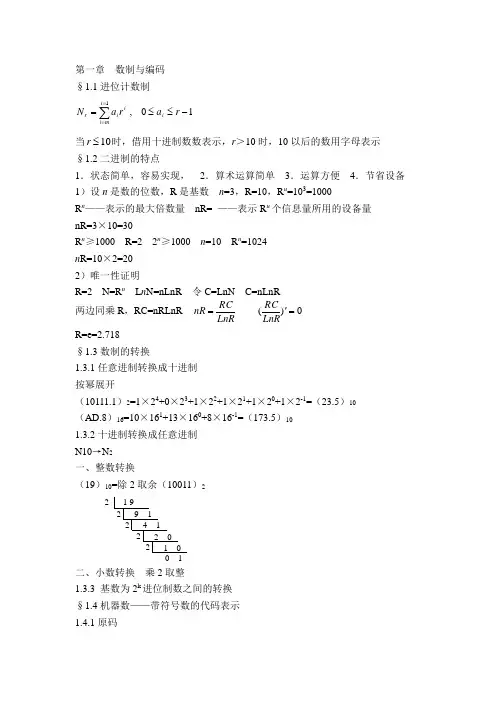

第一章 数制与编码§1.1进位计数制∑==-≤≤=110,i m i i i i r r a r a N当10≤r 时,借用十进制数数表示,r >10时,10以后的数用字母表示 §1.2二进制的特点1.状态简单,容易实现, 2.算术运算简单 3.运算方便 4.节省设备1)设n 是数的位数,R 是基数 n =3,R=10,R u =103=1000R n ——表示的最大倍数量 nR= ——表示R u 个信息量所用的设备量nR=3×10=30R n ≥1000 R=2 2n ≥1000 n =10 R n =1024n R=10×2=202)唯一性证明R=2 N=R n L n N=nLnR 令C=LnN C=nLnR两边同乘R ,RC=nRLnR LnR RC nR = 0)(='L n RRC R=e=2.718§1.3数制的转换1.3.1任意进制转换成十进制按幂展开(10111.1)2=1×24+0×23+1×22+1×21+1×20+1×2-1=(23.5)10(AD.8)16=10×161+13×160+8×16-1=(173.5)101.3.2十进制转换成任意进制N10→N 2一、整数转换(19)10=除2取余(10011)2二、小数转换 乘2取整1.3.3 基数为2k 进位制数之间的转换§1.4机器数——带符号数的代码表示1.4.1原码 1 92 9 12 4 12 2 02 1 02 0 1一、原码的表示符号位表示数的符号,其余位表示数的本身,和真值相同,只是符号位负数用1表示,正数用0表示。

N 3=+0.1011 [N 3]原=0.1011N 4=-0.1011 [N 4]原=1.1011原码形成规则对于n 位的整数N (含一位符号位),[N]原=对于小数[N]原= N2=-1011 [N 2]原=25-1-(-1011)=10000+1011=11011二、原码的性质1.若N ≥0时,[N]原=N ,若N ≤0时,符号位为1,尾数不变。

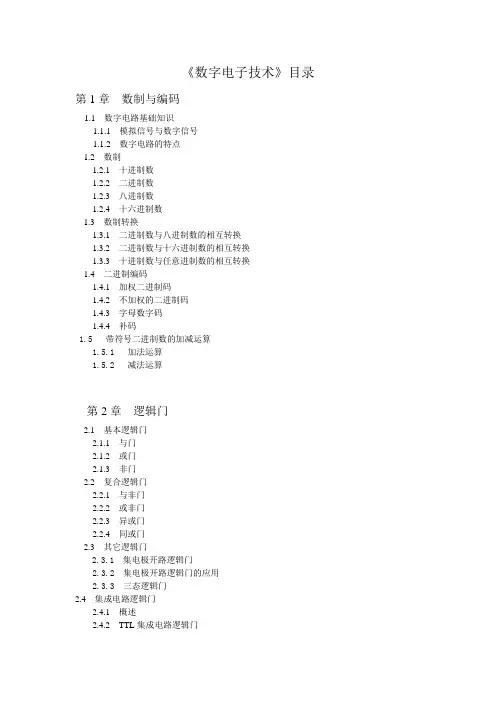

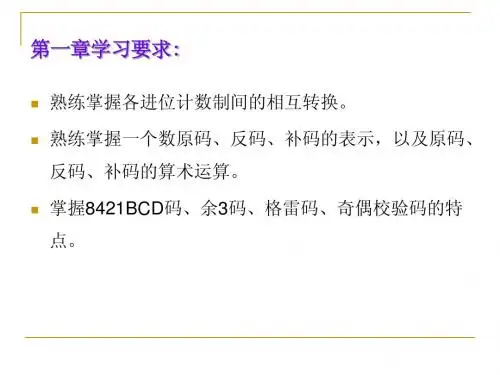

第⼀章数制和码制第⼀章数制和码制本章教学⽬的、要求:1.掌握⼆进制、⼋进制、⼗进制、⼗六进制及其相互转换。

2.掌握原码、反码、补码的概念及转换,了解⼆进制补码的运算。

3.理解常⽤8421BCD 码和可靠性代码。

重点:不同进制数间的转换。

难点:补码的概念及⼆进制补码的运算。

第⼀节概述(⼀)数字量与模拟量数字量:物理量的变化在时间上和数量上都是离散的。

它们数值的⼤⼩和每次变化的增减变化都是某⼀个最⼩数量单位的整数倍,⽽⼩于这个最⼩数量单位的数值没有任何物理意义。

例如:统计通过某⼀个桥梁的汽车数量,得到的就是⼀个数字量,最⼩数量单位的“1”代表“⼀辆”汽车,⼩于1的数值已经没有任何物理意义。

数字信号:表⽰数字量的信号。

如矩形脉冲。

数字电路:⼯作在数字信号下的电⼦电路。

模拟量:物理量的变化在时间上和数值上都是连续的。

例如:热电偶⼯作时输出的电压或电流信号就是⼀种模拟信号,因为被测的温度不可能发⽣突跳,所以测得的电压或电流⽆论在时间上还是在数量上都是连续的。

模拟信号:表⽰模拟量的信号。

如正弦信号。

模拟电路:⼯作在模拟信号下的电⼦电路。

这个信号在连续变化过程中的任何⼀个取值都有具体的物理意义,即表⽰⼀个相应的温度。

(⼆)数字信号的⼀些特点数字信号通常都是以数码形式给出的。

不同的数码不仅可以⽤来表⽰数量的不同⼤⼩,⽽且可以⽤来表⽰不同的事物或事物的不同状态。

tu t第⼆节⼏种常⽤的数制数制:把多位数码中每⼀位的构成⽅法以及从低位到⾼位的进位规则称为数制。

在数字电路中经常使⽤的计数进制有⼗进制、⼆进制和⼗六进制。

有时也⽤到⼋进制。

⼀、⼗进制数(Decimal)⼗进制是⽇常⽣活中最常使⽤的进位计数制。

在⼗进制数中,每⼀位有0~9⼗个数码,所以计数的基数是10。

超过9的数必须⽤多位数表⽰,其中低位和相邻⾼位之间的进位关系是“逢⼗进⼀”。

任意⼗进制数 D 的展开式:i i k D 10∑= k i 是第 i 位的系数,可以是0~9中的任何⼀个。