VHDL语言的基本要素(大全)

- 格式:doc

- 大小:106.50 KB

- 文档页数:6

VHDL入门教程VHDL(Very High-speed Integrated Circuit HardwareDescription Language)是一种用于设计数字电路的硬件描述语言。

它是IEEE 1076标准中规定的一种语言,广泛应用于数字电路的设计、仿真和综合等领域。

本文将为大家介绍VHDL的基础知识和入门教程。

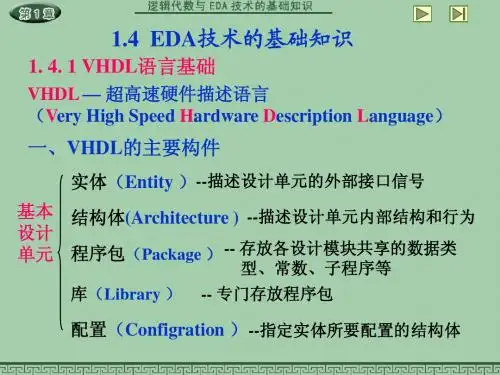

一、VHDL的基本概念1. 实体(Entity):VHDL代码的最高层次,用于定义模块的输入、输出和内部信号。

2. 架构(Architecture):定义了实体中的各个信号和组合逻辑的行为。

3. 信号(Signal):表示数据在电路中的传输和操作。

4. 进程(Process):定义了组合逻辑的行为,用于描述信号之间的关系。

5. 实体声明(Entity Declaration):用于描述模块的名称、输入、输出和内部信号。

6. 架构声明(Architecture Declaration):用于描述模块的内部逻辑。

二、VHDL的基本语法1.实体声明语法:```entity entity_name isport ( port_list );end entity_name;```其中,entity_name是实体的名称,port_list是实体的输入、输出和内部信号。

2.架构声明语法:```architecture architecture_name of entity_name issignal signal_list;beginprocess (sensitivity_list)begin--逻辑行为描述end process;end architecture_name;```其中,architecture_name是架构的名称,entity_name是实体的名称,signal_list是架构的内部信号,sensitivity_list是触发事件的信号列表。

三、VHDL的基本例子下面以一个简单的4位加法器为例介绍VHDL的编写和仿真流程。

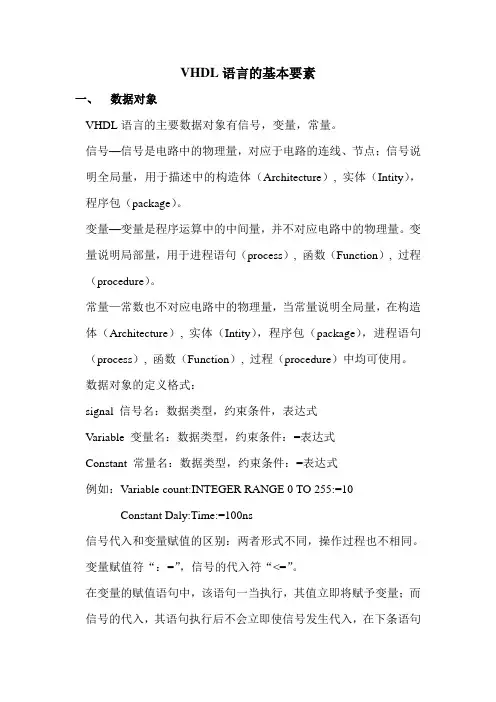

VHDL语言的基本要素一、数据对象VHDL语言的主要数据对象有信号,变量,常量。

信号—信号是电路中的物理量,对应于电路的连线、节点;信号说明全局量,用于描述中的构造体(Architecture), 实体(Intity),程序包(package)。

变量—变量是程序运算中的中间量,并不对应电路中的物理量。

变量说明局部量,用于进程语句(process), 函数(Function), 过程(procedure)。

常量—常数也不对应电路中的物理量,当常量说明全局量,在构造体(Architecture), 实体(Intity),程序包(package),进程语句(process), 函数(Function), 过程(procedure)中均可使用。

数据对象的定义格式:signal 信号名:数据类型,约束条件,表达式Variable 变量名:数据类型,约束条件:=表达式Constant 常量名:数据类型,约束条件:=表达式例如:Variable count:INTEGER RANGE 0 TO 255:=10Constant Daly:Time:=100ns信号代入和变量赋值的区别:两者形式不同,操作过程也不相同。

变量赋值符“:=”,信号的代入符“<=”。

在变量的赋值语句中,该语句一当执行,其值立即将赋予变量;而信号的代入,其语句执行后不会立即使信号发生代入,在下条语句执行时,仍使用原来的信号值,如进程语句中的敏感表的信号代入就是如此。

二、数据类型VHDL语言中的数据类型,一般而言可分为:标量类型和组合类型。

在实际使用中,也可分成予定义类型和用户定义类型。

VHDL语言是强类型的语言,主要可按如下分类和变换处理。

①标准数据类型⑴整数⑵实数(浮点数)-1.0E+38~+1.0E38 ⑶位bit(0,1)⑷位矢量⑸布尔量,“假”,“真”⑹字符(ASCⅡ)字符⑺时间⑻错误等级⑼自然数(大于等于0的整数)⑽字符串(字符矢量)②用户定义的数据类型TYPE 数据类型名{数据类型名} 数据类型定义⑴枚举类型⑵整数类型⑶实数类型⑷数组类型⑸存取类型⑹文件类型⑺记录类型⑻时间类型③用户定义子类型SUBTUPE 子类型名IS 数据类型名[范围]例:SUBTYPE digit is INTEGER RANGE 0 TO 9④数据类型转换数据类型的变换函数通常由“STD_LOGIC_1164”,“STD_LOGIC_ARITH”,“STD_LOGIC_UNSIGNED”的程序包提供例如,在STD_LOGIC_1164程序包中,TO_STD LOGIC VECTOR(A) 由BIT_VECTOR转换为STD_LOGIC_VECTORTO_BITVECTOR(A) 由STO_LOGIC_VECTOR转为BIT_VECTORTO_STDLOGIC(A) 由BIT转换为STD_LOGICTO_BIT(A) 由STD_LOGIC转换成BIT signal a: BIT_VECTOR(11 DOWNTO 0)signal b: STD_LOGIC_VECTOR(11 DOWNTO 0)a<=X”A8” 十六进制值可赋予位矢量b<=X”A8” 语法错,十六进制不能赋予.STD 矢量b<=TO_STDLOGICVECTOR(X“AF7”)b<=TO_STDLOGICVECTOR(O“5177”)八进制变换b<=TO_STDLOGICVECTCR(B“1010_1111_0111”)下表中也给出一些典型的类型变换函数三、运算符运算符的优先级如下表所示:运算符的优先级例如,并置运算符的使用:tmp_b<=b AND (en&en&en&en) y <= a & tmp_b第一个语句表示b 的4位位矢量由en 进行选择 得到一个4位位矢量输出第二个语句表示4位位矢量a 和4位位矢量b 再 次连接(并置)构成8位的位矢量y 输出 右图所示为并置运算符操作的电路示意。

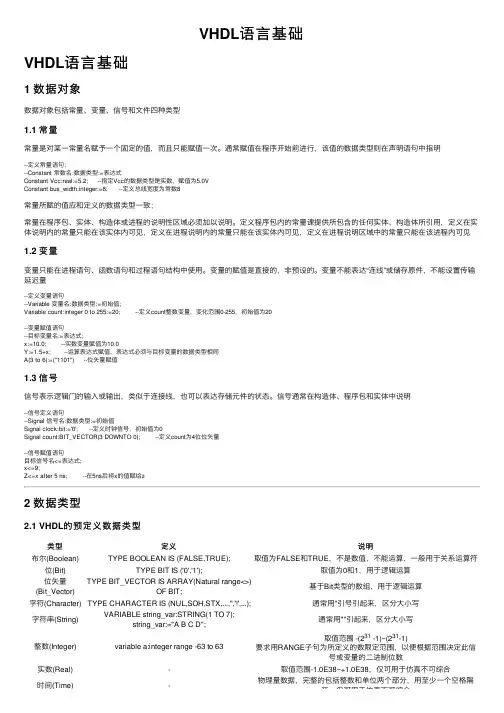

VHDL语⾔基础VHDL语⾔基础1 数据对象数据对象包括常量、变量、信号和⽂件四种类型1.1 常量常量是对某⼀常量名赋予⼀个固定的值,⽽且只能赋值⼀次。

通常赋值在程序开始前进⾏,该值的数据类型则在声明语句中指明--定义常量语句:--Constant 常数名:数据类型:=表达式Constant Vcc:real:=5.2; --指定Vcc的数据类型是实数,赋值为5.0VConstant bus_width:integer:=8; --定义总线宽度为常数8常量所赋的值应和定义的数据类型⼀致;常量在程序包、实体、构造体或进程的说明性区域必须加以说明。

定义程序包内的常量课提供所包含的任何实体、构造体所引⽤,定义在实体说明内的常量只能在该实体内可见,定义在进程说明内的常量只能在该实体内可见,定义在进程说明区域中的常量只能在该进程内可见1.2 变量变量只能在进程语句、函数语句和过程语句结构中使⽤。

变量的赋值是直接的,⾮预设的。

变量不能表达“连线”或储存原件,不能设置传输延迟量--定义变量语句--Variable 变量名:数据类型:=初始值;Variable count:integer 0 to 255:=20; --定义count整数变量,变化范围0-255,初始值为20--变量赋值语句--⽬标变量名:=表达式;x:=10.0; --实数变量赋值为10.0Y:=1.5+x; --运算表达式赋值,表达式必须与⽬标变量的数据类型相同A(3 to 6):=("1101") --位⽮量赋值1.3 信号信号表⽰逻辑门的输⼊或输出,类似于连接线,也可以表达存储元件的状态。

信号通常在构造体、程序包和实体中说明--信号定义语句--Signal 信号名:数据类型:=初始值Signal clock:bit:='0'; --定义时钟信号,初始值为0Signal count:BIT_VECTOR(3 DOWNTO 0); --定义count为4位位⽮量--信号赋值语句⽬标信号名<=表达式;x<=9;Z<=x after 5 ns; --在5ns后将x的值赋给z2 数据类型2.1 VHDL的预定义数据类型类型定义说明布尔(Boolean)TYPE BOOLEAN IS (FALSE,TRUE);取值为FALSE和TRUE,不是数值,不能运算,⼀般⽤于关系运算符位(Bit)TYPE BIT IS ('0','1');取值为0和1,⽤于逻辑运算位⽮量(Bit_Vector)TYPE BIT_VECTOR IS ARRAY(Natural range<>)OF BIT;基于Bit类型的数组,⽤于逻辑运算字符(Character)TYPE CHARACTER IS (NUL,SOH,STX,...,'','!',...);通常⽤''引号引起来,区分⼤⼩写字符串(String)VARIABLE string_var:STRING(1 TO 7);string_var:="A B C D";通常⽤""引起来,区分⼤⼩写整数(Integer)variable a:integer range -63 to 63取值范围 -(231 -1)~(231-1)要求⽤RANGE⼦句为所定义的数限定范围,以便根据范围决定此信号或变量的⼆进制位数实数(Real)-取值范围-1.0E38~+1.0E38,仅可⽤于仿真不可综合时间(Time)-物理量数据,完整的包括整数和单位两个部分,⽤⾄少⼀个空格隔开,仅可⽤于仿真不可综合时间(Time)-开,仅可⽤于仿真不可综合错误等级(SeverityLevel)TYPE severity_level IS (NOTE、WARNING、ERROR、FAILURE);表⽰系统状态,仅可⽤于仿真不可⽤于综合类型定义说明2.2 IEEE预定义标准逻辑位与⽮量标准逻辑类型对数字逻辑电路的逻辑特性描述更加完整、真实,因此在VHDL程序中,对逻辑信号的定义通常采⽤标准逻辑类型标准逻辑位(Std_Logic)符号说明'U'Undefined(未初始化)'X'Forcing Unknown(强未知)'0'Forcing 0(强0)'1'Forcing 1(强1)'Z'High Impedance(⾼阻)'W'Weak Unknown(弱未知)'L'Weak 0(弱0)'H'Weak 1(弱1)'-'Don't Care(忽略)标准逻辑位⽮量(Std_Logic_Vector)基于Std_Logic类型的数组使⽤Std_Logic和Std_Logic_Vector要调⽤IEEE库中的Std_Logic_1164程序包;就综合⽽⾔,能够在数字器件中实现的是“-、0、1、Z”四种状态。

VHDL语言的基本知识点罗列1 VHDL语言的标识符VHDL中的标识符可以是常数、变量、信号、端口、子程序或参数的名字。

使用标识符要遵守如下法则:a)标识符由字母(A…Z;a…z)、数字和下划线字符组成。

任何标识符必须以英文字母开头。

λ末字符不能为下划线。

λb)不允许出现两个连续下划线。

标识符中不区分大小写字母。

λVHDL定义的保留子或称关键字,不能用作标识符。

λc) VHDL中的注释由两个连续的短线(--)开始,直到行尾。

以下是非法标识符:-Decoder —起始不能为非英文字母3DOP —起始不能为数字Large#number —“#”不能成为标识符的构成符号Data__bus —不能有双下划线Copper_ —最后字符不能为下划线On —关键字不能用作标识符。

注:在AHDL语言中标识符要区分大小写,但在VHDL语言中不区分大小写。

所以写程序时,一定要养成良好的书写习惯,应用关键字时用大写,自己定义的标识符用小写。

标识符表示的几种数据对象的详细说明如下:1) 常数(Constant )常数是一个固定的值,主要是为了使设计实体中的常数更容易阅读和修改。

常数一被赋值就不能在改变。

一般格式:CONSTANT 常数名:数据类型:=表达式;例:CONSTANT Vcc: REAL: =5.0;—设计实体的电源电压指定常数所赋得值应与定义的数据类型一致。

常量的使用范围取决于它被定义的位置。

程序包中定义的常量具有最大的全局化特性,可以用在调用此程序包的所有设计实体中;设计实体中某一结构体中定义的常量只能用于此结构体;结构体中某一单元定义的常量,如一个进程中,这个常量只能用在这一进程中。

2) 变量(Variable)变量是一个局部变量,它只能在进程语句、函数语句和进程语句结构中使用。

用作局部数据存储。

在仿真过程中。

它不像信号那样,到了规定的仿真时间才进行赋值,变量的赋值是立即生效的。

变量常用在实现某种算法的赋值语句中。

VHDL语言的基本要素

一、数据对象

VHDL语言的主要数据对象有信号,变量,常量。

信号—信号是电路中的物理量,对应于电路的连线、节点;信号说明全局量,用于描述中的构造体(Architecture), 实体(Intity),程序包(package)。

变量—变量是程序运算中的中间量,并不对应电路中的物理量。

变量说明局部量,用于进程语句(process), 函数(Function), 过程(procedure)。

常量—常数也不对应电路中的物理量,当常量说明全局量,在构造体(Architecture), 实体(Intity),程序包(package),进程语句(process), 函数(Function), 过程(procedure)中均可使用。

数据对象的定义格式:

signal 信号名:数据类型,约束条件,表达式

Variable 变量名:数据类型,约束条件:=表达式

Constant 常量名:数据类型,约束条件:=表达式

例如:Variable count:INTEGER RANGE 0 TO 255:=10

Constant Daly:Time:=100ns

信号代入和变量赋值的区别:两者形式不同,操作过程也不相同。

变量赋值符“:=”,信号的代入符“<=”。

在变量的赋值语句中,该语句一当执行,其值立即将赋予变量;而信号的代入,其语句执行后不会立即使信号发生代入,在下条语句

执行时,仍使用原来的信号值,如进程语句中的敏感表的信号代入就是如此。

二、数据类型

VHDL语言中的数据类型,一般而言可分为:标量类型和组合类型。

在实际使用中,也可分成予定义类型和用户定义类型。

VHDL语言是强类型的语言,主要可按如下分类和变换处理。

①标准数据类型

⑴整数⑵实数(浮点数)-1.0E+38~+1.0E38 ⑶位bit

(0,1)

⑷位矢量⑸布尔量,“假”,“真”⑹字符(ASCⅡ)字符

⑺时间

⑻错误等级⑼自然数(大于等于0的整数)⑽字符串

(字符矢量)

②用户定义的数据类型

TYPE 数据类型名{数据类型名} 数据类型定义

⑴枚举类型⑵整数类型⑶实数类型⑷数组类型

⑸存取类型⑹文件类型⑺记录类型⑻时间类型③用户定义子类型

SUBTUPE 子类型名IS 数据类型名[范围]

例:SUBTYPE digit is INTEGER RANGE 0 TO 9

④数据类型转换

数据类型的变换函数通常由“STD_LOGIC_1164”,

“STD_LOGIC_ARITH”,“STD_LOGIC_UNSIGNED”的程序包提供

例如,在STD_LOGIC_1164程序包中,

TO_STD LOGIC VECTOR(A) 由BIT_VECTOR转换为STD_LOGIC_VECTOR

TO_BITVECTOR(A) 由STO_LOGIC_VECTOR转为BIT_VECTOR

TO_STDLOGIC(A) 由BIT转换为STD_LOGIC

TO_BIT(A) 由STD_LOGIC转换成BIT signal a: BIT_VECTOR(11 DOWNTO 0)

signal b: STD_LOGIC_VECTOR(11 DOWNTO 0)

a<=X”A8” 十六进制值可赋予位矢量

b<=X”A8” 语法错,十六进制不能赋予.STD 矢量

b<=TO_STDLOGICVECTOR(X“AF7”)

b<=TO_STDLOGICVECTOR(O“5177”)八进制变换

b<=TO_STDLOGICVECTCR(B“1010_1111_0111”)

下表中也给出一些典型的类型变换函数

三、运算符

运算符的优先级如下表所示:运算符的优先级

例如,并置运算符的使用:

tmp_b<=b AND (en&en&en&en) y <= a & tmp_b

第一个语句表示b 的4位位矢量由en 进行选择 得到一个4位位矢量输出

第二个语句表示4位位矢量a 和4位位矢量b 再 次连接(并置)构成8位的位矢量y 输出 右图所示为并置运算符操作的电路示意。

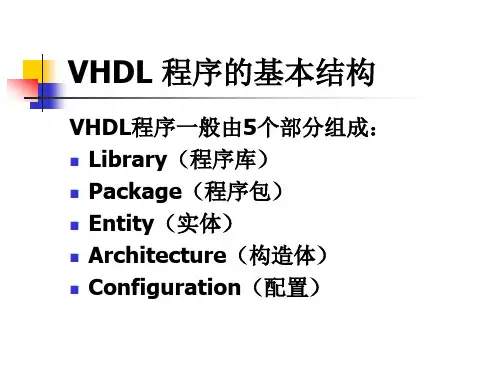

VHDL 语言程序的基本结构

⑴ 实体(Entity )

实体主要由实体说明和构造体组成;实体说明描述电路的外部特征,

构造体描述的是电路内部的逻辑。

①实体说明主要包括·类属参数说明 ·端口说明

②构造体主要包括 ·名称命名 ·定义语句 ·并行处理语句等 定义语句是对其内部使用的信号、常数、数据类型、函数定义

y(4) en

b(0) b(1) b(2) b(3) y(5) y(6) y(7)

a(0) a(1) a(2) a(3)

实体

实体说明

接口说明

构造体

功能定义entity top is port(

i, j, k: in bit; z: out bit);

end top;

architecture top of top is

signal h: bit;

begin

u1: and2 port map(a=>i, b=>j, x=>h); u2: or2 port map(a=>h, b=>k, y=>z); end;

端口配置中的形参和实参

设计实体与其实体说明、构造体的关系

⑵构造体的子结构

构造体的子结构主要可由如下语句结构组成

·Block语句结构

·Process语句结构过程(procedure)·SUBPROGRAMS结构

函数(Function)

⑶程序包、库、配置

重载运算符(overloaded operators):和其他运算符一样,关系运算符也可以重载。

重载运算符允许多种类型使用运算符(这些运算符不是由IEEE1076标准预定义的)。

运算符可能由用户定义函数重载,但很多重载运算符是由IEEE1164和IEEE1076.3标准所定义。

例如,IEEE 1076标准定义了为类型signed和integer以及unsigned和natural 重载=运算符的函数。

此重载运算符允许以下的代码段被执行。