第五讲 VHDL语言程序的基本结构

- 格式:ppt

- 大小:274.50 KB

- 文档页数:51

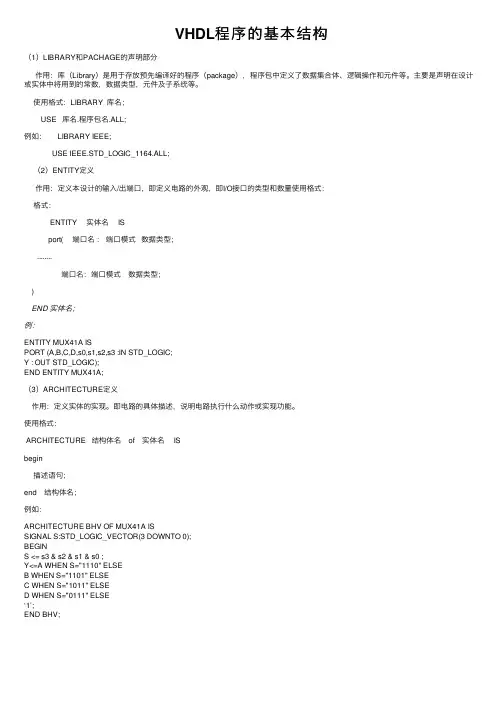

VHDL程序的基本结构(1)LIBRARY和PACHAGE的声明部分作⽤:库(Library)是⽤于存放预先编译好的程序(package),程序包中定义了数据集合体、逻辑操作和元件等。

主要是声明在设计或实体中将⽤到的常数,数据类型,元件及⼦系统等。

使⽤格式:LIBRARY 库名;USE 库名.程序包名.ALL;例如: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;(2)ENTITY定义作⽤:定义本设计的输⼊/出端⼝,即定义电路的外观,即I/O接⼝的类型和数量使⽤格式:格式:ENTITY 实体名 ISport( 端⼝名:端⼝模式数据类型;........端⼝名:端⼝模式数据类型;)END 实体名;例:ENTITY MUX41A ISPORT (A,B,C,D,s0,s1,s2,s3 :IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY MUX41A;(3)ARCHITECTURE定义作⽤:定义实体的实现。

即电路的具体描述,说明电路执⾏什么动作或实现功能。

使⽤格式:ARCHITECTURE 结构体名 of 实体名 ISbegin描述语句;end 结构体名;例如:ARCHITECTURE BHV OF MUX41A ISSIGNAL S:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINS <= s3 & s2 & s1 & s0 ;Y<=A WHEN S="1110" ELSEB WHEN S="1101" ELSEC WHEN S="1011" ELSED WHEN S="0111" ELSE‘1’;END BHV;。

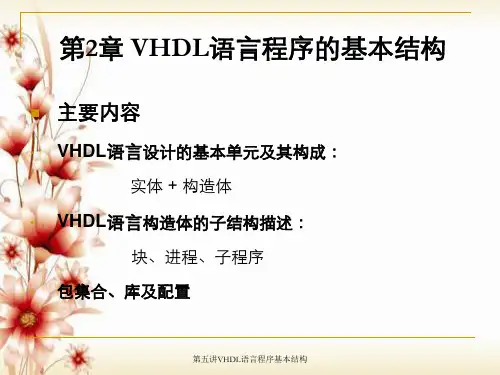

第5章 VHDL 基本结构与语法本章通过几个例题介绍VHDL 语言的基本结构和语法规则5.1 VHDL 基本结构一个相对完整的VHDL 设计由以下四部分组成:(1) 库LIBRARY 、程序包PACKAGE :库用于存储预先完成的程序包和数据集合体;程序包用于声明在设计中将要用到的常数、数据类型、元件及子程序等。

(2) 实体ENTITY :定义设计的输入输出端口。

(3) 结构体ARCHITECTURE :定义实体的实现,即电路的具体描述。

可有多个结构体,但只有一个起作用。

(4) 配置CONFIGURA TION :为实体选定某个特定的结构体。

以上四个部分不是每个VHDL 程序必须的,但每个VHDL 程序至少含有1个实体和1个结构体。

1个实体可有多个结构体,通过配置选择1个结构体对实体起作用,其他结构体不起作用。

当只有1个结构体时不要实体。

【例5-1】2选1多路数据选择器,其功能见图5-1。

功能描述为当S=0时A 送Y , S=1时B 送Y 。

其对应的VHDL 描述为:ENTITY mux21a IS --给出实体名mux21a 和管脚定义 PORT (a,b : IN BIT ;s : INBIT ; y : OUT BIT );END mux21a ;ARCHITECTURE one OF mux21a IS --结构体,描述电路器件的内部逻辑 BEGIN功能或电路结构。

y <=a WHEN s=’0’ ELSE b;END one ;综合后结构体的门电路见图5-3。

5.1.1 实体ENTITY :定义本设计的输入输出端口/信号。

图5-1 例5-1功能示意图图5-3 例5-1综合后的门电路A S约定:[]表示为可选项;--开始的语句为注释,不参与编译和综合;黑体单词为保留字。

1、实体框架:ENTITY实体名IS--此处无分号[GENERIC(常数名:数据类型[:设定值]);]PORT - -端口定义(端口1:端口模式端口类型;…端口n:端口模式端口类型- -最后一个无分号);END[ENTITY] 实体名;注:END中带ENTITY、ARCHITECTURE为IEEESTDl076_1993版的语法要求,不带为IEEESTD1076 1987的语法要求。

1.说明VHDL语言的基本结构。

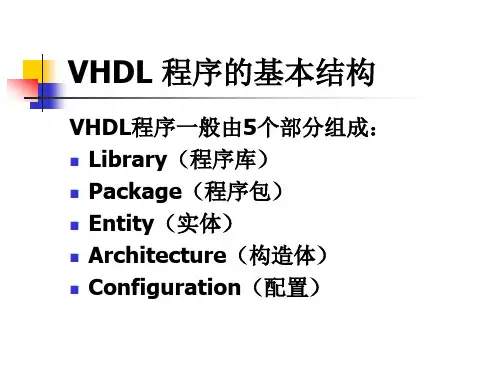

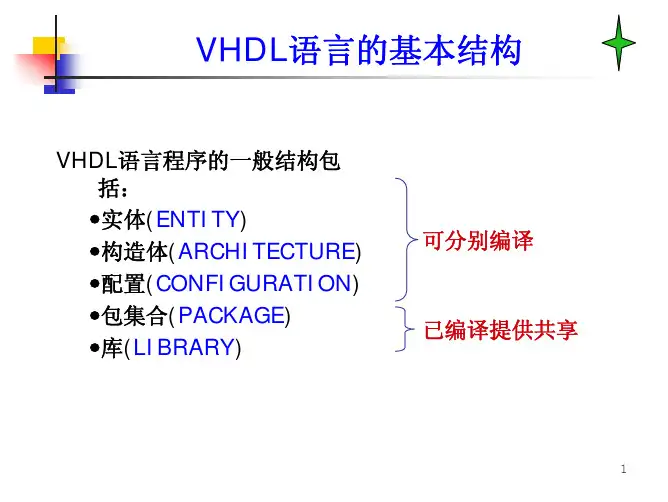

VHDL语言程序的一般结构包括:实体(ENTITY)、构造体(ARCHITECTURE)、配置(CONFIGURATION)、包集合(PACKAGE)、库(LIBRARY)。

2.说明端口模式的INOUT与BUFFER的异同。

INOUT为输入输出双向端口,即从端口内部看,可以对端口进行赋值,即输出数据。

也可以从此端口读入数据,即输入。

BUFFER为缓冲端口,功能与INOUT类似,区别在于当需要读入数据时,只允许内部回读内部产生的输出信号,即反馈。

举个例子,设计一个计数器的时候可以将输出的计数信号定义为BUFFER,这样回读输出信号可以做下一计数值的初始值。

3.VHDL语言有几种数据对象,请说明他们的功能以及使用方法,举例说明数据对象与数据类型之间的关系。

1.常量(CONSTANT):常量为全局量,是指在设计描述过程中保持某一规定类型特定值不变的量。

常量名:数据类型:=表达式;2.变量(VARIABLE):变量为局部量,常用来存储中间数据,以便实现程序的算法。

它只能在进程语句、函数语句和过程语句的结构中使用。

变量名1[ , 变量名2, …]: 数据类型[ := 初始值] ;3.信号(SIGNAL):信号是描述硬件系统的基本数据对象,它是电子电路内部硬件连接的抽象,可以作为设计实体中并行语句模块间的信息交流通道。

信号名:数据类型[:=初值];4.试用结构描述方式来描述图4-18(P137)所示的硬件电路。

Library IEEE;USE IEEE SID_LOGIC_1164.ALLENTITY fadder 3 ISPORT,(a,b,c:IN SID_LOGICY:OUT SID_LOGIC);END fadder 3;ARCHLIECTURE SUM OF fadder3 isSIGNAL to ,t1:SID_LOGICBEGINTo <=(NOT a,ANI) c T1<=(NOT a, ANI) b T2<=(NOT to ANI) t1 END SUM;1.用VHDL语言设计一个8位二进制全加器。