VHDL课程设计报告---交通灯设计

- 格式:doc

- 大小:222.00 KB

- 文档页数:32

基于VHDL 的交通灯控制器设计翟殿棠,方 敏,厉光伟(济南大学控制科学与工程学院 山东济南 250022)摘 要:传统的交通灯控制器多数由单片机或PLC 实现,本文介绍基于EDA 技术设计交通灯控制器的一种方案。

EDA 技术的一个重要特征就是使用硬件描述语言(HDL)来完成系统的设计文件,这在电子设计领域已得到设计者的广泛采用。

给出了交通灯控制器的VH DL 源程序和仿真结果。

仿真结果表明该系统的设计方案正确。

展示了VH DL 语言的强大功能和优秀特性。

关键词:交通灯控制器;电子设计自动化;硬件描述语言;可编程器件中图分类号:T N702 文献标识码:B 文章编号:1004373X(2007)0318702Design of Traffic Light Controller Based on VHDLZH AI Diantang,FANG Min,LI Guangwei(School of Cont rol Sci ence and Engineering,Ji nan Universi t y,Ji c nan,250022,China)A bstra ct :Tr affic light controller is usually developed by micr oprocessor or PLC.This paper introduces the design of t raffic light controller base on EDA,one im portant character istic of the EDA is that the design documents should be complet ed by the HDL,and it is widely used by electr onic designer now.The VH DL source progr ammer and simulating r esults of traffic light cont roller are given.T he simulating r esults show that the design met hod is corr ect,it shows the powerful function and excel 2lent char acter of the VHDL.Keywords :traff ic light controller;EDA;HDL;PLD收稿日期:20060706应用VH DL 语言设计数字系统,大部分设计工作可在计算机上完成,从而缩短系统开发时间,提高工作效率。

姓名:张九如学号:01071619VHDL简易红绿灯设计报告------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 15:10:09 06/09/2009-- Design Name:-- Module Name: myslef - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity myslef isPort ( RST : in STD_LOGIC;CLKIN : in STD_LOGIC;LIGHT : out STD_LOGIC_VECTOR (2 downto 0));end myslef;architecture Behavioral of myslef issignal CLK_DIV:STD_LOGIC:='0';signal CLK_DIV_REG:STD_LOGIC:='0';signal LIGHTN:STD_LOGIC_VECTOR (2 downto 0):="001";CONSTANT N:Integer:=25000000;CONSTANT P:Integer:=12;signal counter:Integer range 0 to N;signal counter1:Integer range 0 to P;beginprocess(RST,CLKIN,LIGHTN)beginLIGHT <= LIGHTN;IF rising_edge(CLKIN)THENIF(RST='1') thenCLK_DIV <='0';IF Counter=N thencounter<=0;CLK_DIV<=not CLK_DIV;elsecounter<=counter+1;end if;end if;end if;end process;process(CLKIN)beginif(CLKIN'EVENT AND CLKIN='1') thenCLK_DIV_REG <= CLK_DIV;end if;end process;process(RST,CLKIN)beginif(RST='0' AND rising_edge(CLKIN)) thenif((CLK_DIV='1') and (CLK_DIV_REG='0')) thencounter1<=counter1+1;if(counter1<=1)thenLIGHTN<="010";elsif(counter1<=6)thenLIGHTN<="100";elsif(counter1<=12)thenLIGHTN<="001";else counter1<=0;end if;end if;end if;end process;LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.all;USE ieee.numeric_std.ALL;ENTITY myslef_tb ISEND myslef_tb;ARCHITECTURE behavior OF myslef_tb IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT myslefPORT(RST : IN std_logic;CLKIN : IN std_logic;LIGHT : OUT std_logic_vector(2 downto 0));END COMPONENT;--Inputssignal RST : std_logic := '0';signal CLKIN : std_logic := '0';--Outputssignal LIGHT : std_logic_vector(2 downto 0);constant CLKIN_period :time := 20 ns;BEGIN-- Instantiate the Unit Under Test (UUT)uut: myslef PORT MAP (RST => RST,CLKIN => CLKIN,LIGHT => LIGHT);-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameCLKIN_process :processbeginCLKIN <= '0';wait for CLKIN_period/2;CLKIN <= '1';wait for CLKIN_period/2; end process;-- Stimulus processstim_proc: processbegin-- hold reset state for 100ms.RST<='1'after 200 ns;wait for 100ms;wait for CLKIN_period*10;-- insert stimulus herewait;end process;电路结构:工作流程:CLKIN脉冲时钟经过分频后激活触发器,触发器激活计数器计数,计数器为12进制计数器,当有不同计数值时,红绿黄灯分别亮起。

华中科技大学基于xilinx FPGA的VHDL交通灯控制器的设计--基于Spartan3E开发板专业:电子信息工程一. 任务设计要求①设计一个十字路口交通信号灯的定时控制电路。

要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,并将运行时间用数码管/液晶显示出来。

②绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为99秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由主干道转换为支干道时,主干道在通行时间只剩下5秒钟时,绿灯闪烁显示,支干道仍为红灯,以便主干道上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由支干道转换为主干道时,支干道绿灯闪烁显示5秒钟,主干道仍为红灯。

③对红、绿灯的运行时间要能比较方便的进行重新设置。

④对器件进行在系统编程和实验验证。

⑤用VHDL语言对设计进行描述,设计一个测试方案,通过ISE对设计进行仿真验证。

并能够下载到实验板上调试成功。

任务扩展:在原设计的基础上加入指示方向的功能。

二. 系统设计1.系统原理图与说明由系统设计原理图,我以清楚地将系统分为六个模块:分频模块,时间设置模块,状态转换模块,时间计算模块,LED流水灯模块,LCD显示模块。

1)分频模块分频模块其作用为:由于Spartan3E板上提供的时钟信号为50MHz,而设计所需时钟信号为1Hz,故使用分频模块将50MHz信号分频为1Hz信号。

2)时间置数模块由于任务设计要求可以对主干道,支干道上左转、绿灯运行的时间进行重新设置调整,所以要对系统进行参数化设计。

首先引入一组参数,main_gh,main_gl,main_lh,main_ll,branch_gh,branch_gl,branch_lh,branch_ll(下划线后面的字母分别取green,left,high,low首字母).需要置数时,首先选择对主干道还是支干道时间置数,这里设置一个main_or_branch参数,当main_or_branch为高时设置支干道时间,为低时设置主干道时间。

交通灯设计课程名称:学院专业姓名:学号:年级:任课教师:2011年9 月 5 日实验目的:1.熟悉quartus的使用,了解VHDL编程2.掌握逻辑电路的设计方法3.利用Quartus,使用VHDL语言编写一个交通灯的程序,使之可以实现红黄绿灯的交替出现,并在十字路口的另一条岔路上实现指挥的同步,完成交通指挥的功能。

实验基本原理:在假设时钟信号为1HZ的情况下,对路口的灯进行计时,每当时间到时转入下一个状态,开始新一轮的计时,一个十字路口的交通灯组合后有四种情况(绿,红)(黄,红)(红,绿)(红,黄),每个状态可对应一个时间。

在对每种状态编号后就可以开始状态的循环了。

实验内容:实验代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity traffic isport(clk: in std_logic;r1,y1,g1,r2,y2,g2:out std_logic --六个输出对应十字路口的六个红绿灯);end traffic;architecture act of traffic isconstant yellow_time:integer:=5;constant green_time:integer:=20; --不用定义红灯的时间,因为后面用不到.signal state:integer range 0 to 3; --这里有四种状态,用state来表示beginprocess(clk)beginif(clk'event and clk='1') thencase state is --用来展示这四种状态when 0=>r1<='0';y1<='0';g1<='1';r2<='1';y2<='0';g2<='0';when 1=>r1<='0';y1<='1';g1<='0';r2<='1';y2<='0';g2<='0';when 2=>r1<='1';y1<='0';g1<='0';r2<='0';y2<='0';g2<='1';when others=>r1<='1';y1<='0';g1<='0';r2<='0';y2<='1';g2<='0';end case;end if;end process;process(clk)variable count:integer range 0 to 25;beginif(clk'event and clk='1') thenif count=0 then --状态的循环if state=3 thenstate<=0;elsestate<=state+1;end if;case state iswhen 0=>count:=yellow_time; --选择状态对应的时间when 1=>count:=green_time;when 2=>count:=yellow_time;when others=>count:=green_time;end case;elsecount:=count-1; --状态的计时end if;end if;end process;end act;实验结果点击编译,可以看出没有出现错误设计出相应的波形文件并加载后,点击仿真,就可以出现如下的波形由时序仿真的结果可以看出,它实现了红绿灯的交替以及十字路口的两路灯的协调实验总结:此次实验做出的交通灯是建立在时钟频率为1HZ的基础上的,而硬件实验中提供的时钟信号一般都为几兆赫兹,因此如果这个实验想要下载到实验箱上去模拟的的话就需要在前面加上分频的代码,并将clk换成更改后的时钟通过实验的结果可以看出,在红绿灯稳定之前,有几秒钟的不稳定时期,这个是由于在设计是没有给变量赋给初值造成的,这在以后的设计中尤其需要注意,而在稳定后,功能实现较好,各时间段的衔接很顺畅,并且计时的时候用的是定义的常数green_time和yellow_time本实验中定义式25秒和5秒,这种做法可以方便以后的维护,修改起来也比较方便,并且使代码比较容易读懂。

基于VHDL语言的交通灯控制器设计2009年06 月18 日星期四20:38设计要求1、显示一个方向的绿、黄、红的指示状态。

2、特殊情况按键能实现特殊的功能,计数器停止计数并保持在原来的状态,显示红灯状态。

特殊后能继续计数.3、复位按键实现总体计数清零功能。

4、实现正常的倒计时功能. 用数码管作为倒计时显示, 显示时间为绿灯17s, 黄灯3s 红灯20s。

| ---------- >|--->| ------------ >|| 绿灯| 黄灯| 红灯|设计思想首先由晶振产生出发信号,由控制器处理成1HZ的时钟,利用此时钟进行计数,通过判断控制交通灯的亮灭。

通过每种灯亮的时间总数与计数值比较得到数码管应该显示的数值,利用分位分成十位和个位。

通过译码电路来实现数码管的显示。

本实验所使用的芯片为EPM7128SLS84-,6 实体逻辑单元为64 点,结构体逻辑单元为128 小型芯片。

软件本实验使用MAX+plus II 10 来进行程序的编写,编译,仿真以及下载。

在实验中发现其用,但仍有地方需要改进,不支持MOD取余运算。

(源程序)* 在MAX+plus II 中,汉字很容易出现乱码,建议大家用英文,这里为了考虑到读者的习惯写论文时都译成中文Library IEEE;Use IEEE.std_logic_1164.all;Entity redgreen isPort(clock_in:in std_logichold_state:instd_logic;reset_state:instd_logic,led_green ,led_yellow:out std_logic;led_redselect_en:buffer std_logic; select_display:out std_logic_vector(0 to 6)); end;Architecture half of redgreen isconstant loop_hz:integer:=800000; -- 一根据晶振实际频率算出来signal count_time:integer range 0 to loop_hz;signal clock_buffer:std_logic;signal clock_out:std_logic;signal count_num:integer range 0 to 40;signal display_num:integer range 0 to 20;signal display_shi:integer range 0 to 9;signal display_ge:integer range 0 to 9;constant loop_time:integer:=40; 个循环周期的时间constant red_time:integer:=20; -- 红灯的时间constant green_time:integer:=17; -- 绿灯的时间constant yellow_time:integer:=3; -- 黄灯的时间beginprocess(clock_in) -- 分频进程beginif rising_edge(clock_in) thenif count_time=loop_hz then count_time<=0; clock_buffer<=notclock_buffer;else count_time<=count_time+1;end if;end if; clock_out<=clock_buffer;-- 输入1HZ 的频率end process;process(reset_state ,clock_out) -- 计数进程beginif reset_state=1 then -- 重启后计数归零count_num<=0;elsif rising_edge(clock_out) thenif hold_state=1 then -- 紧急时计数占停count_num<=count_num;elseif count_num=loop_time-1 then count_num<=0;else count_num<=count_num+1;end if;end if;end if;end process;process(clock_out) -- 交通灯显示count countbeginnumnumif falling_edge(clock_in) thenif hold_state=1 then --led_red<=1;led_green<=0;led_yellow<=0;elseifelsifelseendif;占停时红灯亮display_num<=green_time-count_num;led_red<=0;led_green<=1;led_yellow<=0;display_num<=green_time+yellow_time-led_red<=0;led_green<=0;led_yellow<=1;display_num<=loop_time-count_num;led_red<=1;led_green<=0;led_yellow<=0;endif; end if;end process;process(display_num) -- 分位进程beginif display_num>=20 then display_shi<=2;display_ge<=display_num-20;elsif display_num>=10 thendisplay_shi<=1;display_ge<=display_num-10;elsedisplay_shi<=0;display_ge<=display_num;end if;end process;process(clock_in) -- 数码管显示beginif falling_edge(clock_in) thenselect_en<=1; -- 因为我们的实验箱采用数码管并联方式,所以显示case display_shi iswhen 0=>select_display<=1111110; when1=>select_display<=0110000; when 2=>select_display<=1101101; whenothers=>select_display<=0000000; end case;if select_en=1 then select_en<=0; case display_ge is when0=>select_display<=1111110; when 1=>select_display<=0110000; when2=>select_display<=1101101; when 3=>select_display<=1111001; when4=>select_display<=0110011; when 5=>select_display<=1011011; when6=>select_display<=1011111; when 7=>select_display<=1110000; when8=>select_display<=1111111; when 9=>select_display<=1110011; whenothers=>select_display<=0000000; end case;end if;end if;end process;end;-- 由于时间和硬件限制,这个程序仅仅实现了一路交通灯,用类似的方法可以写出两路交通灯的程library ieee;use ieee.std_logic_1164.all;entity redgreen isPort( clock_in:in std_logic; hold_state:in std_logic;reset_state:in std_logic;led_red,led_green,led_yellow:out std_logic; select_en:buffer std_logic; select_display:out std_logic_vector(0 to 6));end;architecture half of redgreen isbeginsignal count_time:integer range 0 to 800000;signal clock_buffer:std_logic;signal clock_out:std_logic;signal count_num:integer range 0 to 40;signal display_num:integer range 0 to 20; signal display_shi:integer range 0 to 9; signal display_ge:integer range 0 to 9; constantloop_time:integer:=50;constant red_time:integer:=25;constant green_time:integer:=20; constant yellow_time:integer:=5;begin process(clock_in)beginif rising_edge(clock_in)count_time<=0;clock_buffer<=not clock_buffer;count_time<=count_time+1;end if;end if;clock_out<=clock_buffer;end process;process(reset_state,clock_out)beginif reset_state=1then count_num<=0;elsif rising_edge(clock_out)then if hold_state=1then count_num<=count_num;else if count_num=loop_time-1then count_num<=0;else count_num<=count_num+1;end if;end if;thenif count_time=loop_hz then elseend if;end process;process(clock_out)beginif falling_edge(clock_in)then if hold_state=1thenled_red<=1;led_green<=0; led_yellow<=0;elseif count_numdisplay_num<=green_time-count_num;led_red<=0;led_green<=1;led_yellow<=0;elsif count_numdisplay_num<=green_time+yellow_time-count_num; led_red<=0;led_green<=0;led_yellow<=1;elsedisplay_num<=loop_time-count_num;led_red<=1;led_green<=0;led_yellow<=0;end if;end if;end if;end process;process(display_num)beginif display_num>=20then display_shi<=2;display_ge<=display_num-20;elsif display_num>=10then display_shi<=1;display_ge<=display_num-10;else display_shi<=0;display_ge<=display_num;end if;end process;process(clock_in)beginif falling_edge(clock_in)then select_en<=1;case display_shi iswhen 0=>select_display<=1111110;when 1=>select_display<=0110000;when 2=>select_display<=1101101;when others=>select_display<=0000000; end case;if select_en=1then select_en<=0;case display_ge iswhen 0=>select_display<=1111110;when 1=>select_display<=0110000;when 2=>select_display<=1101101;when 3=>select_display<=1111001;when 4=>select_display<=0110011;when 5=>select_display<=1011011;when 6=>select_display<=1011111;when 7=>select_display<=1110000;when 8=>select_display<=1111111;when 9=>select_display<=1110011;when others=>select_display<=0000000;end case; end if; end if;end process; end;end half;。

基于vhdl交通灯课程设计一、课程目标知识目标:1. 学生能理解并掌握VHDL语言的基本结构及其在交通灯控制系统中的应用;2. 学生能运用VHDL语言编写交通灯控制程序,实现对交通灯红、黄、绿灯亮灭时间的控制;3. 学生了解交通灯控制系统的工作原理,理解数字电路在实际应用中的重要性。

技能目标:1. 学生能够独立进行VHDL代码的编写,具备初步的编程能力;2. 学生通过课程设计实践,培养解决实际问题的能力,提高动手操作能力;3. 学生能够运用所学知识对交通灯控制系统进行调试和优化。

情感态度价值观目标:1. 学生在课程学习中,培养对电子信息技术专业的兴趣,激发学习热情;2. 学生通过团队合作完成课程设计,提高沟通与协作能力,增强团队意识;3. 学生认识到电子技术在现实生活中的应用,增强社会责任感和创新意识。

课程性质:本课程为电子信息技术专业高年级的专业课程设计,旨在通过实际操作,让学生将所学理论知识运用到实际项目中。

学生特点:学生已经掌握了VHDL语言的基本知识,具有一定的编程基础,对实际项目具有一定的兴趣和热情。

教学要求:结合学生特点和课程性质,注重实践操作,提高学生的动手能力和解决实际问题的能力。

在教学过程中,注重启发式教学,引导学生主动探索,培养学生的创新意识。

同时,关注学生的情感态度价值观培养,提高学生的综合素质。

通过分解课程目标,为后续教学设计和评估提供依据。

二、教学内容1. 交通灯控制系统原理介绍:讲解交通灯控制系统的工作原理,分析各个模块的功能及相互关系,使学生对交通灯控制系统有整体的认识。

相关教材章节:第三章 数字电路设计基础,第四节 交通灯控制系统原理。

2. VHDL语言基础回顾:回顾VHDL语言的基本结构、语法和常用语句,为后续编程打下基础。

相关教材章节:第二章 VHDL语言基础,全章。

3. 交通灯控制程序设计:详细讲解如何使用VHDL语言编写交通灯控制程序,包括红、黄、绿灯亮灭时间的设置。

福建农林大学计算机与信息学院信息工程类实验报告课程名称:VHDL数字系统设计姓名:系:电子信息工程专业:电子信息工程年级:2008级学号:指导教师:职称:2011 年6 月18 日实验项目列表福建农林大学计算机与信息学院信息工程类实验报告实验基于VHDL的交通控制灯设计1•实验目的和要求模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED作为交通信号灯,设计一个交通信号灯控制器。

基本要求:(a)信号灯分别由红、黄、绿三种颜色组成,运行时,绿灯亮40秒钟,然后闪5秒,绿灯灭,黄灯亮2秒,黄灯灭,红灯亮,同时另一方向的绿灯亮,红灯亮的时间为47秒。

扩展要求:(b)增加显示功能,即每个灯亮时显示相应的秒数并倒计时。

(c)增加左转功能,即信号灯由红灯、黄灯和两个绿灯组成,左转时间为15秒,红灯亮的时间调整为62秒。

2•实验原理或方案1.总体方案的设计:交通灯控制电路主要由以下几部分构成,如图 2.1所示,有电源电路,脉冲电路,分频电路,倒计时电路,(交通灯)状态控制电路,灯显示电路。

图2.1交通灯控制电路功能模块框图在某一十字路口交叉地带,可设置东西走向的道路为主道,南北走向的道路为次道,主次车道的交通灯需按交通法则交替运行。

2.总体设计电路图交通控制灯系统总体电路图3 •主要仪器设备1、 装有Altera 公司Max+plusU 仿真软件的计算机一台。

2、 选择 FPG/器件:Cyclone 中的 EP1C12Q240C83、 EDA-VI 实验箱一台。

4、 实现数据下载的数据线,导线。

5、 开关以及LED 灯。

6、 四位八段数码显示管。

4 •操作方法与实验步骤Max+plusH 开发工具是美国Altera 公司自行设计的一种软件工具,其使用方 法如下:(1) 建立和编写一个VHDL 语言的工程文件CLK-------- INPUT—VCC --OUTPUT C1 [KZCLK G1Y1 R1 L1L2 C2 Y2 R2inst9CNT45selkDOUT45M「 0EN45ADOUT45B[7 EN45B -instlOUTPUT Y1卜 二CD”OUTPU i^^^ L2OUTPUT Y2.OUTPU ^^ R2 XSKZinst4elk DOUT02M[7 EN02A EN02B inst3diV1elk3 elkouelkou 2i ist8SELTIMEDAOUT[y0]delednum[3..O] Ainst7Dfdeeode3 8SEL[2..0]Q[7.. 0]inst6OUTPUT Ar BTPUT C——=»OUTPUTEOUTPUT Q[7..0]EN45A EN45B EN02A EN02B EN15A EN15BCNT15sAIN45A[7..0] AIN45B[7..0]AIN15A[7..0]EN15ADOUT15B[7AIN15B[7..0]EN15BAIN02[7..0]inst2CNT02selk DOUT15M[: D O ITI 7TMD7OTDOUTM[7 DOUTB[7DOUT3[3..0] DOUT4[3..O] inst5BT U C DT U O D砂K2 碱T1[3..0]SEL [2.DOUT2[3..0]首先启动Max+plusU系统,启动后系统进入主菜单画面。

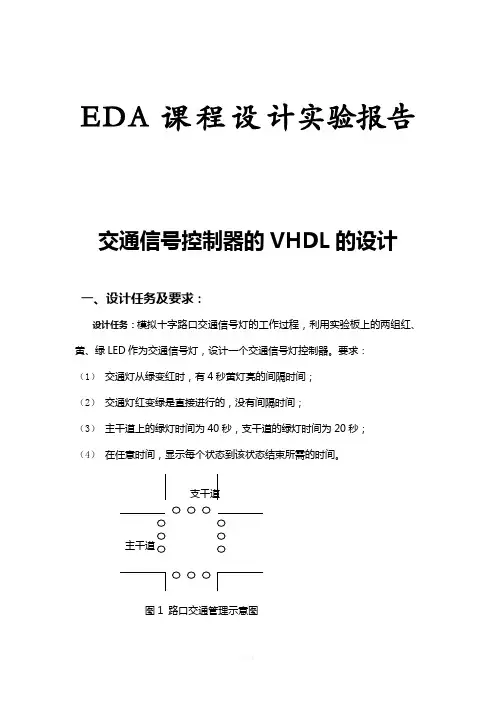

EDA课程设计实验报告交通信号控制器的VHDL的设计一、设计任务及要求:设计任务:模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED作为交通信号灯,设计一个交通信号灯控制器。

要求:(1)交通灯从绿变红时,有4秒黄灯亮的间隔时间;(2)交通灯红变绿是直接进行的,没有间隔时间;(3)主干道上的绿灯时间为40秒,支干道的绿灯时间为20秒;(4)在任意时间,显示每个状态到该状态结束所需的时间。

支干道主干道图1 路口交通管理示意图表1 交通信号灯的4种状态设计要求:(1)采用VHDL语言编写程序,并在QUARTUSII工具平台中进行仿真,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

二设计原理1、设计目的:学习DEA开发软件和QuartusII的使用方法,熟悉可编程逻辑器件的使用。

通过制作来了解交通灯控制系统,交通灯控制系统主要是实现城市十字交叉路口红绿灯的控制2’设计说明(1)第一模块:clk时钟秒脉冲发生电路在红绿灯交通信号系统中,大多数情况是通过自动控制的方式指挥交通的。

因此为了避免意外事件的发生,电路必须给一个稳定的时钟(clock)才能让系统正常运作。

模块说明:系统输入信号:Clk: 由外接信号发生器提供256的时钟信号;系统输出信号:full:产生每秒一个脉冲的信号;(2)第二模块:计数秒数选择电路计数电路最主要的功能就是记数负责显示倒数的计数值,对下一个模块提供状态转换信号。

模块说明:系统输入:full: 接收由clk电路的提供的1hz的时钟脉冲信号;系统输出信号:tm:产生显示电路状态转换信号tl:倒计数值秒数个位变化控制信号th:倒计数值秒数十位变化控制信号(3)第三模块:红绿灯状态转换电路本电路负责红绿灯的转换。

模块说明:系统输入信号:full: 接收由clk电路的提供的1hz的时钟脉冲信号;tm: 接收计数秒数选择电路状态转换信号;系统输出信号:comb_out: 负责红绿灯的状态显示。

北京XX大学《数字电路逻辑设计》实训报告基于VHDL语言的EDA设计——交通灯控制系统课程名称:数字电路逻辑设计课程实训学院:信息学院专业:电子信息工程姓名:班级:200908030301学号:2009080303132 2009080303101指导教师:成绩:2011年12 月22日目录目录 ................................................................................................................................................ - 1 - 概述 .. (1)第一章交通灯控制系统工程设计要求 (2)1、基础功能要求 (2)2、拓展功能要求 (2)第二章基础功能模块电路设计 (3)1、南北方向控制模块设计 (3)2、东西方向控制模块设计 (5)3、顶层设计 (8)第三章电路基础功能时序仿真验证 (9)1、南北方向控制模块功能仿真验证 (9)2、东西方向控制模块功能仿真验证 (9)3、顶层设计整体功能仿真验证 (10)第四章电路拓展功能设计 (11)1、“左转向”指示灯功能设计 (11)2、“左转向”指示功能设计 (12)附录 (13)附录1-小组成员与成员分工 (13)附录2-参考资料 (13)概述1、EDA技术的概念EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC 版图或PCB版图的整个过程的计算机上自动处理完成。

大连理工大学本科实验报告题目:十字路口交通灯控制系统课程名称:数字电路课程设计学院(系):电子信息与电气工程学部专业:班级:学生姓名:学号:完成日期:成绩:年月日题目:1 设计要求设计并调试好一个十字路口的交通灯控制系统,具体功能如下:(1).主干道、支干道方向分别有红、黄、绿指示灯以及两个显示数码管。

(2).当主干道方向允许通行亮绿灯时,支干道方向亮红灯,而支干道方向允许通行亮绿灯时,主干道方向亮红灯。

(3).工作顺序为支干道方向红灯亮40秒,前35秒支干道方向绿灯亮,后5秒黄灯亮。

然后主干道方向红灯亮20秒,前15秒支干道方向绿灯亮,后5秒黄灯亮。

(4).主干道和支干道的数码管分别以倒计时的方式显示该道路当前状态所剩余的时间。

2 设计分析及系统方案设计根据设计要求整个系统需要包括交通灯状态控制以及倒计时显示控制两部分,包括了计时器、交通灯状态转换控制器以及译码显示电路的设计。

交通等状态转换控制器用来控制交通灯的颜色转换;计时器用来产生交通灯状态转换的条件以及数码管倒计时所需显示的数据;译码显示电路用来控制数码管完成倒计时的功能。

交通灯控制流程图mg my mr sg sy sr1 0 0 0 0 10 1 0 0 0 10 0 1 1 0 00 0 1 0 1 03系统以及模块硬件电路设计下载时选择开发系统模式54 系统的VHDL设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity traffic isport(clk: in std_logic;mg,my,mr,sg,sy,sr: out std_logic;showmh: out std_logic_vector(3 downto 0);showml: out std_logic_vector(3 downto 0);showsh: out std_logic_vector(3 downto 0);showsl: out std_logic_vector(3 downto 0));end;architecture sys of traffic istype state is (a0,a1,a2,a3); --交通灯亮灭状态type mstate is (m0,m1,m2); --主干道显示状态type sstate is (s0,s1,s2); --支干道显示状态signal presents,nexts : state;signal mpresent,mnext : mstate;signal spresent,snext : sstate;signal ch35,mh35 : std_logic_vector(3 downto 0) :="0011";signal cl35,ml35 : std_logic_vector(3 downto 0) :="0100";--ch35(高位),cl35(低位)为交通灯状态计时信号(35s)--mh35(高位),ml35(低位)为主干道显示计时信号(35s) signal ch15,sh15 : std_logic_vector(3 downto 0) :="0001";signal cl15,sl15 : std_logic_vector(3 downto 0) :="0100";--ch15(高位),cl15(低位)为交通灯状态计时信号(15s)--sh15(高位),sl15(低位)为支干道显示计时信号(15s) signal cl5,sl5,ml5 : std_logic_vector(3 downto 0) :="0100";signal ch5,sh5,mh5 : std_logic_vector(3 downto 0) :="0000";--ch5(高位),cl5(低位)为交通灯状态计时信号(5s)--sh5(高位),sl5(低位)为支干道显示计时信号(5s)--mh5(高位),ml5(低位)为主干道显示计时信号(5s)signal sh40 : std_logic_vector(3 downto 0) :="0011";signal sl40 : std_logic_vector(3 downto 0) :="1001";--sh40(高位),sl40(低位)为支干道显示计时信号(40s) signal mh20 : std_logic_vector(3 downto 0) :="0001";signal ml20 : std_logic_vector(3 downto 0) :="1001";--mh20(高位),ml20(低位)为主干道显示计时信号(20s) signal sreach40,mreach20,mreach5,sreach5,mreach35 : std_logic:='0';sreach15,reach5,reach35,reach15 : std_logic:='0';--表示各计时信号计时一次结束的信号signal srst40,mrst20,mrst5,srst5,mrst35,srst15,rst5,rst35,rst15 : std_logic :='0';--将各计时信号重新置数的信号beginshift: process(clk) --状态转换beginif clk'event and clk='1' thenpresents<=nexts; --交通灯状态转换mpresent<=mnext; --主干道显示状态转换spresent<=snext; --支干道显示状态转换end if;end process;lightctrl: process(presents,reach35,reach15,reach5) --交通灯控制begincase presents iswhen a0 => mg<='1';my<='0';mr<='0';sg<='0';sy<='0';sr<='1';if reach35='1' then nexts<=a1;else nexts<=a0;rst35<='0';rst15<='1';rst5<='1';end if;--若reach35为1则转到a1状态,否则维持a0状态when a1 => mg<='0';my<='1';mr<='0';sg<='0';sy<='0';sr<='1';if reach5='1' then nexts<=a2;else nexts<=a1;rst35<='1';rst15<='1';rst5<='0';end if;--若reach5为1则转到a2状态,否则维持a1状态when a2 => mg<='0';my<='0';mr<='1';sg<='1';sy<='0';sr<='0';if reach15='1' then nexts<=a3;else nexts<=a2;rst35<='1';rst15<='0';rst5<='1';end if;--若reach15为1则转到a3状态,否则维持a2状态when a3 => mg<='0';my<='0';mr<='1';sg<='0';sy<='1';sr<='0';if reach5='1' then nexts<=a0;else nexts<=a3;rst35<='1';rst15<='1';rst5<='0';end if;--若reach5为1则转到a0状态,否则维持a3状态end case;end process;c35: process(clk,rst35) --35s交通灯状态计时beginif rst35='1' then ch35<="0011";cl35<="0100";elsif (clk'event and clk='1') thenif (cl35="0001" and ch35="0000") then reach35<='1';else reach35<='0';--计数到1时reach35置1,否则置0if cl35="0000" thenif ch35="0000" thench35<="0011";cl35<="0100";else cl35<="1001";ch35<=ch35-1;end if;else cl35<=cl35-1;end if;end if;end process;c15: process(clk,rst15) --15s交通灯状态计时beginif rst15='1' then ch15<="0001";cl15<="0100";elsif clk'event and clk='1' thenif (cl15="0001" and ch15="0000") then reach15<='1';else reach15<='0';end if;--计数到1时reach15置1,否则置0if cl15="0000" thenif ch15="0000" thenelse cl15<="1001";ch15<=ch15-1;end if;else cl15<=cl15-1;end if;end if;end process;c5: process(clk,rst5) --5s交通灯状态计时beginif rst5='1' then cl5<="0100";elsif clk'event and clk='1' thenif cl5="0001" then reach5<='1';else reach5<='0';--计数到1时reach5置1,否则置0cl5<=cl5-1;end if;end process;mcount: process(mpresent,mreach20,mreach35,mreach5) --主干道显示控制begincase mpresent iswhen m0 => mrst35<='0';mrst20<='1';mrst5<='1';showmh<=mh35;showml<=ml35;if mreach35='1' then mnext<=m1;else mnext<=m0;end if;--若mreach35为1则转到m1状态,否则维持m0状态when m1 => mrst35<='1';mrst20<='1';mrst5<='0';showmh<=mh5;showml<=ml5;if mreach5='1' then mnext<=m2;else mnext<=m1;end if;--若mreach5为1则转到m2状态,否则维持m1状态when m2 => mrst35<='1';mrst20<='0';mrst5<='1';showmh<=mh20;showml<=ml20;if mreach20='1' then mnext<=m0;else mnext<=m2;end if;--若mreach20为1则转到m0状态,否则维持m2状态end case;end process;m5: process(clk,mrst5) --5s主干道显示计时beginif mrst5='1' then ml5<="0100";mh5<="0000";elsif clk'event and clk='1' thenif ml5="0001" then mreach5<='1';else mreach5<='0';end if;--计数到1时mreach5置1,否则置0if ml5="0000" then ml5<="0100";else ml5<=ml5-1;end if;end if;end process;m20: process(clk,mrst20) --20s主干道显示计时beginif mrst20='1' then mh20<="0001";ml20<="1001";elsif clk'event and clk='1' thenif (ml20="0001" and mh20="0000") then mreach20<='1';else mreach20<='0';end if;--计数到1时mreach20置1,否则置0if ml20="0000" thenif mh20="0000" thenmh20<="0001";ml20<="1001";else ml20<="1001";mh20<=mh20-1;end if;else ml20<=ml20-1;end if;end if;end process;m35: process(clk,mrst35) --20s主干道显示计时beginif mrst35='1' then mh35<="0011";ml35<="0100";elsif (clk'event and clk='1') thenif (ml35="0001" and mh35="0000") then mreach35<='1';else mreach35<='0';end if;--计数到1时mreach35置1,否则置0if ml35="0000" thenif mh35="0000" thenmh35<="0011";ml35<="0100";else ml35<="1001";mh35<=mh35-1;end if;else ml35<=ml35-1;end if;end if;end process;scount: process(spresent,sreach40,sreach15,sreach5) --支干道显示控制begincase spresent iswhen s0 => srst40<='0';srst15<='1';srst5<='1';showsh<=sh40;showsl<=sl40;if sreach40='1' then snext<=s1;else snext<=s0;end if;--若sreach40为1则转到s1状态,否则维持s0状态when s1 => srst40<='1';srst15<='0';srst5<='1';showsh<=sh15;showsl<=sl15;if sreach15='1' then snext<=s2;else snext<=s1;end if;--若sreach15为1则转到s2状态,否则维持s1状态when s2 => srst40<='1';srst15<='1';srst5<='0';showsh<=sh5;showsl<=sl5;if sreach5='1' then snext<=s0;else snext<=s2;end if;--若sreach5为1则转到s0状态,否则维持s2状态end case;end process;s40: process(clk,srst40) --40s支干道显示计时beginif srst40='1' then sh40<="0011";sl40<="1001";elsif (clk'event and clk='1') thenif (sl40="0001" and sh40="0000") then sreach40<='1';else sreach40<='0';end if;--计数到1时sreach40置1,否则置0if sl40="0000" thenif sh40="0000" thensh40<="0011";sl40<="1001";else sl40<="1001";sh40<=sh40-1;end if;else sl40<=sl40-1;end if;end if;end process;s5: process(clk,srst5) --5s支干道显示计时beginif srst5='1' then sl5<="0100";sh5<="0000";elsif clk'event and clk='1' thenif sl5="0001" then sreach5<='1';else sreach5<='0';--计数到1时sreach5置1,否则置0end if;if sl5="0000" then sl5<="0100";else sl5<=sl5-1;end if;end if;end process;s15: process(clk,srst15) --15s支干道显示计时beginif srst15='1' then sh15<="0001";sl15<="0100";elsif clk'event and clk='1' thenif (sl15="0001" and sh15="0000") then sreach15<='1';else sreach15<='0';end if;--计数到1时sreach15置1,否则置0if sl15="0000" thenif sh15="0000" thensh15<="0001";sl15<="0100";else sl15<="1001";sh15<=sh15-1;end if;else sl15<=sl15-1;end if;end if;end process;end sys;5 结论以及结果说明采用GW48-CK开发系统,选用工作模式5,使用MAX+plus II软件调试环境,仿真过程中时钟周期设为200ns,仿真时间100us。

课程设计课程名称:交通灯设计.一、课程设计内容1.学习ALTERA公司的FPGA/CPLD的结构、特点和性能。

2.学习集成开发软件MAX+plus II/Quartus II的使用及设计过程。

3.熟悉EDA工具设计数字电路设计方法,掌握VHDL硬件描述语言设计方法。

4.根据给定题目设计数字电路,来加深对可编程逻辑器件的理解和掌握。

二、课程设计应完成的工作1.在所选择器件内完成交通灯控制器的设计,要求设计完成后芯片具有交通灯控制器的全部功能、包括显示和操作接口。

2.交通灯控制器要求控制十字路口两道路的交通灯,两道路交替通行,每次通行时间可设定20——60秒之间,每个路口要求有前行、禁止、人行灯。

(根据实际设计进度考虑可以增加左右转向灯,等待和通行时间显示等)。

3.撰写设计说明书一份(不少于2000字),阐述系统的工作原理,软、硬件设计方法,重点阐述软件思路。

说明书应包括封面、任务书、目录、摘要、正文、参考文献(资料)等内容,以及硬件电路综合图和软件程序清单等材料。

注:设计说明书题目字体用小三,黑体,正文字体用五号字,宋体,小标题用四号及小四,宋体,并用A4纸打印。

三、课程设计进程安排四、设计资料及参考文献1.康华光主编,《电子技术基础-数字部分》,高等教育出版社,1998。

2.谭会生等主编,《EDA技术及应用》,西安电子科技大学出版社,2001 3.潘松等主编,《EDA技术实用教程》,科学出版社,20064.雷伏容主编,《VHDL电路设计》,清华大学出版社,2006 5.Charles H.Roth等著,《数字系统设计与VHDL》,电子工业出版社,2008五、成绩评定综合以下因素:(1) 说明书及设计图纸的质量(占50%)。

(2) 独立工作能力及设计过程的表现(占30%)。

(3) 回答问题的情况(占20%)。

说明书和图纸部分评分分值分布如下:1、任务分析与设计思路(10分)要求说明设计任务的具体技术指标打算如何实现,根据实现各技术指标的解决方法,提出总体设计的思路和解决方案,说明其中关键问题及其解决办法。

《电子设计自动化(EDA)技术》课程实训报告题目: 交通信号控制器VHDL设计姓名:* *院系:应用技术学院专业:电子信息工程(仪器仪表)学号: ************ 指导教师:徐正坤2010 年6 月29 日目录1 课程设计题目、内容与要求…………………………………4页1.1 设计题目…………………………………………………4页1.2 设计内容…………………………………………………4页1.3 具体要求…………………………………………………4页2 系统设计………………………………………………………5页2.1 设计思路…………………………………………………5页2.2 系统原理…………………………………………………5页3 系统实现………………………………………………………5页3.1 VHDL源程序的具体程序和说明………………………5页3.2 交通信号控制器程序中使用到得信号及其对应的管脚…7页4 系统仿真………………………………………………………7页5 硬件验证(操作)说明………………………………………7页6 总结…………………………………………………………8页7 参考书目……………………………………………………8页交通灯控制器周晓重庆三峡学院应用技术学院电子信息工程(仪器仪表)2008级重庆万州 404000摘要基于VHDL的交通灯控制器设计,芯片采用ALTERA公司的ACEX1K 系列的EP1K10TC100-3,使用硬件描述语言VHDL进行描述,对交通灯进行模块化,在VHDL编程环境Quartus II下编译通过。

此报告对该设计的思想原理,详细程序和引脚配置以及波形仿真进行了详细的阐述。

关键词:VHDL 模块化交通灯设计1 课程设计题目、内容与要求1.1 设计题目交通信号控制器VHDL设计1.2 设计内容交通信号控制器的VHDL源程序;交通信号控制器的仿真波形;交通信号控制器的硬件测试结果。

可编程逻辑器件应用项目报告书项目名称:交通灯控制器指导老师:姓名:学号:班级:(以后写报告要包含以下一些内容:)一、设计要求--------------------------------------------------------------------------------二、设计目的--------------------------------------------------------------------------------三、设计方案--------------------------------------------------------------------------------四、设计程序---------------------------------------------------------------------------------五、管脚分配---------------------------------------------------------------------------------六、硬件下载实现现象描述------------------------------------------七、体会、对设计工作的总结与展-------------------------------------------一、设计要求:①在十字路口的两个方向上各设一组红、绿、黄灯,显示顺序为其中一方向(东西方向)是绿灯、黄灯、红灯;另一方向(南北方向)是红灯、绿灯、黄灯。

②设置一组数码管,以倒计时的方式显示允许通行或禁止通行的时间,其中绿灯、黄灯、红灯的持续时间分别是20s、5s和25s。

③当各条路上任意一条上出现特殊情况时,如当消防车、救护车或其他需要优先放行的车辆通过时,各方向上均是红灯亮,倒计时停止,且显示数字在闪烁。

当特殊运行状态结束后,控制器恢复原来状态,继续正常运行。

基于VHDL的交通信号灯设计曾辉,物理与电子信息工程学院摘 要:针对交通信号灯控制器的设计问题,采用层次化的设计方法,应用VHDL语言编制了可变多相位交通信号灯控制器的程序,并利用QuartusⅡ进行了仿真。

仿真结果表明:该系统可分别实现2、3、4相位交通信号灯控制,并且各相位的灯时分配能方便地通过设定输入进行调节,增强了系统的灵活性和适用范围。

关键字:交通信号灯,VHDL,设计, 多相位Design and simulation of traffic signal lamp circuitbased on VHDLZengHui,College of Physics and Electronic Information Abstract:To the design problem of traffic light controller ,the program of controller with VHDL is given and simulated by MAXPLUS Ⅱby using bierarchical design means. The simulation results show that the system could realize two phase. Three phase and four phase traffic light control, and light time of each phase could be changed by setting input value ,the adaptability of the system can be increased by changing the phase ang light time of traffic light ,I tab,6 figs 10 refs.Key words: traffic light,VHDL,design,multi phase引 言:随着城市的不断发展,城市交通的需求量快速加大,交通信号灯的数量急速加大,目前很多城市的交通信号灯还是应用传统的电路设计一旦交通信号灯出现故障不能及时维修和处理势必会造成道路的交通混乱.传统的交通信号灯控制电路的设计是基于中小规模集成电路电路元件多焊接复杂故障率高可靠性低而且控制系统的功能扩展及调试都需要硬件电路的支持为日常维护和管理增加了难度.为了更好地实现交通畅通不断优化交通信号灯的智能化管理通过采用EDA技术对交通信号灯控制电路进行改进,应用VHDL语言实现电路的设计和仿真消除了传统交通信号灯控制电路的弊端使交通信号灯控制电路的性能更稳定调试和维护更便捷。

基于VHDL的交通灯设计摘要随着社会上特别是城市中机动车辆保有量的不断增加,在现代城市的日常运行控制中,车辆的交通控制越来越重要,在十字交叉路口,越来越多的使用红绿灯进行交通指挥和管理。

本文以VHDL硬件描述语言为设计手段,完成了交通信号灯控制电路的设计,其中交通信号灯控制电路的开发目的是设计一个适用于主、支干道十字交叉路口的红黄绿交通灯的控制系统,通过合理设计系统功能,使红黄绿灯的转换有一个准确的时间间隔和转换顺序。

所设计的交通信号灯控制电路经过在QuartusⅡ 6.0软件下进行模拟仿真,观察其波形,证明所设计的交通信号灯控制电路完全可以实现预定的功能,并有一定的实用性。

关键词:FPGA; VHDL; QuartusⅡ; 交通灯一、设计思路本设计主要是利用状态机控制,交通灯的工作分成5个状态,如下:St0:支干道亮红灯,主干道亮绿灯,数码管不显示。

St1:主干道亮绿灯45秒,数码管显示45秒倒计时;支干道亮红灯,数码管显示从49秒倒计时到05秒。

St2::主干道亮黄灯5秒,数码管显示5秒倒计时;支干道亮红灯,数码管显示从04秒倒计时到00秒。

St3:支干道亮绿灯25秒,数码管显示25秒倒计时;主干道亮红灯,数码管显示从29秒倒计时到05秒。

St4:支干道亮黄灯5秒,数码管显示5秒倒计时;主干道亮红灯,数码管显示从04秒倒计时到00秒。

把交通灯的工作分成五个状态,则写程序的时候思路就比较清晰,只要在相应的状态里完成相应的工作,控制好黄绿红灯和数码管的倒计时显示,而且把握好五个状态转换的条件即可。

实现起来也方便。

二、设计分析根据设计思路可以把整体设计分为三个模块:1、分频模块:把实验板上的50MHz的频率分成1Hz信号(用于倒计时计数的时钟信号)、1kHz信号(用于数码管扫描显示的片选时钟信号)和2hz(用于黄灯的闪烁);2、交通灯控制以及倒计时(五个状态的控制)模块;3、数码管译码扫描显示模块。

基于VHDL语言的交通信号灯设计交通信号灯的设计是交通管理中非常重要的一环,通过合理的交通信号灯设计,可以提高道路交通的效率,并保证交通的安全性。

在本文中,将基于VHDL语言设计一个简单的交通信号灯系统,对信号灯进行控制。

首先,我们需要了解交通信号灯的基本原理。

一般情况下,交通信号灯通常分为红灯、黄灯和绿灯三个状态。

每个状态的时间长度可以根据实际情况进行调整。

在设计中,我们将考虑两个十字路口,每个十字路口设置一个交通信号灯。

接下来,我们将使用VHDL语言进行交通信号灯的设计。

首先定义一个信号类型,表示交通灯的三种状态:```vhdltype traffic_light_state is (red, yellow, green);```然后,定义信号灯实体,包括输入信号和输出信号:```vhdlentity traffic_light isportclk: in std_logic;reset: in std_logic;north_south_light: out traffic_light_state;east_west_light: out traffic_light_stateend traffic_light;```在实体中,我们使用了时钟clk和复位信号reset,以确保交通灯的状态按照预期进行转换。

north_south_light和east_west_light是输出信号,表示两个十字路口的交通信号灯状态。

接下来,我们定义信号灯行为。

在时钟上升沿或复位信号为高时,交通灯的状态会发生变化。

我们可以使用一个计数器和状态机来实现交通灯的控制。

当计数器达到一定值时,状态机将更新信号灯的状态。

```vhdlarchitecture behav of traffic_light issignal state: traffic_light_state := red;beginprocess(clk, reset)beginif reset = '1' thencounter <= 0;state <= red;elsif rising_edge(clk) thencounter <= counter + 1;case state iswhen red =>state <= green;counter <= 0;end if;when green =>state <= yellow;counter <= 0;end if;when yellow =>state <= red;counter <= 0;end if;end case;end if;end process;north_south_light <= state; east_west_light <= state; end behav;```最后,我们需要在顶层模块中实例化交通信号灯实体,并提供时钟和复位信号。

课程设计课程名称:交通灯设计.学院:电气工程学院专业:测仪姓名:学号:年级:级任课教师:2012年 1月12日电气工程学院课程设计任务书课题名称:交通灯控制器的设计专业、班级:测控技术与仪器测仪班指导教师:20 年1 月2 日至20 年1 月13 日共2周指导教师签名:教研室主任签名:分管院长签名:一、课程设计内容1.学习ALTERA公司的FPGA/CPLD的结构、特点和性能。

2.学习集成开发软件MAX+plus II/Quartus II的使用及设计过程。

3.熟悉EDA工具设计数字电路设计方法,掌握VHDL硬件描述语言设计方法。

4.根据给定题目设计数字电路,来加深对可编程逻辑器件的理解和掌握。

二、课程设计应完成的工作1.在所选择器件内完成交通灯控制器的设计,要求设计完成后芯片具有交通灯控制器的全部功能、包括显示和操作接口。

2.交通灯控制器要求控制十字路口两道路的交通灯,两道路交替通行,每次通行时间可设定20——60秒之间,每个路口要求有前行、禁止、人行灯。

(根据实际设计进度考虑可以增加左右转向灯,等待和通行时间显示等)。

3.撰写设计说明书一份(不少于2000字),阐述系统的工作原理,软、硬件设计方法,重点阐述软件思路。

说明书应包括封面、任务书、目录、摘要、正文、参考文献(资料)等内容,以及硬件电路综合图和软件程序清单等材料。

注:设计说明书题目字体用小三,黑体,正文字体用五号字,宋体,小标题用四号及小四,宋体,并用A4纸打印。

三、课程设计进程安排四、设计资料及参考文献1.康华光主编,《电子技术基础-数字部分》,高等教育出版社,1998。

2.谭会生等主编,《EDA技术及应用》,西安电子科技大学出版社,2001 3.潘松等主编,《EDA技术实用教程》,科学出版社,20064.雷伏容主编,《VHDL电路设计》,清华大学出版社,2006 5.Charles H.Roth等著,《数字系统设计与VHDL》,电子工业出版社,2008五、成绩评定综合以下因素:(1) 说明书及设计图纸的质量(占50%)。

(2) 独立工作能力及设计过程的表现(占30%)。

(3) 回答问题的情况(占20%)。

说明书和图纸部分评分分值分布如下:1、任务分析与设计思路(10分)要求说明设计任务的具体技术指标打算如何实现,根据实现各技术指标的解决方法,提出总体设计的思路和解决方案,说明其中关键问题及其解决办法。

2、详细设计(50分)根据总体设计完成下面任务:1)用Quartus 综合出电路原理图;(10分)2)列出芯片引脚分配并有注释;(10分)3)提供波形图并给出具体分析;(10分)4)提交程序清单,程序清单必须有详细注释。

(10分)六、其他说明1.课程设计需独立完成,每人必须提交课程设计说明书。

2.课程设计说明书内容不得雷同,雷同者本课程设计成绩一律不及格。

指导老师不负责甄别原创者与抄袭者。

正文目录一.摘要..........................二.设计思路........................三.设计过程........................1.分频模块div..................2.红绿的现实模块crosslight与crosslight2......3.计数兼译码模块.................4.模块连接图....................五.设计分析与总结.....................六.程序清单........................一、摘要EDA技术是以计算机为工具,根据硬件描述语言VHDL完成的设计文件,自动的完成逻辑编译,化简,分割,综合及优化,布局布线,仿真以及对特定目标芯片的适配编译和编程下载等工作.随着基于CPLD的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息,通信,自动控制用计算机等领域的重要性日益突出。

作为一个学习通信工程专业的学生,我们必须不断的了解更多的新产品信息,这就更加要求我们对EDA有个全面认识。

本程序设计的是基于VHDL的数字时钟,采用EDA 作为开发工具,VHDL语言为硬件描述语言,QUARTUSII作为程序的运行平台,所开发的程序经过调试运行,波形仿真验证,初步实现了设计目标。

本程序使用的硬件描述语言VHDL,可以大大降低了硬件数字系统设计的入门级别,让人感觉就是C语言的亲近。

通过本次的课程设计,不但使同学们进一步了解EDA技术在实际中的应用,也使同学们对EDA的综合应用有了更深一步的应用,这次的课程设计给同学们以后的学习与工作中有了一个全面的指导作用.典型的EDA工具中必须包含两个特殊的软件包,即综合器和适配器,综合器的功能就是将设计者在EDA平台上完成的针对某个系统项目的VHDL原理图或状态图形描述,针对给定的硬件系统组件,进行编译,优化,转换和综合,最终获得我们欲将实现的功能的描述文件。

综合器在工作前,必须给定要实现的硬件结构参数,它的功能就是将软件描述与给定的硬件结构用一定的方式联系起来,也就是说综合器是软件描述与硬件实现的一座桥梁。

综合过程就是将电路的高级语言描述转换成低级的,可与目标器件CPLD相映射的网表文件。

适配器的功能是将由综合器产生的网表文件配置与指定的目标器件中,产生最终的下载文件。

适配器所选的目标器件(CPLD芯片)必须包含于在综合器中已指定的目标器件系列。

硬件描述语言VHDL的英文全名是Very-High-Speed Integrated Circuit Hardware Description Language。

它主要用于描述数字系统的结构,行为,功能和接口。

除了还有很多硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似与一般的高级计算机语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体内外部分的概念是VHDL系统设计的基本点。

二、设计思路首先,既然是要用VHDL语言设计就必须得先学会VHDL语言,这是设计前必须的准备工作;其次,要求学会软件的仿真使用,此次设计中所用的软件工具是QUARTUSII 5.1;再者就是具体设计过程的构想了。

在车流不需交叉转弯的单十字路口可以仅用简单的四组的红、黄、绿灯来控制,其中两两相同。

假设一个十字路口有东西南北方向,则南北方向红、黄、绿灯时序完全相同,东西方向亦如此。

当南北方向为绿灯时东西方向为红灯,此时南北方向通行而东西方向禁止通行,同时来至东、西方的车辆均可以右转,但不能左转,这是此设计的最大不足。

当一个直通方向的红灯停止时为该直通方向的出发的车辆不与另一直通方向已经进入十字路交叉处但还为使出的车辆发生碰撞事故,必须设置黄灯等待指示作为缓冲。

即为红灯停了亮黄灯,黄灯停了亮绿灯,绿灯停了亮红灯,依次循环。

同时可以设置黄等2秒,绿灯20秒,红灯22秒。

采用模块化设计,先将各个功能模块设计调试成功之后再用例化语句将各个功能模块连接起来,即建立顶层模块。

三、设计过程1、分频模块div其功能就是根据所提供的晶振频率进行分频,以予驱动计数模块和红绿灯显示模块能,此模块可以通过改变软件的个别参数实现任意倍数的分频。

Clk接晶振,fpclk用于驱动后续模块,rst接复位信号,低电平复位。

2、红绿的显示模块crosslight与crosslight2用于对红绿灯的显示控制,分别控制两个直通方向的红绿灯,clk为时钟输入端,接分频模块的输出,rst1与rst0分别为复位信号输入端,高电平复位,greenlgt、yellowlgt、redlgt与greenlgt0、yellowlgt0、redlgt0 分别作为两个直通方向的绿灯黄灯和红灯的显示。

3、计数兼译码模块这六个模块均为计数模块,其输出直接为字形码,即兼备译码的功能。

具体原理为采用加计数器的方向显示,利用直接查表赋值的方法逐一赋值,于是就可以实现正序的加一计数行成倒序的减一计数。

此六个模块的功能实现原理完全一致,EN02 EN20 EN22 ENe02 ENe20 ENe22即为复位输入端,低电平复位。

右端均为输出端,输出与七段显示码对应的字型码可以直接驱动数码管。

4、模块连接图通过顶层模块的例化语句连接得到此图(输入端口)(输出端口)四、仿真波形图中第一个为分频器时钟输入,第二到七个信号为红绿灯的输出信号,以下为计数输出,计数输出全为字型码,可直接驱动七段数码管显示,例如图中的“1111110”为十进制“0”的字型码。

五、设计分析与总结本次课程设计的程序的设计和调试都花了我不少精力,虽然结果并不如意但至少最后还是仿真陈功了,而且通过本次课程设计是我进一步加深了对VHDL硬件描述语言的理解及其运用,VHDL描述数字电路系统设计的行为、功能、输入和输出,它在语法上与现代编程语言相似,但包含了许多与硬件有特殊关系的结构。

VHDL将一个设计称为一个实体Entity(元件、电路或者系统),并且将它分成外部的可见部分(实体名、连接)和内部的隐藏部分(实体算法、实现)。

当定义了一个设计的实体之后,其他实体可以利用该实体,也可以开发一个实体库。

所以,内部和外部的概念对系统设计的VHDL是十分重要的。

外部的实体名或连接由实体声明Entity来描述。

而内部的实体算法或实现则由结构体Architecture来描述。

结构体可以包含相连的多个进程process或者组建component等其他并行结构。

在此过程中,程序的反复调试简直让人想哭,有时候就仅仅是一个标点符号的错误都会花费大量的时间,特别是顶层模块的调用,一不小心就错误一大堆。

不过尽管感觉这次设计好难,但这也可以作为一次宝贵的人生体验,可以加强独立学习的能力,也许有同学会觉得快毕业了就没必要学习了但我不这样认为,我以前没学好是现在更应该抓住着大学剩下的短短时间。

尽管很累,但我觉得很值得,谢谢老师给予我这个“累”的机会。

六、程序清单(由于六个计数兼显示模块设计思想完全一致,在注释部分仅对前面两个模块进行注释)--顶层模块,完成各个功能模块的链接LIBRARY IEEE;--主程序库说明部分USE IEEE.Std_Logic_1164.ALL;ENTITY yintong IS--实体说明port( rst0,rst1,rst,clk: in std_logic;yellowlgt,greenlgt,redlgt: out std_logic;greenlgt0,yellowlgt0,redlgt0: out std_logic;DOUT02M: out std_logic_vector(6 downto 0);DOUTe02M:out std_logic_vector(6 downto 0);DOUT22M,DOUT22B:out std_logic_vector(6 downto 0);DOUT20M,DOUT20B:out std_logic_vector(6 downto 0);DOUTe20M,DOUTe20B:out std_logic_vector(6 downto 0);DOUTe22M,DOUTe22B:out std_logic_vector(6 downto 0));end yintong;architecture tong of yintong is--结构体说明component div--分频模块引用port( rst: in std_logic;clk: in std_logic;fpclk: out std_logic);end component;component crosslight2-- 一直通方向红绿灯显示模块引用port(clk: in std_logic;rst1: in std_logic;greenlgt: out std_logic;yellowlgt: out std_logic;redlgt: out std_logic);end component;component crosslight-- 另一直通方向的红绿灯显示模块引用port(clk: in std_logic;rst0: in std_logic;greenlgt0: out std_logic;yellowlgt0: out std_logic;redlgt0: out std_logic);end component;component cnt02s-- 一直通方向的黄灯显示模块引用port(clk,EN02B:in std_logic;DOUT02M:out std_logic_vector(6 downto 0));end component;component cnte02s-- 另一直通方向的黄的显示模块引用port(clk,ENe02B:in std_logic;DOUTe02M:out std_logic_vector(6 downto 0));end component;component CNT22s-- 一直通方向的红灯显示模块引用port(clk,EN22A:in std_logic;DOUT22M,DOUT22B:out std_logic_vector(6 downto 0)); end component;component CNT20s-- 一直通方向的绿灯显示模块引用port(clk,EN20A:in std_logic;DOUT20M,DOUT20B:out std_logic_vector(6 downto 0)); end component;component CNTe20s-- 另一直通方向的绿灯显示模块引用port(clk,ENe20A:in std_logic;DOUTe20M,DOUTe20B:out std_logic_vector(6 downto 0)); end component;component CNTe22s-- 另一直通方向的红灯显示模块引用port(clk,ENe22A:in std_logic;DOUTe22M,DOUTe22B:out std_logic_vector(6 downto 0)); end component;signal o1:std_logic;-- 信号量的定义signal yl:std_logic; -- 信号量的定义signal eyl:std_logic; -- 信号量的定义signal rl:std_logic; -- 信号量的定义下同signal erl:std_logic;signal gl:std_logic;signal egl:std_logic;beginu1:div port map(rst,clk,o1);-- 位置映射方法完成信号连接下同u2:crosslight port map(o1,rst1,egl,eyl,erl);u3:crosslight2 port map(o1,rst0,gl,yl,rl);u4:cnt02s port map(o1,yl,DOUT02M);u5:cnt22s port map(o1,rl,DOUT22M,DOUT22B);u6:CNT20s port map(o1,gl,DOUT20M,DOUT20B);u7:cnte02s port map(o1,eyl,DOUTe02M);u8:CNTe20s port map(o1,egl,DOUTe20M,DOUTe20B);u9:cnte22s port map(o1,rl,DOUTe22M,DOUTe22B);yellowlgt<=yl;-- 赋值输出下同yellowlgt0<=eyl;redlgt<=rl;greenlgt<=gl;greenlgt0<=egl;redlgt0<=erl;end tong;-- 顶层模块结束--分频模块library ieee;-- 库说明use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div is-- 实体说明port( rst: in std_logic;clk: in std_logic;fpclk: out std_logic);end div;architecture arc of div is-- 结构体说明beginprocess(clk)-- 并行进程语句variable count: integer range 0 to 1000000000;-- 定义允许分频为0到--1000000000 variable clk0: std_logic;beginif rst='0' then -- rst为低电平时复位clk0:='0' ;elsif clk'event and clk='1' thenif count=1000 thenclk0:=not clk0;count:=0; --上升沿敏感,定义1000分频elsecount:=count+1;end if;end if;fpclk<=clk0;end process;end arc;--一方向红绿灯显示模块library ieee;-- 库说明use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity crosslight is-- 实体说明generic(yellow:integer:=2;-- 定义黄灯显示时间green:integer:=20;-- 定义绿灯显示时间red:integer:=22-- 定义红灯显示时间);port(clk: in std_logic;rst0: in std_logic;greenlgt0: out std_logic;yellowlgt0: out std_logic;redlgt0: out std_logic);end crosslight;architecture a of crosslight is-- 结构体说明type states is (st0,st1,st2);signal state :states;signal cnt : integer;signal cnt_end: std_logic;beginprocess(rst0,clk) -- 并行进程语句实现红绿灯信号输入beginif(rst0='1')then-- 定义高电平复位state<=st0; cnt<=0;elsif(rising_edge(clk))thenif(cnt_end='1')thencnt<=cnt+1;-- 计数加一else cnt<=0;end if;case state iswhen st0=>if(cnt=green)thenstate<=st1;else state<=st0;end if;when st1=>if(cnt=yellow)thenstate<=st2;else state<=st1;end if;when st2=>if (cnt=red)thenstate<=st0;else state<=st2;end if;end case;end if;end process;process (state) -- 并行进程语句实现红绿灯信号输出begincase state is when st0=> yellowlgt0<='1'; greenlgt0<='0'; redlgt0<='0';cnt_end<='1';if(cnt=green)then cnt_end<='0';end if;when st1=> yellowlgt0<='0'; greenlgt0<='1'; redlgt0<='0';cnt_end<='1';if(cnt=yellow)then cnt_end<='0';end if;when st2=> yellowlgt0<='0'; greenlgt0<='0'; redlgt0<='1';cnt_end<='1';if(cnt=red)then cnt_end<='0';end if;end case;end process;end a;--另一方向红绿灯显示模块library ieee; -- 库说明use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity crosslight2 is-- 实体说明generic(green:integer:=20; -- 定义绿灯显示时间yellow:integer:=2; -- 定义黄灯显示时间red:integer:=22-- 定义红灯显示时间);port(clk: in std_logic;rst1: in std_logic;greenlgt: out std_logic;yellowlgt: out std_logic;redlgt: out std_logic);end crosslight2;architecture a of crosslight2 is-- 结构体说明type states is (st0,st1,st2);signal state :states;signal cnt : integer;signal cnt_end: std_logic;beginprocess(rst1,clk) -- 并行进程语句实现红绿灯信号输入beginif(rst1='1')thenstate<=st0; cnt<=0;-- 复位elsif(rising_edge(clk))thenif(cnt_end='1')thencnt<=cnt+1;else cnt<=0;end if;case state iswhen st0=>if(cnt=red)thenstate<=st1;else state<=st0;end if;when st1=>if(cnt=yellow)thenstate<=st2;else state<=st1;end if;when st2=>if (cnt= green)thenstate<=st0;else state<=st2;end if;end case;end if;end process;process (state) -- 并行进程语句实现红绿灯信号输出begincase state iswhen st0=>redlgt<='1';yellowlgt<='0';greenlgt<='0';cnt_end<='1';if(cnt=red)thencnt_end<='0';end if;when st1=>redlgt<='0';yellowlgt<='1';greenlgt<='0';cnt_end<='1';if(cnt=yellow)thencnt_end<='0';end if;when st2=>redlgt<='0';yellowlgt<='0';greenlgt<='1';cnt_end<='1';if(cnt= green)thencnt_end<='0';end if;end case;end process;end a;--一方向两秒计数及显示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNT02s is-- 实体说明port(clk,EN02B:in std_logic;DOUT02M:out std_logic_vector(6 downto 0));--定义七位输出end entity CNT02s;architecture art of CNT02s issignal CNT2B:std_logic_vector(1 downto 0);beginprocess(clk,EN02B)isbeginif(clk'event and clk='1')then-- 上升沿计数if EN02B='1' then CNT2B<=CNT2B+1;-- 计数器加一ELSECNT2B<="01";end if;end if;end process;process(CNT2B) isbeginCASE CNT2B isWHEN"00"=>DOUT02M<="0111110";-- 字型码输出WHEN"01"=>DOUT02M<="1111110";-- 字型码输出WHEN OTHERS=>DOUT02M<="1111110";-- 字型码输出END CASE;END PROCESS;END ARCHITECTURE ART;--二十二秒计数兼显示模块,正序计时倒序输出use ieee.std_logic_1164.all;-- 库说明use ieee.std_logic_unsigned.all;entity CNT22s is-- 实体说明port(clk,EN22A:in std_logic;DOUT22M,DOUT22B:out std_logic_vector(6 downto 0));--定义高位和地位字型码的输出end entity CNT22s;architecture art of CNT22s is-- 结构体说明signal CNT6B:std_logic_vector(4 downto 0);-- 5位计数beginlibrary ieee;process(clk,EN22A)is-- 正序计数并行进程语句beginif(clk'event and clk='1')thenif EN22A='1' then CNT6B<=CNT6B+1;-- 上升沿计数 EN22A为低电平时复位 ELSECNT6B<="10110";end if;end if;End process;Process(CNT6B) is-- 倒序字型码输出beginCASE CNT6B isWHEN"10110"=>DOUT22M<="1111110";DOUT22B<="1111110";--字型码倒序输出下同WHEN"10101"=>DOUT22M<="1111110";DOUT22B<="0110000"; WHEN"10100"=>DOUT22M<="1111110";DOUT22B<="1101101";WHEN"10011"=>DOUT22M<="1111110";DOUT22B<="1111001"; WHEN"10010"=>DOUT22M<="1111110";DOUT22B<="0110011"; WHEN"10001"=>DOUT22M<="1111110";DOUT22B<="1011011"; WHEN"10000"=>DOUT22M<="1111110";DOUT22B<="1011111"; WHEN"01111"=>DOUT22M<="1111110";DOUT22B<="1110010"; WHEN"01110"=>DOUT22M<="1111110";DOUT22B<="1111111"; WHEN"01101"=>DOUT22M<="1111110";DOUT22B<="1111011"; WHEN"01100"=>DOUT22M<="0110000";DOUT22B<="1111110"; WHEN"01011"=>DOUT22M<="0110000";DOUT22B<="0110000"; WHEN"01010"=>DOUT22M<="0110000";DOUT22B<="1101101"; WHEN"01001"=>DOUT22M<="0110000";DOUT22B<="1111001"; WHEN"01000"=>DOUT22M<="0110000";DOUT22B<="0110011"; WHEN"00111"=>DOUT22M<="0110000";DOUT22B<="1011011"; WHEN"00110"=>DOUT22M<="0110000";DOUT22B<="1011111"; WHEN"00101"=>DOUT22M<="0110000";DOUT22B<="1110010"; WHEN"00100"=>DOUT22M<="0110000";DOUT22B<="1111111"; WHEN"00011"=>DOUT22M<="0110000";DOUT22B<="1111011"; WHEN"00010"=>DOUT22M<="1101101";DOUT22B<="1111110"; WHEN"00001"=>DOUT22M<="1101101";DOUT22B<="0110000"; WHEN"00000"=>DOUT22M<="1101101";DOUT22B<="1101101"; WHEN OTHERS=>DOUT22M<="1111110";DOUT22B<="1111110";END CASE;END PROCESS;END ARCHITECTURE ART;--二十秒计数兼显示模块,其余注释同上library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNT20s isport(clk,EN20A,EN20B:in std_logic;DOUT20M,DOUT20B:out std_logic_vector(6 downto 0)); end entity CNT20s;architecture art of CNT20s issignal CNT6B:std_logic_vector(4 downto 0);beginprocess(clk,EN20A,EN20B)isbeginif(clk'event and clk='1')thenif EN20A='1' then CNT6B<=CNT6B+1;ELSEcNT6B<="10100";end if;end if;end process;process(CNT6B) isbegincASE CNT6B iswHEN"10100"=>DOUT20M<="1111110";DOUT20B<="1111110"; wHEN"10011"=>DOUT20M<="1111110";DOUT20B<="0110000"; wHEN"10010"=>DOUT20M<="1111110";DOUT20B<="1101101"; wHEN"10001"=>DOUT20M<="1111110";DOUT20B<="1111001"; wHEN"10000"=>DOUT20M<="1111110";DOUT20B<="0110011"; wHEN"01111"=>DOUT20M<="1111110";DOUT20B<="1011011"; wHEN"01110"=>DOUT20M<="1111110";DOUT20B<="1011111"; wHEN"01101"=>DOUT20M<="1111110";DOUT20B<="1110010"; wHEN"01100"=>DOUT20M<="1111110";DOUT20B<="1111111";wHEN"01011"=>DOUT20M<="1111110";DOUT20B<="1111011"; wHEN"01010"=>DOUT20M<="0110000";DOUT20B<="1111110"; wHEN"01001"=>DOUT20M<="0110000";DOUT20B<="0110000"; wHEN"01000"=>DOUT20M<="0110000";DOUT20B<="1101101"; wHEN"00111"=>DOUT20M<="0110000";DOUT20B<="1111001"; wHEN"00110"=>DOUT20M<="0110000";DOUT20B<="0110011"; wHEN"00101"=>DOUT20M<="0110000";DOUT20B<="1011011"; wHEN"00100"=>DOUT20M<="0110000";DOUT20B<="1011111"; wHEN"00011"=>DOUT20M<="0110000";DOUT20B<="1110010"; wHEN"00010"=>DOUT20M<="0110000";DOUT20B<="1111111"; wHEN"00001"=>DOUT20M<="0110000";DOUT20B<="1111011"; wHEN"00000"=>DOUT20M<="1101101";DOUT20B<="1111110"; WHEN OTHERS=>DOUT20M<="1111110";DOUT20B<="1111110"; END CASE;eND PROCESS;eND ARCHITECTURE ART;--两秒计数兼显示,其余注释同上library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNTe02s isport(clk,ENe02B:in std_logic;DOUTe02M:out std_logic_vector(6 downto 0)); end entity CNTe02s;architecture art of CNTe02s issignal CNTe2B:std_logic_vector(1 downto 0);beginprocess(clk,ENe02B)isbeginif(clk'event and clk='1')thenif ENe02B='1' then CNTe2B<=CNTe2B+1;ELSECNTe2B<="01";end if;end if;end process;process(CNTe2B) isbeginCASE CNTe2B isWHEN"01"=>DOUTe02M<="1111110";WHEN"00"=>DOUTe02M<="0110000";WHEN OTHERS=>DOUTe02M<="1111110";END CASE;END PROCESS;END ARCHITECTURE ART;--二十秒计数兼显示其余注释同上library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNTe20s isport(clk,ENe20A,ENe20B:in std_logic;DOUTe20M,DOUTe20B:out std_logic_vector(6 downto 0)); end entity CNTe20s;architecture art of CNTe20s issignal CNTe6B:std_logic_vector(4 downto 0);beginprocess(clk,ENe20A,ENe20B)isbeginif(clk'event and clk='1')thenif ENe20A='1' then CNTe6B<=CNTe6B+1;ELSEcNTe6B<="10100";end if;end if;end process;process(CNTe6B) isbegincASE CNTe6B iswHEN"10100"=>DOUTe20M<="1111110";DOUTe20B<="1111110"; wHEN"10011"=>DOUTe20M<="1111110";DOUTe20B<="0110000"; wHEN"10010"=>DOUTe20M<="1111110";DOUTe20B<="1101101"; wHEN"10001"=>DOUTe20M<="1111110";DOUTe20B<="1111001"; wHEN"10000"=>DOUTe20M<="1111110";DOUTe20B<="0110011"; wHEN"01111"=>DOUTe20M<="1111110";DOUTe20B<="1011011"; wHEN"01110"=>DOUTe20M<="1111110";DOUTe20B<="1011111"; wHEN"01101"=>DOUTe20M<="1111110";DOUTe20B<="1110010"; wHEN"01100"=>DOUTe20M<="1111110";DOUTe20B<="1111111"; wHEN"01011"=>DOUTe20M<="1111110";DOUTe20B<="1111011"; wHEN"01010"=>DOUTe20M<="0110000";DOUTe20B<="1111110"; wHEN"01001"=>DOUTe20M<="0110000";DOUTe20B<="0110000"; wHEN"01000"=>DOUTe20M<="0110000";DOUTe20B<="1101101"; wHEN"00111"=>DOUTe20M<="0110000";DOUTe20B<="1111001"; wHEN"00110"=>DOUTe20M<="0110000";DOUTe20B<="0110011"; wHEN"00101"=>DOUTe20M<="0110000";DOUTe20B<="1011011";wHEN"00100"=>DOUTe20M<="0110000";DOUTe20B<="1011111"; wHEN"00011"=>DOUTe20M<="0110000";DOUTe20B<="1110010"; wHEN"00010"=>DOUTe20M<="0110000";DOUTe20B<="1111111"; wHEN"00001"=>DOUTe20M<="0110000";DOUTe20B<="1111011"; wHEN"00000"=>DOUTe20M<="1101101";DOUTe20B<="1111110";WHEN OTHERS=>DOUTe20M<="1111110";DOUTe20B<="1111110";END CASE;eND PROCESS;eND ARCHITECTURE ART;--二十二秒计数兼显示,其余注释同上library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNTe22s isport(clk,ENe22A:in std_logic;DOUTe22M,DOUTe22B:out std_logic_vector(6 downto 0)); end entity CNTe22s;architecture art of CNTe22s issignal CNTe6B:std_logic_vector(4 downto 0);beginprocess(clk,ENe22A)isbeginif(clk'event and clk='1')thenif ENe22A='1' then CNTe6B<=CNTe6B+1;ELSECNTe6B<="10110";end if;end if;End process;Process(CNTe6B) isbeginCASE CNTe6B isWHEN"10110"=>DOUTe22M<="1111110";DOUTe22B<="1111110"; WHEN"10101"=>DOUTe22M<="1111110";DOUTe22B<="0110000"; WHEN"10100"=>DOUTe22M<="1111110";DOUTe22B<="1101101"; WHEN"10011"=>DOUTe22M<="1111110";DOUTe22B<="1111001"; WHEN"10010"=>DOUTe22M<="1111110";DOUTe22B<="0110011"; WHEN"10001"=>DOUTe22M<="1111110";DOUTe22B<="1011011"; WHEN"10000"=>DOUTe22M<="1111110";DOUTe22B<="1011111"; WHEN"01111"=>DOUTe22M<="1111110";DOUTe22B<="1110010"; WHEN"01110"=>DOUTe22M<="1111110";DOUTe22B<="1111111"; WHEN"01101"=>DOUTe22M<="1111110";DOUTe22B<="1111011"; WHEN"01100"=>DOUTe22M<="0110000";DOUTe22B<="1111110"; WHEN"01011"=>DOUTe22M<="0110000";DOUTe22B<="0110000"; WHEN"01010"=>DOUTe22M<="0110000";DOUTe22B<="1101101"; WHEN"01001"=>DOUTe22M<="0110000";DOUTe22B<="1111001"; WHEN"01000"=>DOUTe22M<="0110000";DOUTe22B<="0110011"; WHEN"00111"=>DOUTe22M<="0110000";DOUTe22B<="1011011"; WHEN"00110"=>DOUTe22M<="0110000";DOUTe22B<="1011111"; WHEN"00101"=>DOUTe22M<="0110000";DOUTe22B<="1110010"; WHEN"00100"=>DOUTe22M<="0110000";DOUTe22B<="1111111"; WHEN"00011"=>DOUTe22M<="0110000";DOUTe22B<="1111011"; WHEN"00010"=>DOUTe22M<="1101101";DOUTe22B<="1111110"; WHEN"00001"=>DOUTe22M<="1101101";DOUTe22B<="0110000"; WHEN"00000"=>DOUTe22M<="1101101";DOUTe22B<="1101101"; WHEN OTHERS=>DOUTe22M<="1111110";DOUTe22B<="1111110";END CASE;END PROCESS;END ARCHITECTURE ART;。