VHDL与数字系统课程设计

- 格式:doc

- 大小:3.35 MB

- 文档页数:25

数字逻辑原理与VHDL设计课程设计一、课程设计背景数字逻辑原理与VHDL设计是数字集成电路设计专业中的一门重要基础课程,内容涵盖数字电路基础知识、组合逻辑电路设计、时序逻辑电路设计以及数字电路综合和优化等方面。

本课程设计旨在以实践为主,巩固和加深学生的理论知识,提高学生综合运用数字逻辑原理和VHDL语言进行数字电路设计的能力。

二、实验目的通过本次课程设计,要求学生对数字逻辑原理及其应用有更加深入的认识,并掌握以下专业能力:1.掌握数字逻辑电路的基本知识与方法,以及基于VHDL设计数字电路的基本步骤与方法;2.能够运用数字逻辑原理及VHDL语言进行简单数字电路的设计、仿真、综合和下载;3.能够独立进行数字电路设计并解决设计过程中遇到的问题。

三、实验设备和工具1.Xilinx Vivado软件,用于数字电路的综合和仿真;2.FPGA开发板,用于数字电路的下载和实现;3.电脑,用于Vivado软件的安装和使用。

四、实验内容和步骤实验一函数计算器的设计与实现实验目的通过设计一个函数计算器,深入理解组合逻辑电路的设计、实现和仿真过程,同时练习使用VHDL语言进行数字电路的编写、仿真和下载。

实验内容设计一个函数计算器,能够计算并显示四个前缀表达式,包括:–23 45–11 + 22 * 33–23 - 45 / 561./ 45 + 67 - 89其中,加减乘除的运算需要满足基本的优先级规则,即在没有括号的情况下,先乘除后加减。

实验步骤1.设计并编写函数计算器的VHDL代码,包括各种运算模块、数字选择器、显示器控制器等;2.在Vivado软件中进行仿真,验证函数计算器设计的正确性;3.将函数计算器设计综合成比特流文件,下载到FPGA开发板上进行实现和测试。

实验二五位计数器的设计与实现实验目的通过设计一个五位同步加法计数器,深入理解时序逻辑电路的原理、设计和实现过程,同时掌握VHDL语言对时序电路进行设计、仿真和下载的方法。

vhdl与数字系统课程设计一、课程目标知识目标:1. 学生能理解VHDL的基本语法和结构,掌握VHDL编程的基本方法。

2. 学生能运用VHDL语言设计简单的数字系统,如组合逻辑电路和时序逻辑电路。

3. 学生能理解数字系统的基本原理,掌握数字系统的设计方法和步骤。

技能目标:1. 学生能运用VHDL语言编写代码,实现特定功能的数字电路。

2. 学生能使用相关的EDA工具,如ModelSim进行VHDL代码的仿真和调试。

3. 学生能通过课程设计实践,培养解决实际问题的能力和团队协作能力。

情感态度价值观目标:1. 学生能培养对数字系统设计和VHDL编程的兴趣,激发创新思维和探索精神。

2. 学生在学习过程中,能树立正确的工程观念,注重实际应用和问题解决。

3. 学生能在团队合作中,学会互相尊重、沟通协作,培养良好的团队精神和职业素养。

课程性质分析:本课程为数字电路与系统相关专业的选修课程,旨在通过VHDL语言的学习,使学生掌握数字系统设计的基本方法和技能。

学生特点分析:学生已具备一定的电子电路基础知识,具有一定的编程能力和实践操作能力,但对VHDL语言和数字系统设计尚处于入门阶段。

教学要求:1. 结合课本内容,注重理论与实践相结合,提高学生的实际操作能力。

2. 通过课程设计,培养学生分析问题、解决问题的能力,增强学生的工程素养。

3. 注重激发学生的学习兴趣,引导学生主动探索,培养创新意识。

二、教学内容1. VHDL基础语法与结构- 数据类型与运算符- 顺序语句与并发语句- 子程序与程序包- 配置与库的运用2. 数字系统原理与设计方法- 组合逻辑电路设计- 时序逻辑电路设计- 数字系统层次化设计方法3. VHDL在数字系统设计中的应用- 代码编写规范与技巧- 仿真与调试方法- 常用数字电路的VHDL实现,如:编码器、译码器、计数器等4. 课程设计实践- 设计题目与要求- 团队协作与分工- 设计报告撰写与答辩教学大纲安排:第一周:VHDL基础语法与结构介绍第二周:数字系统原理与设计方法第三周:VHDL在数字系统设计中的应用第四周:课程设计实践与指导第五周:课程设计总结与评价教学内容关联教材:1. 《数字电路与系统》相关章节:组合逻辑电路、时序逻辑电路设计原理。

VHDL语言及其应用课程设计一、前言VHDL(VHSIC Hardware Description Language)是一种用于描述数字系统、芯片、电路板和系统级应用的硬件描述语言。

作为一种硬件描述语言,VHDL使用定义来描述设计,供计算机程序执行和仿真。

VHDL被认为是数字电子工程领域中最强大、最灵活的硬件描述语言之一。

在本次课程设计中,我们将通过VHDL语言来设计一个数字系统,从而理解和熟悉VHDL语言的应用以及数字系统的设计方法。

二、开发环境在我们进行VHDL语言开发之前,需要准备以下开发环境:•Vivado:Vivado是一款由Xilinx公司开发的集成开发环境(IDE),可用于设计数字系统的FPGA、ASIC和Soc(System on Chip)。

•VHDL仿真器:VHDL仿真器用于测试和仿真我们设计的数字系统,常用的VHDL仿真器有ModelSim等。

三、课程设计在本次课程设计中,我们将设计一个简单的数字系统,该系统可以对两个8位数字进行求和运算,并输出计算结果。

具体的设计过程如下:1.设计输入首先,我们需要定义输入信号的格式。

在本次设计中,我们需要两个8位的输入信号,因此输入信号的格式如下:entity Input_Output isport(A_In, B_In :in std_logic_vector(7downto0);Sum :out std_logic_vector(7downto0));end Input_Output;在上述代码中,我们使用标准逻辑向量来定义输入信号的格式,其中A_In和B_In是两个8位输入信号,Sum是输出结果。

2.计算过程接下来,我们需要进行计算过程的设计。

在本次设计中,我们将对输入信号进行加法运算,因此我们需要定义一个计算模块来实现这一功能。

由于VHDL是一种面向过程的语言,因此我们需要使用过程来实现计算过程:architecture Behavioral of Input_Output issignal sum_temp :unsigned(7downto0);beginadd_proc:process(A_In,B_In)beginsum_temp <=unsigned(A_In) +unsigned(B_In);end process add_proc;Sum <=std_logic_vector(sum_temp);end Behavioral;在上述代码中,我们首先定义一个sum_temp信号来存储计算结果,接下来使用一个过程来实现加法运算。

课程设计报告实践课题:VHDL与数字系统课程设计学生:XXX指导老师:XXX、XXX系别:电子信息与电气工程系专业:电子科学与技术班级:XXX学号:XXX一、设计任务用VHDL设计一个简单的处理器,并完成相关的仿真测试。

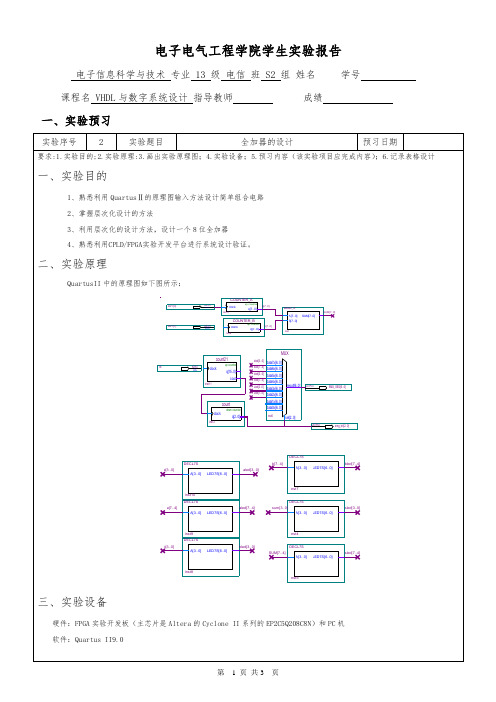

.设计要求:图1是一个处理器的原理图,它包含了一定数量的寄存器、一个复用器、一个加法/减法器(Addsub),一个计数器和一个控制单元。

图1 简单处理器的电路图数据传输实现过程:16位数据从DIN输入到系统中,可以通过复用器分配给R0~R7和A,复用器也允许数据从一个寄存器传通过Bus送到另外一个寄存器。

加法和减法的实现过程:复用器先将一个数据通过总线放到寄存器A中,然后将另一个数据放到总线上,加法/减法器对这两个数据进行运算,运算结果存入寄存器G中,G中的数据又可根据要求通过复用器转存到其他寄存器中。

1)Rx ←[Ry] :将寄存器Ry中的内容复制到Rx;2)Mvi Rx,#D :将立即数存入寄存器Rx中去。

所有指令都按9位编码(取自DIN的高9位)存储在指令存储器IR中,编编码规则为IIIXXXYYY,III表示指令,XXX表示Rx寄存器,YYY表示Ry寄存器。

立即数#D是在mvi指令存储到IR中之后,通过16位DIN输入的。

有一些指令,如加法指令和减法指令,需要在总线上多次传输数据,因此需要多个时钟周期才能完成。

控制单元使用了一个两位计数器来区分这些指令执行的每一个阶段。

当Run信号置位时,处理器开始执行DIN输时间指令T0T1T2T3(mv):I0(mvi):I1(add):I2(sub):I3IR inIR inIR inIR inRY out,RX in,DoneDIN out,RX in,DoneRX out,A inRX out,A in--------RY out,G in,AddsubRY out,G in,Addsub--------G out,RX in,DoneG out,RX in,Done二、实现功能说明2.1 mv Rx,Ry实现的功能:将寄存器Rx的值赋给寄存器Ry(以mv R0, R5为例)(1 )计数器为“00”时,指令寄存器的置位控制信号输入端IRin=1有效,将DIN输入的数据的高9位锁存。

VHDL 与数字系统设计总学时:48 理论学时:16 实验学时:32 课程总学分:3适用专业:电子信息科学与技术一、实验的地位、目的1、实验的地位本课程是电子信息科学与技术本科专业的专业方向课《VHDL与数字系统设计》的配套实验课程。

2、实验的目的使学生通过对VHDL语言及EDA技术的学习和训练,获得现代硬件数字电路的软件化设计方法,了解并初步掌握当代国际数字技术设计领域的最新技术;激发并调动学生创造性思维能力,为学生在数字技术领域的进一步深入探索和进行创新奠定基础。

二、实验教材与指导书《VHDL与数字系统设显示桌面.scf计》实验讲义,杨守良,重庆文理学院物理学与信息工程系,2005.7三、考核方式及成绩评定1、考核方式:平时考查2、成绩评定:根据实验报告、实验态度、考勤、实际操作技能检查等,对学生进行评定考核成绩,实验成绩的比例按规定执行。

2 -五、综合性、设计性实验简介实验四译码器的设计(设计性)(一)实验目的1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步掌握Max+PlusII 软件的基本操作与应用。

4、初步了解可编程器件的设计全过程。

(二)实验内容采用原理图输入法和VHDL编程来设计一个3-8译码器。

并在MAXPLUSII环境下实现仿真。

(三)主要仪器设备及器材PC 机、RC-EDA 实验开发系统、连接导线若干(四)基本实验技能及考核要点基本实验技能:熟悉3-8 译码器的逻辑真值表;基本门电路的使用考核要点:完成3-8 译码器的设计;并在MAX+PlusII 下进行仿真;在实验箱上验证设计。

实验五数字时钟设计(综合性)(一)实验目的1、多位计数器相连的设计方法。

2、掌握十进制,六进制,二十四进制计数器的设计方法。

3、继续巩固多位共阴极扫描显示数码管的驱动及编码。

4、掌握扬声器的驱动。

5、掌握CPLD 技术的层次化设计方法。

(二)实验内容设计的电子钟具有时、分、秒计数显示功能,以24 小时循环计时。

数字系统设计与VHDL第二版课程设计一、背景数字系统设计与VHDL是现代电子工程的基础课程之一,它涵盖了数字系统设计的基本概念和VHDL编程语言的基础应用。

随着技术的发展,数字系统的应用越来越广泛,因此这门课程也越来越受到重视。

二、课程设计目标本次课程设计旨在通过以下方式实现以下目标:1.帮助学生理解数字系统设计的基本概念和VHDL编程语言的基础应用。

2.培养学生的数字系统设计和VHDL编程的能力。

3.提高学生实际应用数字系统设计和VHDL编程的能力。

三、课程设计内容及要求1. 注册并安装软件学生需要注册并安装Xilinx ISE软件,这是一款常用的数字电路设计工具,提供VHDL编程支持,并带有原理图编辑器,布局和布线编辑器等工具。

2. 讲解和练习基本概念在课程开始之前,老师会进行讲解基本概念,如数字电路、逻辑门、布尔代数等。

学生需要掌握这些基本概念,以便后面的内容有更好的理解。

3. VHDL编程练习在学生掌握基本概念后,老师会安排VHDL编程练习。

这些练习旨在使学生熟悉VHDL编程语言,并为后续的数字电路设计打好基础。

4. 数字电路设计作业在完成VHDL编程练习后,老师会安排数字电路设计作业。

学生需要应用VHDL 编程,设计数字系统电路。

这些作业涉及到数字系统的各种应用场景,如闪动信号灯、递增/递减计数器等。

5. 实验课程课程的后半部分是实验课程,学生需要在实验室内完成一系列数字电路设计实验。

这些实验旨在应用之前学习到的知识,为学生提供实践的机会。

四、课程资源以下是一些课程资源,可供学生参考:1.VHDL编程视频教程:由国外的数字电路设计专家制作,介绍了VHDL的基本语法和编程技巧。

2.Xilinx ISE软件使用教程:详细地介绍了Xilinx ISE软件的功能和使用方法。

3.工程案例分享:老师会分享数字电路设计工程案例,为学生提供实践的参考。

五、总结数字系统设计与VHDL是一门重要的课程,它为学生提供了数字系统设计的基本概念和VHDL编程语言的基础应用。

数字逻辑与数字系统设计-基于VHDL语言描述课程设计简介数字逻辑与数字系统设计是计算机科学和工程中的一门重要课程,它涉及到硬件电路的设计和实现。

本文将介绍数字逻辑与数字系统设计中的VHDL语言描述,以及如何基于VHDL语言描述来进行数字系统的设计。

VHDL语言描述VHDL是一种硬件描述语言,它是IEEE标准1076的一部分,是一种文本描述数字电路、系统和信号的详细语言。

VHDL还可以描述模拟电路和数字信号处理系统。

VHDL的设计流程包括建立系统规范、编写代码、生成模拟和仿真。

编写代码可以通过三种不同的方法进行:•行为级描述:描述系统的功能,以及模块之间的交互;•数据流描述:根据输入变量的状态计算输出变量的状态;•结构描述:定义模块和信号的结构、层次结构和网表。

在VHDL中,模块和信号需要有一个基本的结构。

模块可以细分为实体(entity)和体枚(architecture),以及连接点(port)。

在体枚中,设计者可以通过描述行为来定义模块的内部结构,例如使用过程(process)、函数(function)、计数器(counter)等,从而描述模块的行为。

连接点则是模块的输入、输出接口,用于与其它模块连接,并且必须在实体中定义。

信号则是用于电路中传输数据、状态、时序等信息的实体。

它可以被定义为标量或向量,可以是定长或不定长。

在VHDL语言中使用变量(var)、常量(constant)和信号(signal)的方法可以对数字电路进行建模和仿真,并基于VHDL语言描述来进行数字系统的设计。

VHDL语言描述的应用——课程设计利用VHDL语言描述实现的数字电路在实际应用中非常广泛,可以用于网络交换芯片、信号处理器和数字嵌入式系统等领域。

在数字逻辑与数字系统设计中,也具有很高的实用性。

以一个简单的数字系统设计为例,该设计实现了数字加法器的功能,在VHDL 语言表述下的代码如下:-- 定义模块entity adder isport(A_i,B_i:in std_logic_vector(3downto0);S_o :out std_logic_vecotr(3downto0));end adder;-- 定义体枚architecture rtl of adder isbeginS_o <= A_i + B_i; -- 行为描述end rtl;在这个例子中,我们定义了一个模块adder,该模块由A_i和B_i两个输入端口、S_o一个输出端口组成。

课程设计报告实践课题:VHDL与数字系统课程设计学生:XXX指导老师:XXX、XXX系别:电子信息与电气工程系专业:电子科学与技术班级:XXX学号:XXX一、设计任务用VHDL设计一个简单的处理器,并完成相关的仿真测试。

.设计要求:图1是一个处理器的原理图,它包含了一定数量的寄存器、一个复用器、一个加法/减法器(Addsub),一个计数器和一个控制单元。

图1 简单处理器的电路图数据传输实现过程:16位数据从DIN输入到系统中,可以通过复用器分配给R0~R7和A,复用器也允许数据从一个寄存器传通过Bus送到另外一个寄存器。

加法和减法的实现过程:复用器先将一个数据通过总线放到寄存器A中,然后将另一个数据放到总线上,加法/减法器对这两个数据进行运算,运算结果存入寄存器G中,G中的数据又可根据要求通过复用器转存到其他寄存器中。

1)Rx ←[Ry] :将寄存器Ry中的内容复制到Rx;2)Mvi Rx,#D :将立即数存入寄存器Rx中去。

所有指令都按9位编码(取自DIN的高9位)存储在指令存储器IR中,编编码规则为IIIXXXYYY,III表示指令,XXX表示Rx寄存器,YYY表示Ry寄存器。

立即数#D是在mvi指令存储到IR中之后,通过16位DIN输入的。

有一些指令,如加法指令和减法指令,需要在总线上多次传输数据,因此需要多个时钟周期才能完成。

控制单元使用了一个两位计数器来区分这些指令执行的每一个阶段。

当Run信号置位时,处理器开始执行DIN输时间指令T0T1T2T3(mv):I0(mvi):I1(add):I2(sub):I3IR inIR inIR inIR inRY out,RX in,DoneDIN out,RX in,DoneRX out,A inRX out,A in--------RY out,G in,AddsubRY out,G in,Addsub--------G out,RX in,DoneG out,RX in,Done二、实现功能说明2.1 mv Rx,Ry实现的功能:将寄存器Rx的值赋给寄存器Ry(以mv R0, R5为例)(1 )计数器为“00”时,指令寄存器的置位控制信号输入端IRin=1有效,将DIN输入的数据的高9位锁存。

置位的控制信号如图3加粗黑线所示。

图3(2)计数器为“01”时,首先控制单元根据设计器为“00”时输入的指令,向复用器发出选通控制信号,复用器根据该控制信号让R5的值输出到总线上,然后控制单元控制寄存器R0将总线上的值锁存,完成整个寄存器对寄存器的赋值过程。

置位的控制信号和数据流如图4加粗黑线所示。

图42.2 mvi Rx,#D实现的功能:将的立即数#D赋给寄存器Rx(以mv R0, #D为例)(1)计数器为“00”时,指令寄存器的置位控制信号输入端IRin=1有效,将DIN输入的数据的高9位锁存。

置位的控制信号如图5加粗黑线所示。

图5(2)计数器为“01”时,首先控制单元根据设计器为“00”时输入的指令,向复用器发出选通控制信号,复用器根据该控制信号让DIN的值输出到总线上,然后控制单元控制寄存器R0将总线上的值锁存,完成整个立即数对寄存器的赋值过程。

置位的控制信号和数据流如图6加粗黑线所示。

图62.3 add Rx,Ry和sub Rx,Ry实现的功能:将寄存器Ry的值加上/减去寄存器Rx的值并赋给寄存器Rx(以add/sub R0,R1为例)。

(1)计数器为“00”时,指令寄存器的置位控制信号输入端IRin=1有效,将DIN输入的数据的高9位锁存。

置位的控制信号如图7加粗黑线所示。

图7(2)计数器为“01”时,首先控制单元根据设计器为“00”时输入的指令,向复用器发出选通控制信号,复用器根据该控制信号让R0的值输出到总线上,然后控制单元控制寄存器A将总线上的值锁存。

置位的控制信号和数据流如图8加粗黑线所示。

图8(3)计数器为“10”时,首先控制单元根据设计器为“00”时输入的指令,向复用器发出选通控制信号,复用器根据该控制信号让R1的值输出到总线上,然后控制单元控制加法/减法器addsub将寄存器A的值和总线上的值相加/相减并输出,接着寄存器G将加法/减法器addsub的计算结果锁存。

置位的控制信号和数据流如图9加粗黑线所示。

图9(4)计数器为“11”时,首先控制单元向复用器发出选通控制信号,复用器根据该控制信号让寄存器G的值输出到总线上,寄存器R0将总线上的值进行锁存,完成整个寄存器与对寄存器见加减法的运算过程。

置位的控制信号和数据流如图10加粗黑线所示。

图10三、单元模块设计说明4.1寄存器Registe寄存器R0~R7、寄存器A或寄存器G :用于数据的存储。

当时钟输入clk的上升沿到来且rin=1时,将数据输入端rxin[15..0]的数据锁存到寄存器中并从数据输出端rxout[15..0]输出;当rin=0时,输出端保持原来的值不变。

clkrinrxin[15..0]rxout[15..0]registeinst1寄存器Registe的VHDL代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY registe isport(clk:in std_logic;rin:in std_logic;rxin:in std_logic_vector(15 downto 0);rxout:out std_logic_vector(15 downto 0)); end entity registe;architecture one of registe isbeginprocess(clk)beginif clk'event and clk='1' thenif rin='1' then rxout<=rxin;end if;end if;end process;end one;4.2指令寄存器IR指令寄存器IR用于对输入的16为指令进行处理,取其高9位。

当时钟输入clk的上升沿到来且rin=1时,取数据输入端rxin[15..0]的高9位将其锁存到寄存器中并从数据输出端rxout[8..0]输出;当rin=0时,输出端保持原来的值不变。

指令寄存器IR的VHDL代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY IR isport(clk:in std_logic;rin:in std_logic;rxin:in std_logic_vector(15 downto 0);rxout:out std_logic_vector(8 downto 0));end entity IR;architecture one of IR isbeginprocess(clk)beginif clk'event and clk='1' thenif rin='1' then rxout<=rxin(15 downto 7);end if;end if;end process;end one;4.3加/减法器addsub加/减法器addsub用于处理两个输入的数据datain2[15..0] 和datain1[15..0],当控制端Addsub=1时,两个数据输入端datain2[15..0] 和datain1[15..0]相加并从数据输出端dataout[15..0]输出;当控制端Addsub=0时,数据输入端datain2[15..0] 减去datain1[15..0],结果从数据输出端dataout[15..0]输出。

加/减法器addsub的VHDL代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY addsub isport( ain:in std_logic_vector(15 downto 0);bin:in std_logic_vector(15 downto 0);adsub:in bit;about:out std_logic_vector(15 downto 0));end entity addsub;architecture one of addsub issignal a,b:std_logic_vector(15 downto 0);beginprocess(adsub,ain,bin)beginif adsub='0' then about<=ain+bin;elsif adsub='1' then about<=ain-bin;end if;end process;end one;4.4 计数器counter计数器counter用于产生控制单元的输入脉冲,对控制单元的工作时序进行控制。

当clear=0时(清零端clear 无效),时钟输入clk每来一个上升沿,输出count[1..0]加1,所以输出为00——>01——>10——>11——>00不断循环;当clear=1时(清零端clear有效),对输出Q[1..0]同步清零,与时钟有关。

计数器counter的VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk:in std_logic;clear:in std_logic;count:out std_logic_vector(1 downto 0));end counter;architecture one of counter issignal c:std_logic_vector(1 downto 0);beginprocess(clk,clear)beginif clk'event and clk='1' thenif(clear='1')then c<="00";else c<=c+1;end if;end if;end process;count<=c;end one;4.5 复用器multiplexers复用器根据控制单元的控制信号将指定的输入数据输出到总线上。

来自控制单元的控制信号为R0out~R7out、Gout、DINout,输入数据位来自寄存器R0~R7、寄存器A、数据输入端DIN,当控制信号的某一位为1时,将其对应的输入数据输出到总线上。