CPU时序资料

- 格式:ppt

- 大小:3.74 MB

- 文档页数:70

微机原理第2章8086/8088系统结构8086/8088 的工作时序1. 时钟周期、总线周期、指令周期微机原理时钟周期:是CPU的基本时间单位,记为T,其值为计算机主频的倒数。

微机原理时钟周期:是CPU 的基本时间单位,记为T ,其值为计算机主频的倒数。

总线周期:CPU 通过总线对存储器或I/O 进行1次访问所需要的时间。

它至少包含4个T ,记为T 1,T 2,T 3,T 4.1. 时钟周期、总线周期、指令周期1. 时钟周期、总线周期、指令周期微机原理的时间,它包含一个或多个总线周期。

常采用MIPS(Million Instructions Per Second)作单位。

微机原理(1) 8086读总线周期T 1T 2T3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/R DENA 15~A 02. 读/写工作时序微机原理(2) 8086写总线周期T 1T 2T 3T 4一个总线周期CLK A 19 ~ A 16S 6 ~ S 3A 19/S 6 ~ A 16/S 3DATA OUTAD 15 ~ AD 0ALE 高=I/O ,低=MM/IOWRDT/R DENA 15~A 0微机原理(3)8086具有等待状态的读总线周期T 1T 2T 3T W 一个总线周期CLK A 19~A 16A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/RDEN A 15~A 0T 4READYWAITREADYS 6~S 3微机原理(4) 8088读总线周期T 1T 2T 3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 7 ~ AD 0ALE 高=I/O ,低=MIO/MRD DT/R DENA 7~A 0A 15 ~ A 8A 15~A 8微机原理例1:在8088 CPU 中对存储器进行读操作时,CPU 引脚的IO/M 、RD 、WR 、DT/R 的输出电平分别是什么?例2:在若在1个总线周期中,插入了3个T W ,请问在该总线周期中对READY 信号进行了几次采样?低电平低电平高电平低电平4微机原理下次课见。

8086CPU系统、总线操作和时序8086CPU系统、总线操作和时序第⼀节 8086的引脚信号与功能回顾:8086/8088微型计算机的组成、结构及微机系统的⼯作过程,微机系统的存储器组织及相关概念。

本讲重点:8086/8088CPU的两种⼯作模式,8086/8088CPU的外部结构,即引脚信号及其功能。

讲授内容:⼀、 8086/8088微处理器⼯作模式及外部结构1.8086/8088CPU的两种⼯作模式为了适应各种使⽤场合,在设计8088/8086CPU芯⽚时,就考虑了其应能够使它⼯作在两种模式下,即最⼩模式与最⼤模式。

所谓最⼩模式,就是系统中只有⼀个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU 产⽣的,系统中的总线控制逻辑电路被减到最少,该模式适⽤于规模较⼩的微机应⽤系统。

最⼤模式是相对于最⼩模式⽽⾔的,最⼤模式⽤在中、⼤规模的微机应⽤系统中,在最⼤模式下,系统中⾄少包含两个微处理器,其中⼀个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器⼯作的。

与8088/8086CPU配合⼯作的协处理器有两类,⼀类是数值协处理器8087 另⼀类是输⼊/输出协处理器8089。

8087是⼀种专⽤于数值运算的协处理器,它能实现多种类型的数值运算,如⾼精度的整型和浮点型数值运算,超越函数(三⾓函数、对数函数)的计算等,这些运算若⽤软件的⽅法来实现,将耗费⼤量的机器时间。

换句话说,引⼊了8087协处理器,就是把软件功能硬件化,可以⼤⼤提⾼主处理器的运⾏速度。

8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有⼀套专门⽤于输⼊/输出操作的指令系统,但是8089⼜和DMA控制器不同,它可以直接为输⼊/输出设备服务,使主处理器不再承担这类⼯作。

所以,在系统中增加8089协处理器之后,会明显提⾼主处理器的效率,尤其是在输⼊/输出操作⽐较频繁的系统中。

第7章 8086CPU的总线操作与时序本章首先介绍了8086CPU的时钟周期、总线周期和指令周期的基本概念,然后详细介绍了基本的总线周期、主要总线操作及其总线周期,以及总线操作的时序问题,也即总线上有关信号的时间关系,这些对微机系统的设计和应用都是非常重要的。

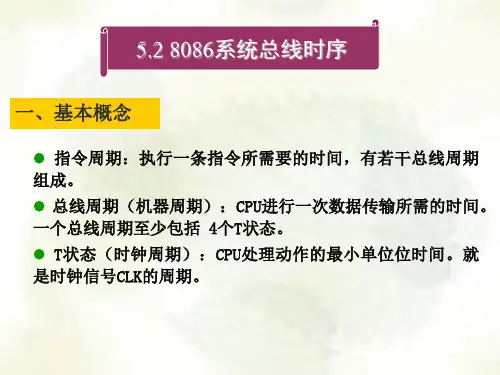

7.1 时钟周期、总线周期和指令周期8086CPU执行一条指令是由取指令、译码和执行等操作组成的,为了使8086CPU的各种操作协调同步进行,8086CPU必须在时钟信号CLK控制下工作,时钟信号是一个周期性的脉冲信号,一个时钟脉冲的时间长度称为一个时钟周期(Clock Cycle),是时钟频率(主频)的倒数,时钟周期是计算机系统中的时间基准,是计算机的一个重要性能指标,也是时序分析的刻度,8086的主频为5MHz,时钟周期为200ns,8086-1的主频为10MHz,时钟周期为100ns。

8086CPU要通过总线才能与外部交换信息,CPU通过总线接口单元与外部交换一次信息,称为一次总线操作,所耗用的时间称为一个总线周期(Bus Cycle),也称机器周期(Machine Cycle)。

一个总线周期由若干个时钟周期组成,总线操作的类型不同,总线周期也不同。

一个总线周期内完成的数据传输,一般有传送地址和传送数据两个过程。

8086CPU执行一条指令所需要的时间称为指令周期(Instruction Cycle),一个指令周期由若干个总线周期组成,不同指令的指令周期不是等长的,最短为一个总线周期,长的指令周期,如乘法指令周期,长达124个时钟周期。

7.2 系统的复位操作8086CPU的RESET引脚是用于系统复位的,可完成系统复位和启动操作,RESET信号由时钟发生器8284A接收外电路的复位请求信号进行同步整形处理后输入CPU,有效信号至少保持4个时钟周期,如果是冷启动,有效信号至少保持50us。

当CPU 检测到RESET 引脚上的上升沿时,就停止正在进行的所有操作,处于初始化状态,进行复位,直到RESET 信号变为低电平。

CPU读写时序参数1. 什么是CPU读写时序参数CPU读写时序参数是指CPU在进行读写操作时,所需的时序参数。

时序参数包括时钟周期、读写延迟、数据传输速率等。

这些参数决定了CPU读写操作的速度和性能。

2. 时钟周期时钟周期是CPU中最基本的时序参数之一。

它表示CPU中的一个时钟周期所占用的时间。

时钟周期通常以纳秒(ns)为单位表示。

时钟周期决定了CPU的工作速度,它越短,CPU的工作速度越快。

时钟周期的长度取决于CPU的设计和制造工艺。

现代CPU的时钟周期通常在几纳秒到几十纳秒之间。

3. 读写延迟读写延迟是CPU进行读写操作时所需的时间。

读写延迟包括地址传输延迟、数据传输延迟和刷新延迟等。

地址传输延迟是指CPU将地址信息传输到存储器或输入输出设备的延迟。

它取决于CPU与存储器或输入输出设备之间的物理连接和传输速率。

数据传输延迟是指CPU将数据传输到存储器或输入输出设备的延迟。

它取决于CPU与存储器或输入输出设备之间的数据传输速率和处理能力。

刷新延迟是指CPU对存储器进行刷新操作时所需的时间。

存储器刷新是为了保持存储器中的数据的稳定性和一致性。

刷新延迟取决于CPU与存储器之间的刷新机制和刷新频率。

4. 数据传输速率数据传输速率是CPU进行读写操作时的数据传输速度。

它表示CPU每秒钟能够传输的数据量。

数据传输速率取决于CPU与存储器或输入输出设备之间的数据传输带宽和传输效率。

数据传输带宽越大,传输效率越高,数据传输速率就越高。

数据传输速率对CPU的读写性能和响应速度有重要影响。

高数据传输速率可以提高CPU的读写性能和响应速度,使CPU能够更快地处理数据。

5. CPU读写时序参数的优化优化CPU读写时序参数可以提高CPU的读写性能和响应速度。

以下是一些优化CPU读写时序参数的方法:•提高时钟频率:增加时钟频率可以缩短时钟周期,提高CPU的工作速度。

•优化物理连接:优化CPU与存储器或输入输出设备之间的物理连接可以减小地址传输延迟和数据传输延迟。

时序控制计算机的工作过程是执行指令的过程。

一条指令的读取和执行过程常常需分成读取指令、读取源操作数、读取目的操作数、运算、存放结果等步骤。

这就需要一种时间划分的信号标志,如周期、节拍等。

同一条指令,在不同时间发送不同的微操作命令,做不同的事,其依据之一就是不同的周期、节拍信号。

CPU的许多操作都需要严格的定时控制,比如在规定的时刻将已经稳定的运算结果打入某个寄存器,这就需要定时控制的同步脉冲。

计算机系统中产生周期节拍、脉冲等时序信号的部件称为时序发生器。

对于时序发生器及时序的概念在前面第二章有专门的叙述。

下面着重叙述时序控制方式、多级时序的建立和典型的指令周期。

一、时序的概念计算机的时间控制称为时序。

指令系统中每条指令的操作均由一个微操作序列完成,这些微操作是在微操作控制信号控制下执行的。

即指令的执行过程是按时间顺序进行的,也即计算机的工作过程都是按时间顺序进行的。

时序控制方式分为同步控制和异步控制两大类。

(一)同步控制(1)时间分配同步控制的基本特征是将操作时间划分为许多时钟周期,周期长度固定,每个时钟周期完成一步操作。

CPU则按照统一的时钟周期来安排严格的指令执行时间表。

各项操作应在规定的时钟周期内完成,一个周期开始,一批操作就开始进行,该周期结束,这批操作也就结束。

各项操作之间的衔接取决于时钟周期的切换。

(2)同步定时有许多操作需要严格的同步定时。

时钟周期提供了加法运算的时间段,即时间分配。

同步打入脉冲则决定读入运算结果的时刻,即同不定时。

(3)各部件间的协调在一个CPU的内部,通常只有一组统一的时序信号系统,CPU内各部件间的传送也就由这组统一的时序信号同步控制。

(二)异步控制异步控制方式指操作按其需要选择不同的时间,不受统一的时钟周期的约束,各项操作之间衔接与各部件之间的信息交换采取应答方式。

二、指令周期多级时序的建立1.时序划分层次(1)指令周期读取并执行一条指令所需的时间称为一个指令周期。

第五讲8086/8088微处理器引脚功能、总线结构和时序第一节、8086/8088引脚信号和功能第二节、8086/8088最小模式和最大模式第三节、8086/8088主要操作第四节、8086存储器的分体结构第一节8086/8088引脚信号和功能一、8086/8088的两种工作模式二、8086/8088引脚信号和功能一、8086/8088的两种工作模式8086/8088CPU有两种模式:最小模式和最大模式。

y最小模式系统中只有8086/8088一个微处理器(单处理器模式)。

所有的总线控制信号都直接由8086/8088产生。

总线控制逻辑电路被减少到最小。

适合于较小规模的系统。

y最大模式包含两个(以上)微处理器,其中一个主处理器是8086/8088,其他的处理器称为协处理器,协助主处理器工作。

适合于中等规模或大型的8086/8088系统中。

系统的控制总线由总线控制器8288来提供:¾8288增强了8088CPU总线的驱动能力;¾将8086的状态信号(S2~S0)进行译码,提供8086对存储器、I/O接口进行控制所需的信号。

最小模式与最大模式的主要区别8086/8088外部引脚图(括号内为最大模式时引脚名)8088地A14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMI INTR CLK 地Vcc(5V)A15A16/S3A17/S4A18/S5A19/S6SS0(HIGH)MN/MX RDHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LOCK M/IO DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST READY RESETVcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086(1)地址/数据复用引脚(AD15~AD0 )是分时复用①在总线周期来输出要访问的存储器地址或口地址A15~A②在总线周期的其他时间内,作为双向数据总线:对8086就是(对8088地AD14AD13Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TESTREADYRESET8861.两种模式下公共引脚(2) 地址/状态复用引脚A19/S6~ A16/S3分时复用引脚,输出,三态。

南桥待机条件H5X系列•系统状态:G3:整个系统的电源均关闭S5:关机状态S4:休眠状态S3:睡眠状态S0:开机状态•信号解释•南卡待机条件VCCRTC:南桥RTC电路的供电,3V,给南桥内部的CMOS芯片(RAM)供电RTCRST#:南桥RTC电路的复位信号,3V,ICH9以后增加了一个RTC复位信号,名字是SRTCRST#32.768KHz:南桥得到了VCCRTC和RTCRST#后,给晶振供电,晶振起震,晶振两脚电压0.1V-0.5V之间V5REF_SUS:5V待机电压VCCSUS3_3:3.3V待机电压VCCSUS1_05:南桥内部产生给自己供电的1.05V,不用管RSMRST#:通知南桥3.3V待机电压正常,电压3.3V。

受控于外部电路SUSCLK:南桥收到RSMRST#后发出32L时钟,大多数老机器不采用,可以忽略,新机器发给ECPWRBTN#:POWER BUTTON,电源按钮,3.3V-0-3.3V脉冲信号,下降沿触发SLP_S5#:3.3V。

南桥退出关机状态的控制信号SLP_S4#:3.3V.南桥退出休眠状态的控制信号,(一般S5#和S4#只采用一个,用来控制产生内存供电一个空着SLP_S3#:3.3V,南桥退出睡眠状态的控制信号,(一般用来控制桥供电,总线供电、独显供电、CPU供电等VDIMM:内存供电南桥待机条件H6X系列•VCCRTC:从主板送给PCH桥的3V供电,给桥的RTC电路供电,以保存CMOS参数•INTRVMEN:桥的内部的浅睡眠待机电压1.05V-VCCSUS1_05 稳压器的开启信号,由VCCRTC上来•DSWVRMEN:桥的内部的深度睡眠待机电压1.05V—稳压器的开启信号,由VCCRTC上拉•RTCRST#/SRTCRST#:从主板送给桥的3V高电平,RTC电路的复位信号,从ICH9开启,有2个复位•32.768KHz:桥方便的32.768KHZ晶振,桥给晶振供电,晶振提供频率给桥•VCCSW3_3:主板给桥提供的深度睡眠唤醒电源(Deep Sleep Well),3.3V.不支持深度睡眠时,此电压与VCCSUS3_#连一起DPWROK:主板给桥的3.3V高电平,表示VCCDSW3_3的电源好,3.3V,不支持睡眠时,此信号与RSMRST#连一起•SLP_SUS#:深度睡眠状态指示信号,可用于开启S5状态的电压,比如VCCSUS3_3,不支持深度睡眠时,SLP_SUS#悬空•VCCSUS3_3#主板给桥的待机供电,3.3V 浅睡眠待机电压•BATLOW#:低电平时表示电池电量低,会导致不开机,一般由VCCSUS3_3上拉为高•RSMRST#:主板给桥的3.3V高电平的ACPI复位信号,意思是通知桥,此时待机电压已经OK •SUSCLK:桥发出的32.768KHZ的时钟,但不一定被主板采用南桥待机条件H6X系列•PWRBTN#:桥收到的下降沿触发信号,3.3V---0v---3.3v,通知桥可以退出睡眠状态•SLP_S5#:桥收到PWRBTN#后,置高SLP_S5#成3.3V,表示退出关机状态•SLP_S4#:桥置高SLP_S4#成3.3V,表示退出睡眠状态•SLP_S3#:桥置高SLP_S3#成3.3V,便是退出待机状态,进入S0开机状态•SLP_A#:桥发出的主动睡眠电路(Active Sleep Well)电源开启信号,用于开启ME模块供电,如果主板有ME固件,开启AMT功能,此信号会在触发前就产生,关闭AMT功能,此信号时序与SLP_S3#一致如果主板无ME固件,不知此后iAMT,ALP_SA#不采用•SLP_LAN#:LAN子系统休眠控制,控制网卡供电,支持网络唤醒,此信号待机时就为高,它不能比SLP_A#或SLP_S3#产生的更迟•VCCASW:主动睡眠电路的供电(ME模块),受控于SLP_A#,ALP_A#悬空时(主板无ME固件),VCCASW直接采用S0状态的供电•VDIMM:指内存供电,受控于SLP_S3#•PWROK:主板发给桥等S0状态的电压,受控于SLP_S3#发出两个•APWROK:主动睡眠电路电源好,开启AMT功能时,APWROK由AMT电压控制,关闭AMT功能时,APWROK与PWROK同步•DRAMPWROK:桥发给CPU的PG,通知CPU,内存模块供电OK南桥待机条件H6X系列•25MHz Crystal Osc: 6系列芯片组无时钟芯片,桥增加25M晶振,给桥内部的时钟模块提供基准率频率•需要读取BIOS:有问题会没有CPU供电•PCH Output Clocks:桥输出各组时钟•PROCRWRGD:桥发给CPU的PG,表示CPU的非核心电压OK•CPU SVID:CPU_SVID是由CPU发给CPU供电芯片的一组信号,由DATA和CLK组成的标准串行总线和一个起提示作用的ALERT#信号组成,用于控制CPU核心电压和集显供电•VCCCORE_COU:CPU核心供电•SYS_PWROK:由CPU的供电芯片发给桥的3.3V作为CPU复位•PLTRST#:桥发出的平台复位3.3V。