数字电路-第六章习题答案

- 格式:pdf

- 大小:61.53 KB

- 文档页数:4

第六章可编程逻辑器件PLD可编程逻辑器件PLD是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD包括只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2.按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device)芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD器件在结构上仍延续GAL的结构原理,因而还是电擦写、电编程的EPLD 器件。

第六章(选择、判断、填空共19题)一、选择题1.脉冲整形电路有。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.555定时器2.多谐振荡器可产生。

A.正弦波B.矩形脉冲C.三角波D.锯齿波3.石英晶体多谐振荡器的突出优点是。

A.速度高B.电路简单C.振荡频率稳定D.输出波形边沿陡峭4.T T L单定时器型号的最后几位数字为。

A.555B.556C.7555D.75565.555定时器可以组成。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器6.用555定时器组成施密特触发器,当输入控制端C O外接10V电压时,回差电压为。

A.3.33VB.5VC.6.66VD.10V7.以下各电路中,可以产生脉冲定时。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.石英晶体多谐振荡器二、判断题(正确打√,错误的打×)1.施密特触发器可用于将三角波变换成正弦波。

()2.施密特触发器有两个稳态。

()3.多谐振荡器的输出信号的周期与阻容元件的参数成正比。

()4.石英晶体多谐振荡器的振荡频率与电路中的R、C成正比。

()5.单稳态触发器的暂稳态时间与输入触发脉冲宽度成正比。

()6.单稳态触发器的暂稳态维持时间用t W表示,与电路中R C成正比。

()7.采用不可重触发单稳态触发器时,若在触发器进入暂稳态期间再次受到触发,输出脉宽可在此前暂稳态时间的基础上再展宽t W。

()8.施密特触发器的正向阈值电压一定大于负向阈值电压。

()三、填空题1.555定时器的最后数码为555的是产品,为7555的是产品。

2.施密特触发器具有现象,又称特性;单稳触发器最重要的参数为。

3.常见的脉冲产生电路有,常见的脉冲整形电路有、。

4.为了实现高的频率稳定度,常采用振荡器;单稳态触发器受到外触发时进入态。

答案一、选择题1.BC2.B3.C4.A5.ABC6.B7.B二、判断题1.×2.√ 3.√ 4.×5.×6.√7.×8.√三、填空题1.TTL CMOS2.回差电压滞后脉宽3.多谐振荡器单稳态触发器施密特触发器4.石英晶体暂稳态。

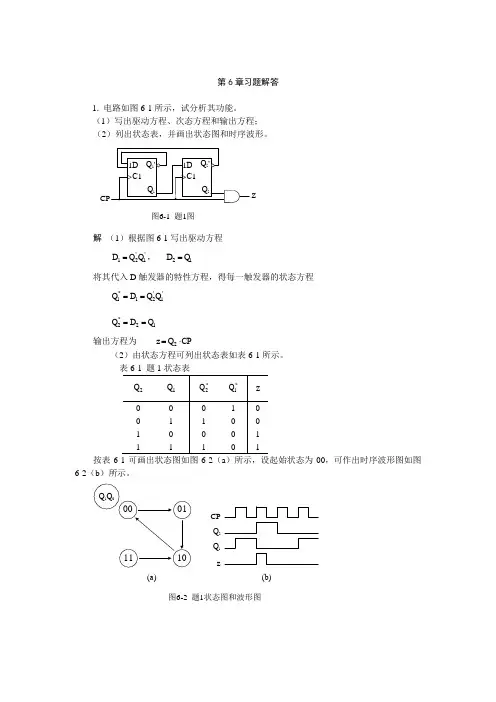

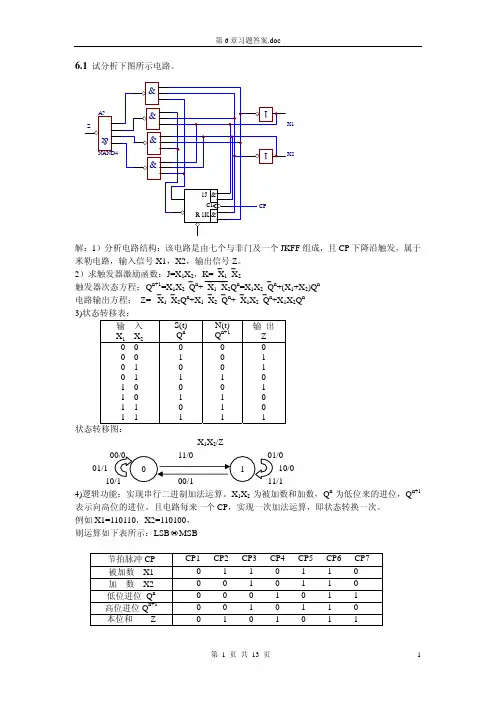

第6章习题解答1. 电路如图6-1所示,试分析其功能。

(1)写出驱动方程、次态方程和输出方程;(2)列出状态表,并画出状态图和时序波形。

图6-1 题1图z解 (1)根据图6-1写出驱动方程'1'21Q Q D =, 12Q D =将其代入D 触发器的特性方程,得每一触发器的状态方程'1'21*1Q Q D Q ==12*2Q D Q ==输出方程为 CP Q z ⋅=2(2)由状态方程可列出状态表如表6-1所示。

按表00,可作出时序波形图如图6-2(b )所示。

图6-2 题1状态图和波形图CP Q 2Q 1z(a )(b )2. 时序电路如图6-3所示。

(1)写出该电路的状态方程、输出方程;(2)列出状态表,画出状态图。

图6-3 题2图解 (1)驱动方程 x K J ==11 122xQ K J ==将其代入JK 触发器的特性方程,的状态方程21'21*21'1*1)'('Q xQ Q xQ Q Q x xQ Q +=+=输出方程 21Q xQ z =(2)假定一个现态,代入状态方程,得出对应的次态和输出状态,列表表示即得状态表,如表6-2所示。

由此算出状态图,如图6-4所示。

表6-2 题2状态表图6-4 题2的状态图3. 某计数器的输出波形如图6-5所示,试确定该计数器是模几计数器,并画出状态图。

图6-5 题3图CP Q A Q B QC解 由波形图画出状态图,Q C 为高位,Q A 为最低位。

010000001100011101Q C Q B Q A故该波形显示的计数器的计数模为六。

4. 分析如图6-6所示的同步时序电路。

图6-6 题4图解 (1)有题图得到各级触发器的驱动方程为⎪⎪⎩⎪⎪⎨⎧====34231242'3'11)'(Q D Q D Q D Q Q Q Q D(2)列出状态方程为⎪⎪⎩⎪⎪⎨⎧========34*423*312*242'3'11*1)'(Q D Q Q D Q Q D Q Q Q Q Q D Q由驱动方程和状态方程可以确定,该电路是移位寄存器型时序电路,其电路的状态转移决定于第一级的驱动信号。

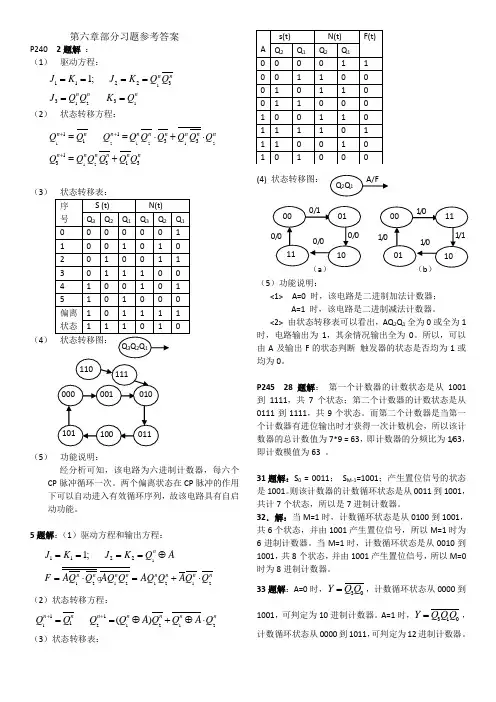

第六章部分习题参考答案 P240 2题解 : (1) 驱动方程:112111223331;n n nnnJ K J K Q Q J Q Q K Q ======(2) 状态转移方程:121212121113313313n n n n n n n n nn n n n n nQ Q Q Q Q Q Q Q Q Q Q Q Q Q Q +++==⋅+⋅=+(3)(4)(5) 功能说明:经分析可知,该电路为六进制计数器,每六个CP 脉冲循环一次。

两个偏离状态在CP 脉冲的作用下可以自动进入有效循环序列,故该电路具有自启动功能。

5题解:(1)驱动方程和输出方程:11212121211221;nnnnnnnnnJ K J K Q A F AQ Q AQ Q AQ Q AQ Q ====⊕=⋅=+⋅(2)状态转移方程: 121212111()n nn n n n n Q Q Q Q A Q Q A Q ++==⊕+⊕⋅(3)状态转移表:(4) 状态转移图:(5)功能说明:<1> A=0 时,该电路是二进制加法计数器;A=1 时,该电路是二进制减法计数器。

<2> 由状态转移表可以看出,AQ 2Q 1全为0或全为1时,电路输出为1,其余情况输出全为0。

所以,可以由A 及输出F 的状态判断 触发器的状态是否均为1或均为0。

P245 28题解: 第一个计数器的计数状态是从1001到1111,共7个状态;第二个计数器的计数状态是从0111到1111,共9个状态。

而第二个计数器是当第一个计数器有进位输出时才获得一次计数机会,所以该计数器的总计数值为7*9 = 63,即计数器的分频比为1/63,即计数模值为63 。

31题解:S 0 = 0011; S M-1=1001;产生置位信号的状态是1001。

则该计数器的计数循环状态是从0011到1001,共计7个状态,所以是7进制计数器。

32.解:当M=1时,计数循环状态是从0100到1001,共6个状态,并由1001产生置位信号,所以M=1时为6进制计数器。

数字电子技术基础第四版课后答案6第六章脉冲波形的产生和整形[题6.1]用施密特触发器能否寄存1位二值数据,说明理由。

[解]不能,因为施密特触发器不具备记忆功能。

[题6.2]在图P6.2(a)所示的施密特触发器电路中,已知R110k,R230kG1和G2为CMOS反相器,VDD=15V。

(1)试计算电路的正向阈值电压VT+、负向阈值电压VT-和回差电压△VT。

(2)若将图P6.2(b)给出的电压信号加到P6.2(a)电路的输入端,试画出输出电压的波形。

[解]R11015VT1VRTH1302V10V2(1)R11015VT1VRTH1302V5V2VTVTVT5V(2)见图A6.2。

[题6.3]图P6.3是用CMOS反相器接成的压控施密特触发器电路,试分析它的转换电平VT+、VT-以及回差电压△VT与控制电压VCO的关系。

,则根据叠加定理得到[解]设反相器G1输入端电压为IR2//R3R1//R3R1//R2VCO0R1R2//R3R3R1//R2R2R1//R3VTH时,IVT,因而得到(1)在I升高过程中00。

当升至IIIVTHVTR2//R3R1//R2VCOR1R2//R3R3R1//R2R1R1R1R1//R2R1R2//R3VTVTHVCOVTH1RVCORRRR//RR//R32331223 VTH时,IVT,于是可得(2)在I降低过程中0VDD。

当降至I VTHVTR2//R3R1//R3R1//R2VCOVDDR1R2//R3R3R1//R2R2R1//R3 R1//R3R1R2//R3R1//R2VVVCODDTHR3R1//R2R2R1//R3R2//R3VTR1R1R1VTH1RRRVCO323RRVTVTVT21VTH1VDDR2R2(3)(与VCO无关)根据以上分析可知,当Vco变小时,VT+和VT-均增大,但回差电压△VT不变。

[题6.4]在图P6.4施密特触发器电路中,若G1和G2为74LS系列与非门和反相器它们的阈值电压VTH=1.1V,R1=1KΩ,二极管的导通压降VD=0.7V,试计算电路的正向阈值电压VT+、负向阈值电压VT-和回差电压△VT。

第六章可编程逻辑器件PLD可编程逻辑器件PLD是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD包括只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2.按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device)芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD器件在结构上仍延续GAL的结构原理,因而还是电擦写、电编程的EPLD 器件。

A T V,、-、、/:第六章可编程逻辑器件PLD可编程逻辑器件PLD 是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC 芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD 器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD 基本结构可编程逻辑器件PLD 包括只读存储器ROM 、可编程只读存储器PROM 、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门” 两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD 的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1. 按编程部位分类PLD 有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2. 按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device )芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD 器件在结构上仍延续GAL 的结构原理,因而还是电擦写、电编程的EPLD 器件。

P6.1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_1 isport(clk:in std_logic;d_out:out std_logic_vector(5 downto 0)); end;architecture bhv of chp6_1 issignal count: std_logic_vector(5 downto 0); signal temp: std_logic_vector(5 downto 0); beginprocess(clk)beginif clk'event and clk='1' thencount<= count+1;if count="100000" then count<="000000";end if;end if;end process;process(clk)beginif clk'event and clk='0' thentemp<=temp+1;if temp="0111111" then temp<="000000"; end if;end if;end process;d_out<=count+temp;end;P6.3solution1library ieee;use ieee.std_logic_1164.all;entity chp6_3 isport(x:in std_Logic_vector(7 downto 1);y:out std_logic_vector(2 downto 0)); end;architecture bhv of chp6_3 isbeginprocess(x)beginif x(7)='1' then y<="111";elsif x(6)='1' then y<="110";elsif x(5)='1' then y<="101";elsif x(4)='1' then y<="100";elsif x(3)='1' then y<="011";elsif x(2)='1' then y<="010";elsif x(1)='1' then y<="001";else y<="000";end if;end process;end;solution2library ieee;use ieee.std_logic_1164.all;entity chp6_3_2 isgeneric(n:integer:=3);port(x:in std_logic_vector(2**n-1 downto 0);y:out integer range 0 to 2**n-1); end;architecture bhv of chp6_3_2 isbeginprocess(x)variable temp:integer range 0 to 2**n-1; beginfor i in x'range loopif x(i)='1' thentemp:=i;exit;end if;end loop;y<=temp;end process;end;P6.4library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_4 isgeneric (n:integer:=8);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_4 issignal rst:std_logic;signal temp:std_logic_vector(2 downto 0); beginprocess(clk,rst)beginif rst='1' thentemp<="000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;rst<='1' when temp="111" else'0';clk_out<=temp(2);end;P6.5library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_5 isgeneric (n:integer:=7);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_5 issignal temp:std_logic_vector(2 downto 0); signal cout:std_logic;beginprocess(clk)beginif clk'event and clk='1' thentemp<=temp+1;if temp="110" then temp<="000";end if;end if;end process;cout<='1' when temp="110" else'0';clk_out<=cout;end;P6.6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity chp6_6 isport(clk,start,stop,reset:in std_logic;dig1,dig2,dig3:out std_logic_vector(3 downto 0)); end;architecture bhv of chp6_6 issignal sec1:integer range 0 to 10;signal sec2:integer range 0 to 6;signal min:integer range 0 to 10;beginprocess(clk,start, stop,reset)variable count1:integer range 0 to 10;variable count2:integer range 0 to 6;variable count3:integer range 0 to 10;beginif reset='1' thencount1:=0;count2:=0;count3:=0;elsif clk'event and clk='1' thenif start='1' and stop='0' thencount1:=count1+1;if count1=10 thencount1:=0;count2:=count2+1;if count2=6 thencount2:=0;count3:=count3+1;if count3=10 thencount3:=0;end if;end if;end if;end if;end if;sec1<=count1;sec2<=count2;min<=count3;end process;dig1<=conv_std_logic_vector(sec1,4);dig2<=conv_std_logic_vector(sec2,4);dig3<=conv_std_logic_vector(min,4);end;P6.8use ieee.std_logic_1164.all;entity chp6_8 isgeneric(n:integer:=8);port(input:in std_logic_vector(n-1 downto 0);output:out std_logic);end;architecture bhv of chp6_8 isbeginprocess(input)variable temp:std_logic_vector(n-1 downto 0); begintemp(0):=input(0);for i in 1 to n-1 looptemp(i):=input(i) xor temp(i-1);end loop;output<=temp(n-1);end process;end;P6.9library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_9 isgeneric(n:integer:=4);port(input:std_logic_vector(n-1 downto 0);output:out integer range 0 to n);end;architecture bhv of chp6_9 isbeginprocess(input)variable temp:integer range 0 to n;begintemp:=0;for i in 0 to n-1 loopif input(i)='1' thentemp:=temp+1;end if;end loop;output<=temp;end process;end;P6.10use ieee.std_logic_1164.all;entity chp6_10 isgeneric(n:integer :=8);port(din:in integer range 0 to n-1;dout:out std_logic_vector(n-1 downto 0));end;architecture bhv of chp6_10 isbeginprocess(din)beginfor i in 0 to n-1 loopif din=i then dout<=(i=>'1', others=>'0');end if;end loop;end process;end;P6.16library ieee;use ieee.std_logic_1164.all;entity chp6_16 isgeneric (n:integer:=8);port(a,b:in std_logic_vector(n-1 downto 0);cin:in std_logic;s:out std_logic_vector(n-1 downto 0);cout:out std_logic);end;architecture bhv of chp6_16 issignal carry:std_logic_vector(n downto 0);beginprocess(a,b,cin,carry)begincarry(0)<=cin;for i in 0 to n-1 loops(i)<=a(i) xor b(i) xor carry(i);carry(i+1)<=(a(i) and b(i)) or (a(i) and carry(i)) or (b(i) and carry(i));end loop;cout<=carry(n);end process;end;说明:本次答案均为课上讨论过的,P6.11-P6.15均可参考第五章答案,可以利用对应语句将其放入进程中。

思考题与习题6-1已知图T6-1所示为施密特触发器输入信号u I 的波形,请对应画输出信号u O 的波形。

图T6-16-2 在如图6-14所示的单稳态触发器电路中,已知R=10k Ω、C=0.1μF ,G 1的输出 电阻可忽略不计,试估算输出波形u O 的脉冲宽度。

代入得,脉宽t w=0.7ms6-3图T6-3所示电路是用两个集成单稳态触发器74121构成的脉冲波形变换电路,试计算u O1和u O2输出脉冲的宽度,并画出对应于u I 的u O1和u O2波形。

图T6-3RCt w 7.06-4图T6-4所示电路为可控多谐振荡器,已知tW等于振荡器输出脉冲周期的5倍,请对应u k画u O1和u O2的波形。

图T6-46-5试构成一个如图6-23所示的RC环形振荡器电路,要求振荡器输出信号的频率为1kHZ ,请估算R和C的数值。

若要求振荡频率为1HZ,则R和C又该为多少?解:T≈2.2RC,f=1KHZ,则T=1ms,因此,当f=1KHZ时,RC=0.45ms;当f=1HZ 时,RC=0.45s。

6-6试用555定时器构成一个单稳态电路,要求输出脉冲幅度≥10V,输出脉冲宽度在1-10秒范围内连续可调。

解:根据题意,用555定时器设计得单稳态触发器取R1=22K,R2=18K,分压后输入端电压为6.75V(电源电压为15V),一般的,555定时器得输出高电平不低于其电源电压得90%,因此选15v.则UO输出脉宽t W=1.1RC设C=1000μF,则1≤1.1R×1000×10-6≤ 10 909≤R ≤9K6-7图T6-7是用两个555定时器接成的延迟报警器。

当开关S 断开后,经过一定的延 迟时间后扬声器开始发出声音。

如果在延迟时间内S 重新闭合,扬声器不会发出 声音。

在图中给定的参数下,试求延迟时间的具体数值和扬声器发出声音的频率。

图中的G 1是CMOS 反相器,电源电压为12V 。

6.2 试作出101序列检测器得状态图,该同步电路由一根输入线X ,一根输出线Z ,对应与输入序列的101的最后一个“1”,输出Z=1。

其余情况下输出为“0”。

(1) 101序列可以重叠,例如:X :010101101 Z :000101001 (2) 101序列不可以重叠,如:X :010******* Z :0001000010 解:1)S 0:起始状态,或收到101序列后重新开始检测。

S 1:收到序列起始位“1”。

S 2:收到序列前2位“10”。

10101…X/Z0/01/0X/Z11…100…2)10101…X/Z0/0X/Z11…100…6.3对下列原始状态表进行化简:(a)解:1)列隐含表:A B CDC B ×A B CD C B ×AD BC ××(a)(b)2)进行关联比较 所有的等价类为:AD ,BC 。

最大等价类为:AD ,BC ,重新命名为a,b 。

3)列最小化状态表为:a/1b/0bb/0a/0aX=1X=0N(t)/Z(t)S(t)(b)N (t )/Z (t )S (t )X=0 X=1A B/0 H/0B E/0 C/1C D/0 F/0D G/0 A/1E A/0 H/0F E/1 B/1G C/0 F/0H G/1 D/1解:1)画隐含表:2)进行关联比较:AC,BD,EG ,HF,之间互为等价隐含条件,所以分别等价。

重新命名为: a, b, e, h 3)列最小化状态表:N (t )/Z (t ) S (t )X=0 X=1a b/0 h/0b e/0 a/1 e a/0 h/0 h e/1 b/1试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:J1=K1=1;J2=Q1n⎯Q3n,K2=Q1nJ2=Q1n Q2n,K2=Q1n状态方程:Q1n+1=⎯Q1n·CP↓Q2n+1=[Q1n⎯Q3n⎯Q2n+⎯Q1n Q2n]·CP↓Q3n+1=[Q1n Q2n⎯Q3n+⎯Q1n Q3n]·CP↓状态转移表:序号Q3Q2Q10 1 2 3 4 5 000 001 010 011 100 101偏离状态110Æ111111Æ000状态转移图状态转移图:Q3Q2Q1偏离态能够进入有效循环,因此该电路具有自启动性。

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

数字电路与系统第六章时序逻辑电路(第5-6节)课堂笔记及练习题主题:第六章时序逻辑电路(第5-6节)学习时间: 2016年6月13日—6月19日内容:一、本周知识点及重难点分布表12-1 本周知识点要求掌握程度一览表二、知识点详解【知识点1】寄存器(1)定义:在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储1位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成。

(2)寄存器的分类(按功能分类):①基本寄存器:只能并行送入数据,需要时也只能并行输出②移位寄存器:移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

1、集成寄存器74LSl7574LS175的控制端功能:①RD是异步清零控制端。

②D0~D3是并行数据输入端。

③CP为时钟脉冲端。

④Q0~Q3是并行数据输出端。

表12-2 74LS175的功能表2、移位寄存器移位寄存器——不但可以寄存数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移动1位。

(1)单向移位寄存器1)右移寄存器(D 触发器组成的4位右移寄存器)右移寄存器的结构特点:左边触发器的输出端接右邻触发器的输入端。

QR C11D∧1DC1∧R Q1DC1∧R Q1DQ∧RC1Q 0Q 1Q 2Q 3CP CRI D 串行输入串行输出D 0D 1D 20FF 1FF 2FF 3FF 并 行 输 出D 3图12-1 D 触发器组成的四位右移寄存器设移位寄存器的初始状态为0000,串行输入数码D I =1101,从高位到低位依次输入。

其状态表如下:表12-3 右移寄存器状态表CP Q 0Q 1Q 21234567893Q I D 111图12-2右移寄存器的时序图在4个移位脉冲作用下,输入的4位串行数码1101全部存入了寄存器中。

第六章习题答案6.5解:对于74的TTL 电路,取V OH =3V ,V OL =0,V TH =1.3V ,R1=4k由于R 1+R S >>R ,则有:612ln 1.0210S OH TH OH THV V T RC V V --==⨯- 62ln0.3610S OH TH TH V V T RC V -+==⨯ 12110.72MHz f T T T ===+6.6解:石英晶体的多谐振器频率为f=1MHz74LS90为下降沿计数,并由电路可知,当QC=1,QB=1即110时,被异步清零。

波形如下:6.7解:T1=1ms ,T2=2mS波形如下:6.8补充两道555的题:6.9 用555定时器设计一个单稳态触发器。

要求输出脉冲宽度在1-10秒范围内手动可调。

给定555定时器的电源为15V,触发信号来自TTL电路,高低电平分别为3.4V和0.1V。

解:(1)若使图A6.27的单稳态电路正常工作,触发信号必须能将触发输入端电压(2端)拉到V T-以下,而在触发信号到来之前,2端电压应高于V T-。

由于V T-=5V,而触发脉冲最高电平仅为3.4V,所以需要在输入端加分压电阻,使2端电压在没有触发脉冲时略高于5V。

可取R1=22kΩ、R2 =18kΩ,经分压后2端电压为6.75V。

触发脉冲经微分电容C d加到2端。

(2)取C=100uF,为使T W=1~10秒,可求出R的阻值变化范围取100 kΩ的电位器与8.2 kΩ电阻串联作为R,即可得到T W=1~10秒的调节范围。

6.10 如图所示的由555定时器组成的多谐振荡器电路中,若R1=R2=5.1k,C=0.01uF,VCC=12V,计算电路的振荡频率解:。

第六章习题6-1 略。

6-2 此时相当于触发器在前级Q的上沿翻转,所以是减法计数器。

6-3 异步可逆计数器。

UP/DOWN=0时,加法计数;UP/DOWN=1时,减法计数6-4该电路为异步置位法任意模计数器,置位状态为4(M-1),所以该计数器的模M=5计数器;时序图略。

有效状态循环:0、1、2、3、7、0;4,6为过渡状态,其次态为7;5的次态为6。

由于由状态011(M-2)到100(M-1)时,Q1、Q0由1变0,所以这两个Q端上会出现毛刺。

6-5 用4位T’触发器;因用复位法,故用状态1010清0(R=Q3Q1)。

有效状态循环为0~9;10、11、14、15均为过渡状态,其次态均为0;12的次态是13,13的次态是14;毛刺出现在Q1上。

6-6用4位T’触发器;因用置位法,故用状态1001置位(S=Q3Q1Q0)。

有效状态循环为0~8,15;9、13为过渡状态,其次态均为15;10→11→12→13→15,14→15;无毛刺。

6-7用4位T’触发器;因用置位法,故用状态1101置位(S=Q3Q2Q1Q0)。

有效状态循环为0~12,15;13为过渡状态,其次态为15;14→15;毛刺出现在Q0上。

6-8~6-11 略。

6-12 电路由T触发器组成;CP i=CP,T0=1,T1=Q0,T2=Q1Q0,所以它是同步二进制减法计数器。

时序图略。

6-13 该题未要求是同步还是异步计数器,可以两种都做,也可以只做一种。

异步:先将JK转换为T’,即令J=K=1;同步:先将JK转换为T,即令J=K=T;M=8,需要3个触发器;异步可逆、同步可逆,参见图6.39;6-14 异步计数器电路简单,速度慢;同步计数器则相反。

6-15可能产生毛刺,也可能不产生。

如果产生毛刺,则它(们)出现在由M-2到M-1时由1变0的Q A、Q D端上和/或由M-2到M-1时由0变1的Q B、Q C端上。

6-16 先分别将‘290接为8421和5421计数器,再分别用M=7(Q D Q C Q B Q A =0111)8421和(Q A Q D Q C Q B=1010)5421复位即可,应特别注意高低位的顺序。